#opensourceasichighlight نتائج البحث

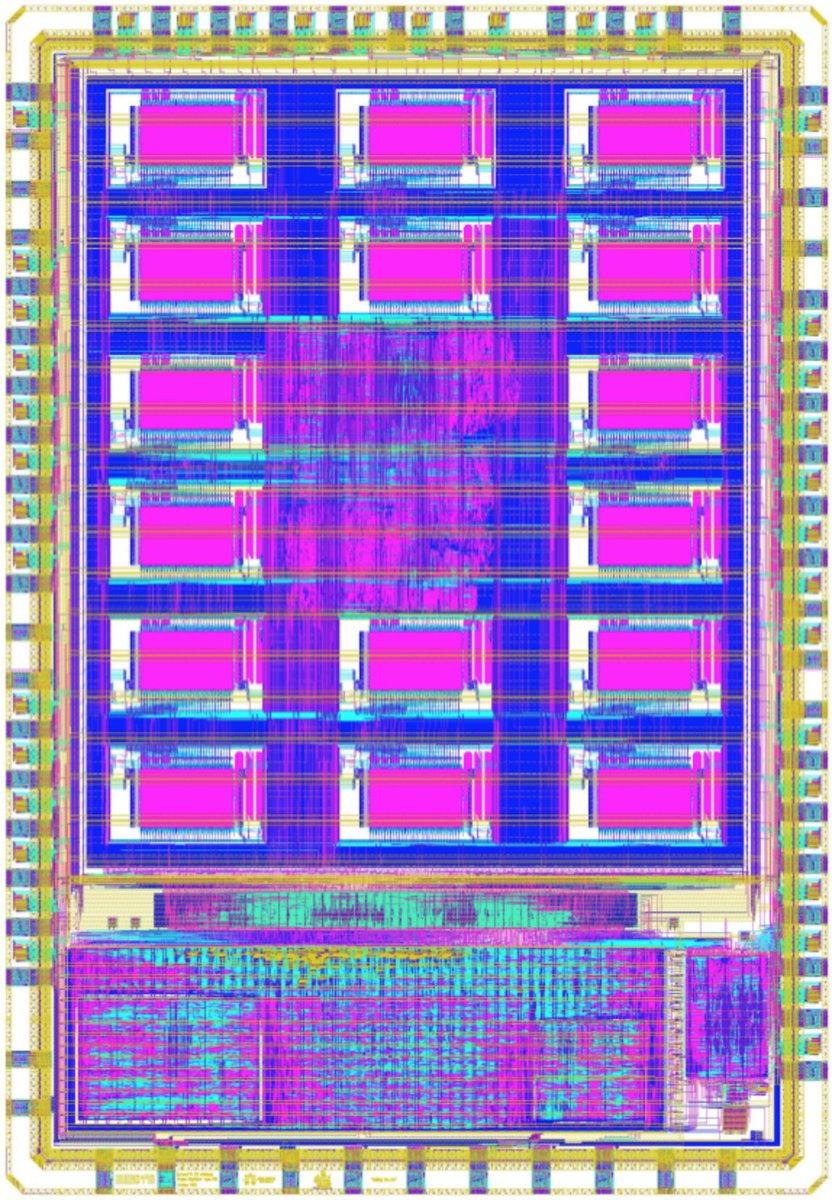

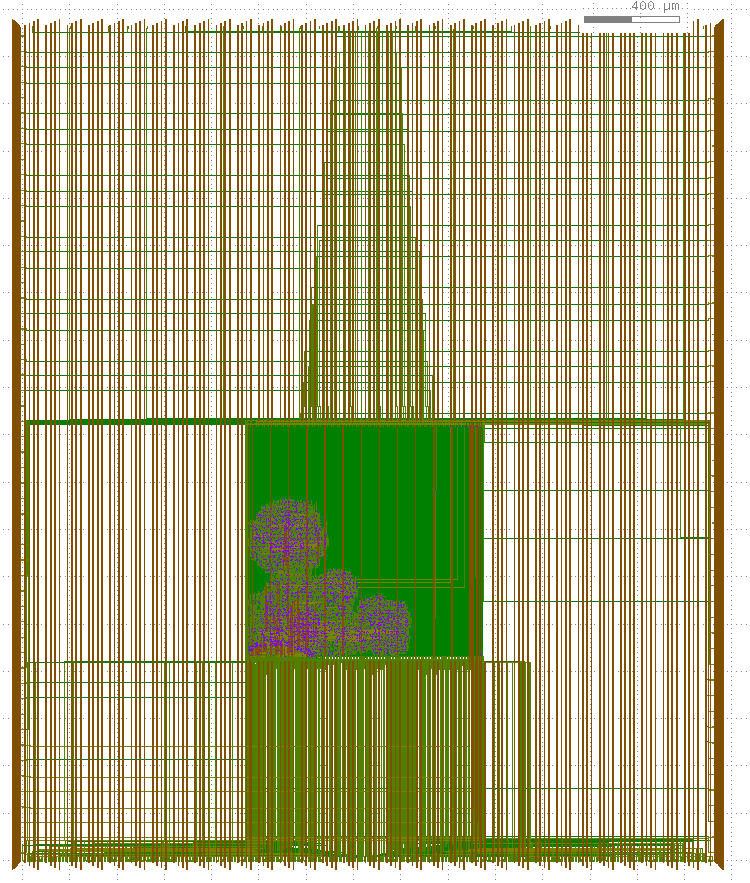

#OpenSourceASIChighlight Super Hitachi (SH)-2 CPU with 2-Stage Pipeline on MPW8. Shumpei Kawasaki submitted this processor based on patents that expired in 2014. This chip appears to have computational power w/a small footprint. #ASIC platform.efabless.com/projects/1542

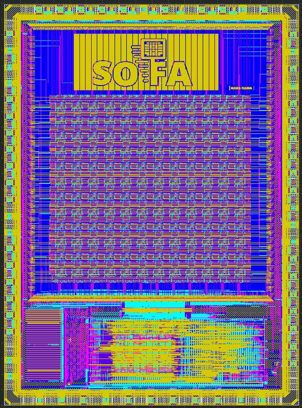

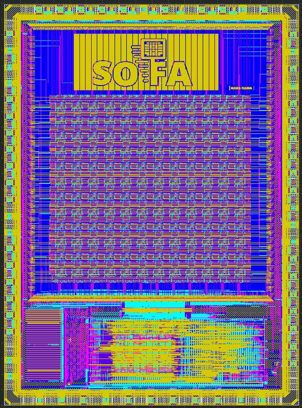

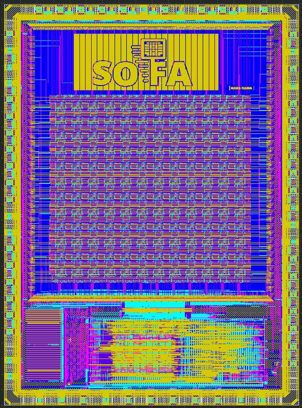

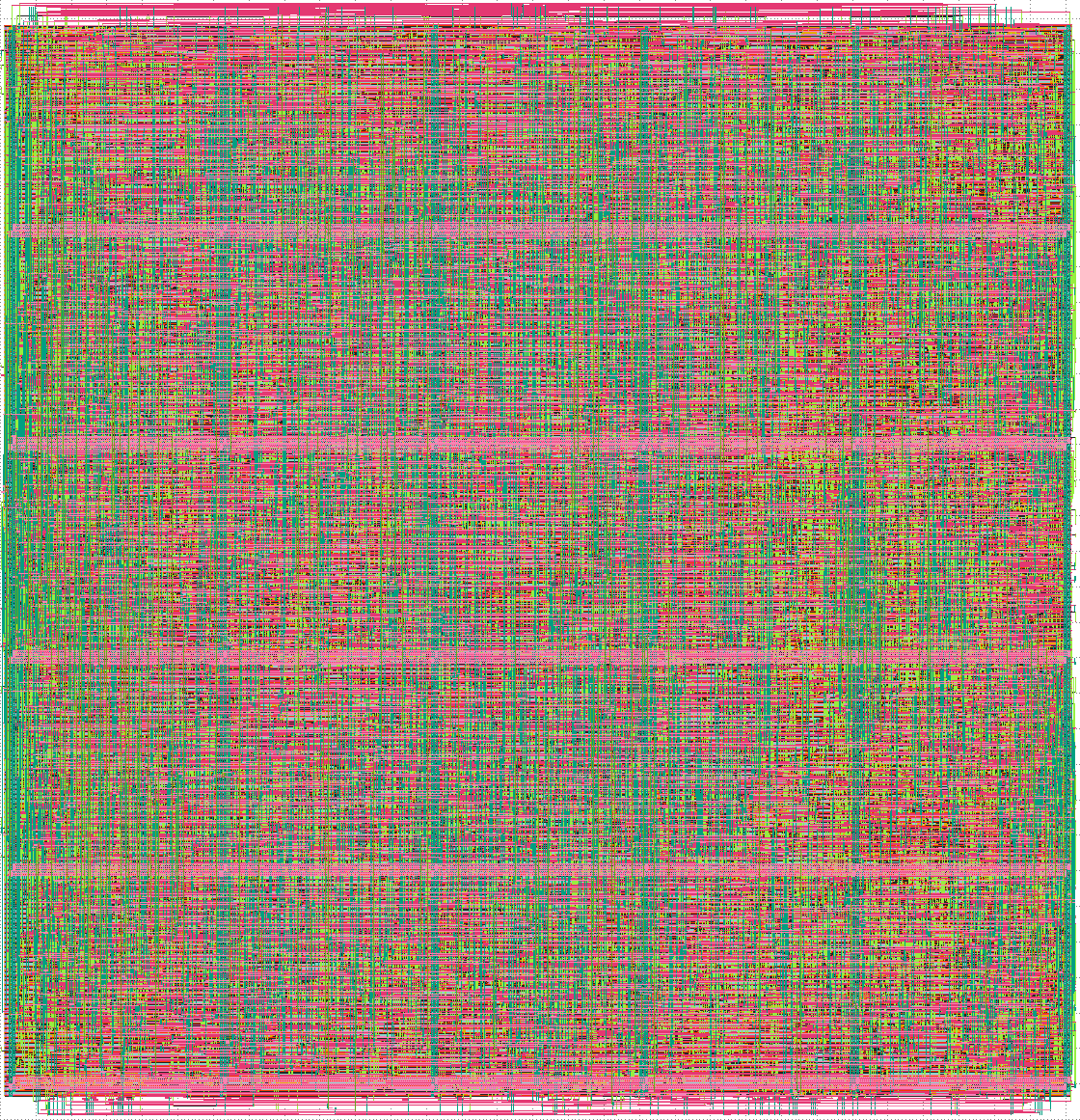

#OpenSourceASIChighlight SOFA (Skywater Opensource FPGAs) are open-source FPGA IPs using the open-source Skywater 130nm PDK and OpenFPGA, an open-source FPGA IP generator for highly-customizable FPGA architectures. #ASIC #UofU github.com/lnis-uofu/SOFA

#OpenSourceASIChighlight @jkulinz implemented a stereo delta-sigma audio DAC. The digital DS-modulator features a single-bit output, and thus two digital GPIO (per channel) as outputs. The design was designed for #Skywater130 and submitted to @Efabless MPW5.

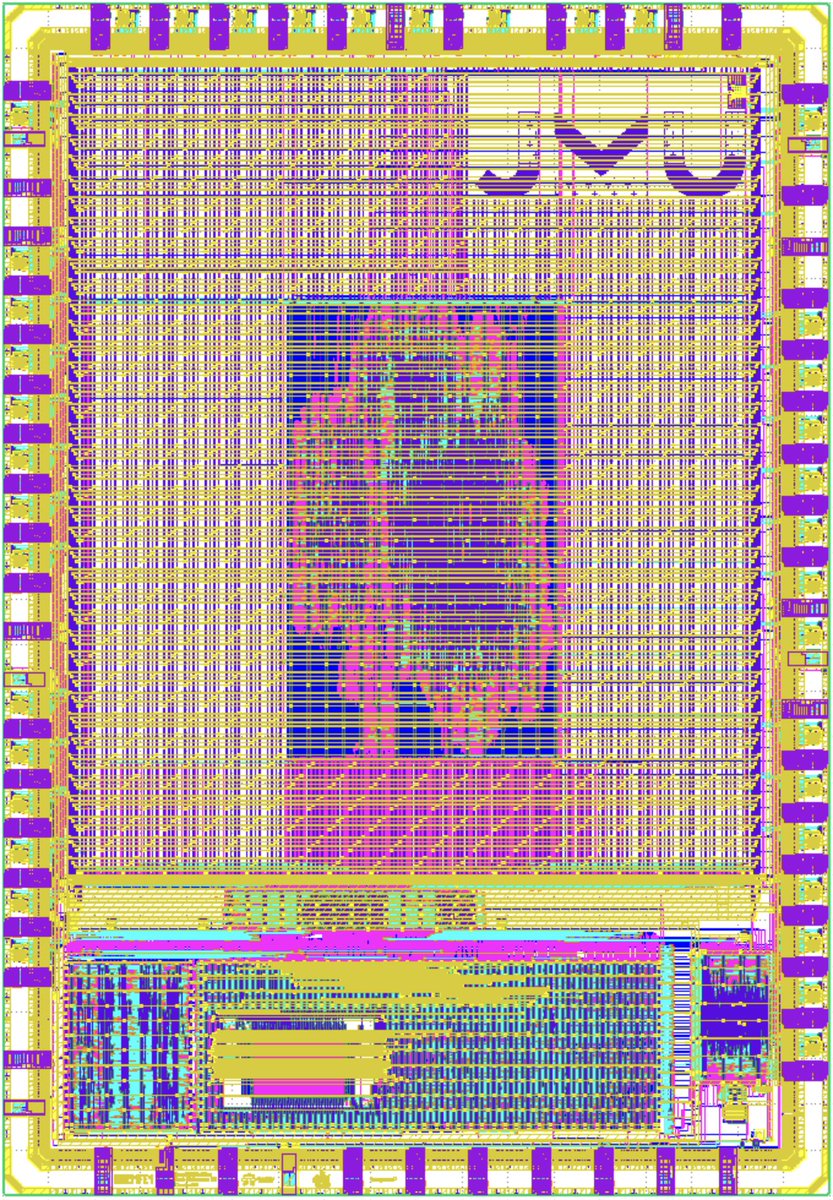

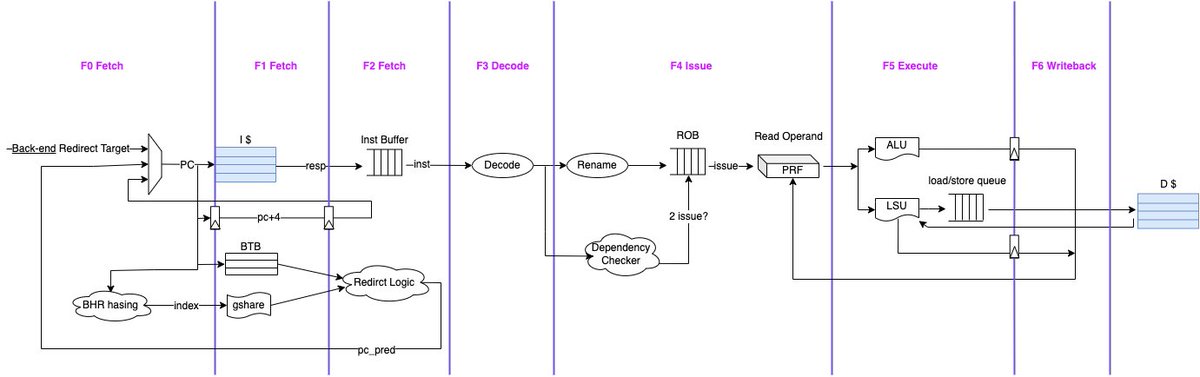

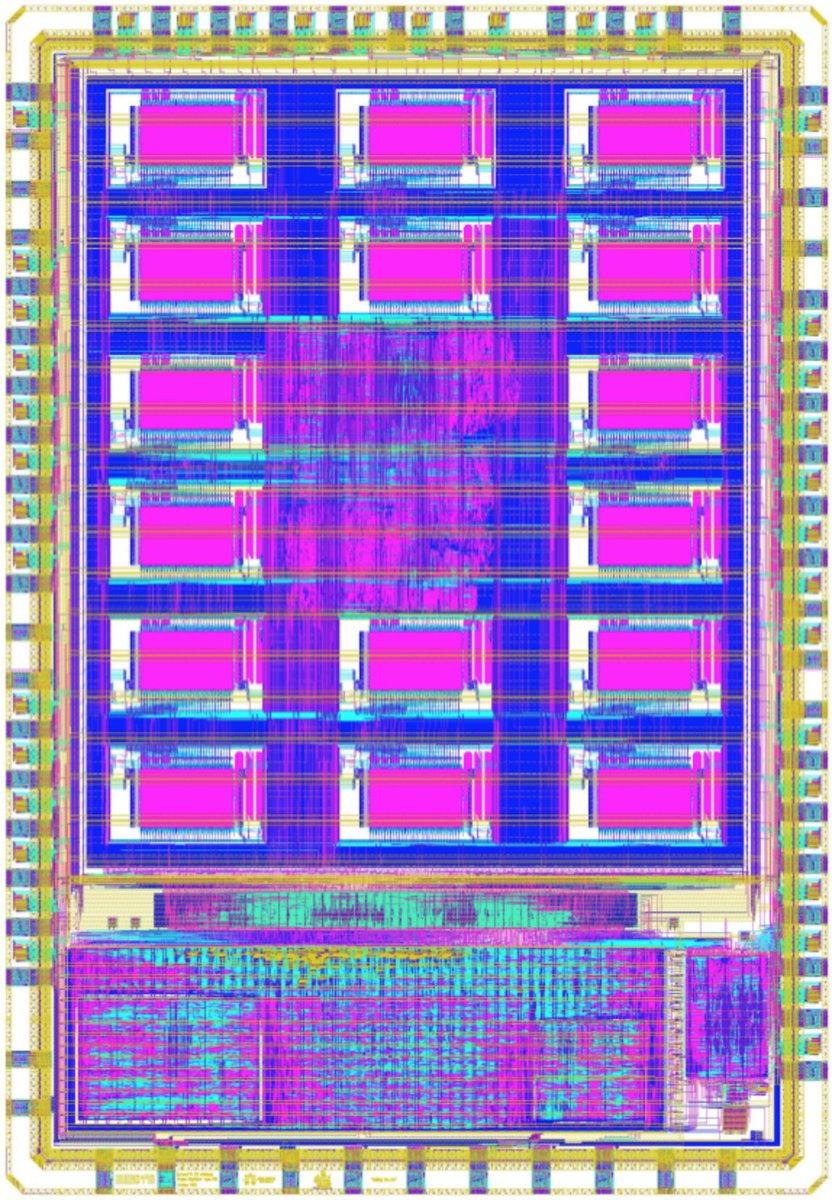

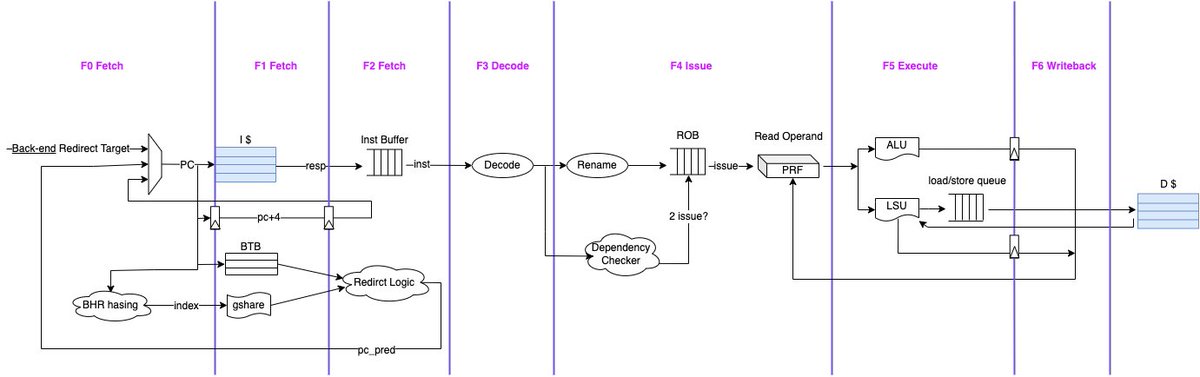

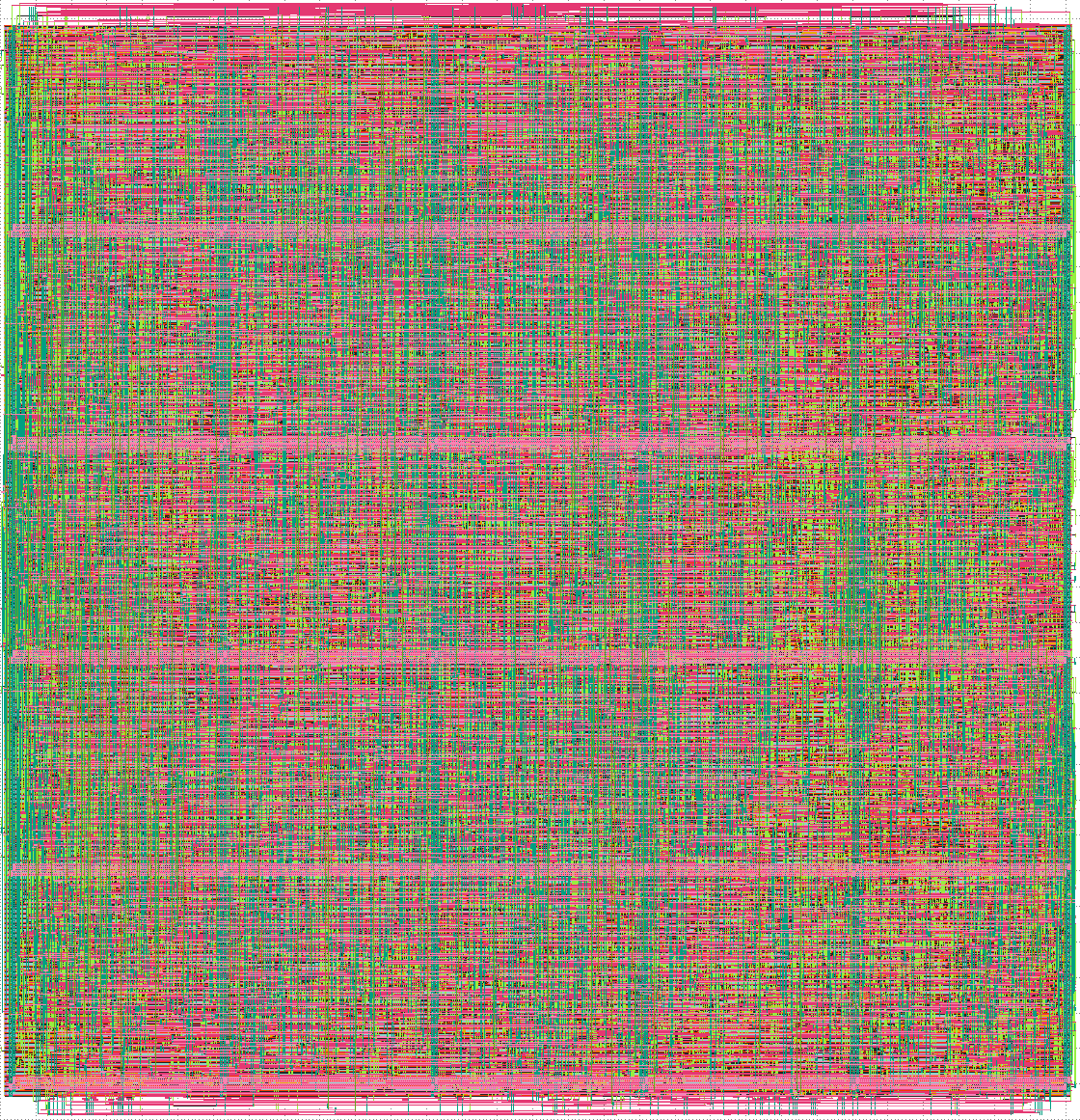

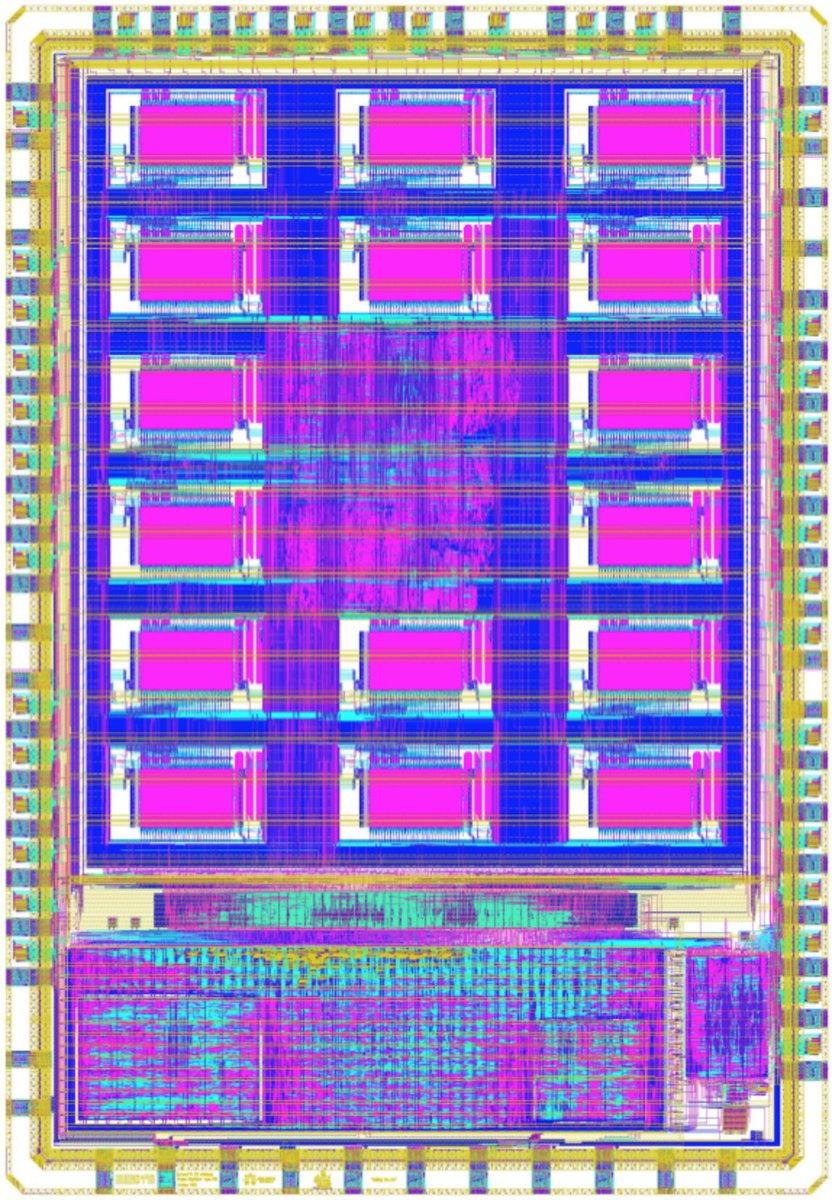

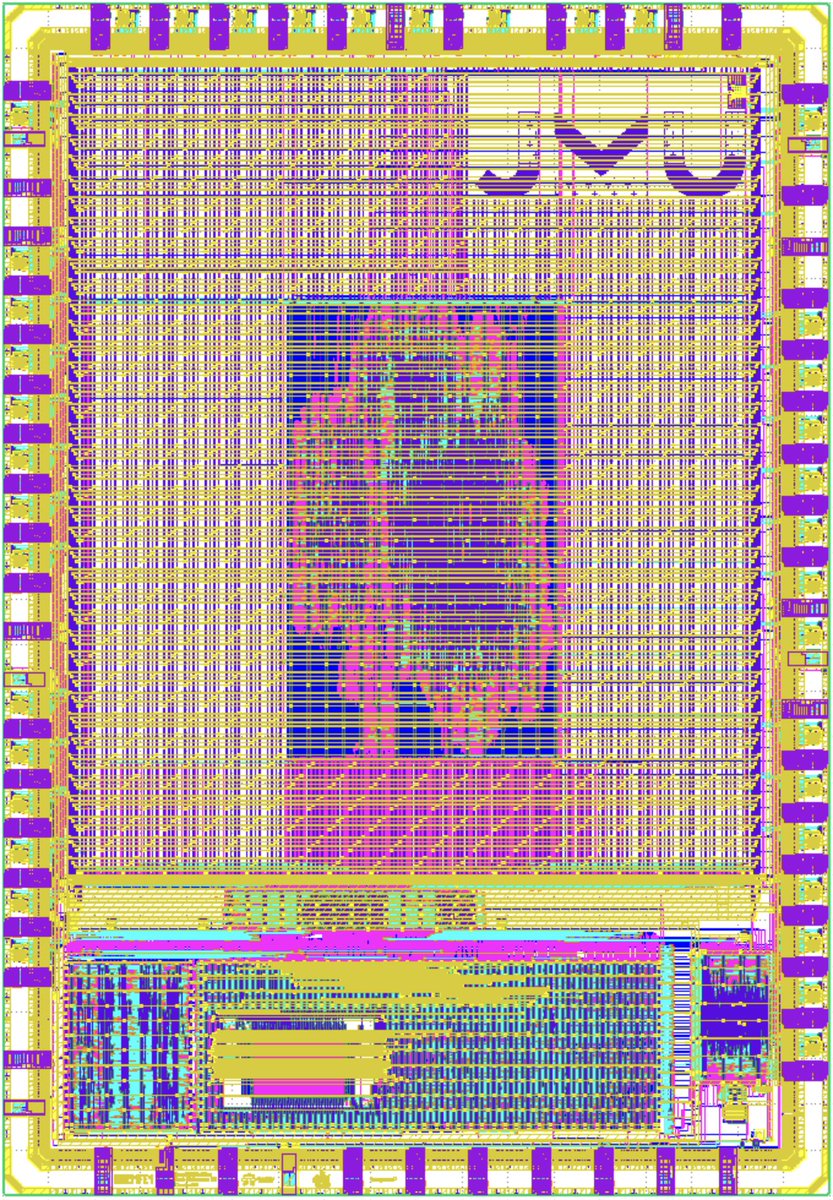

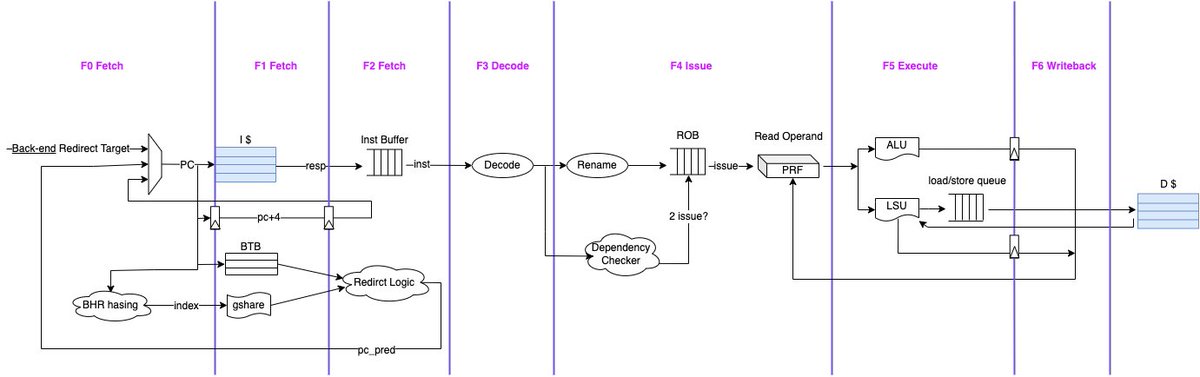

#OpenSourceASIChighlight HEHECore by the RIOS Lab (rioslab.org) is a 64-bit, dual-issue, out-of-order RISC-V processor designed in Verilog. The creators seek to lower the threshold for CPU design using #opensource tools. Great work! github.com/b224hisl/riosc…

Wednesday's #OpenSourceASIChighlight! VLSIFFRA for creating fast and efficient standard cell-based adders and multipliers by @antonblanchard of @IBM. The designs are fast, configurable and verified using @YosysHQ. The same algorithms were used in the Bluegene Q supercomputer!

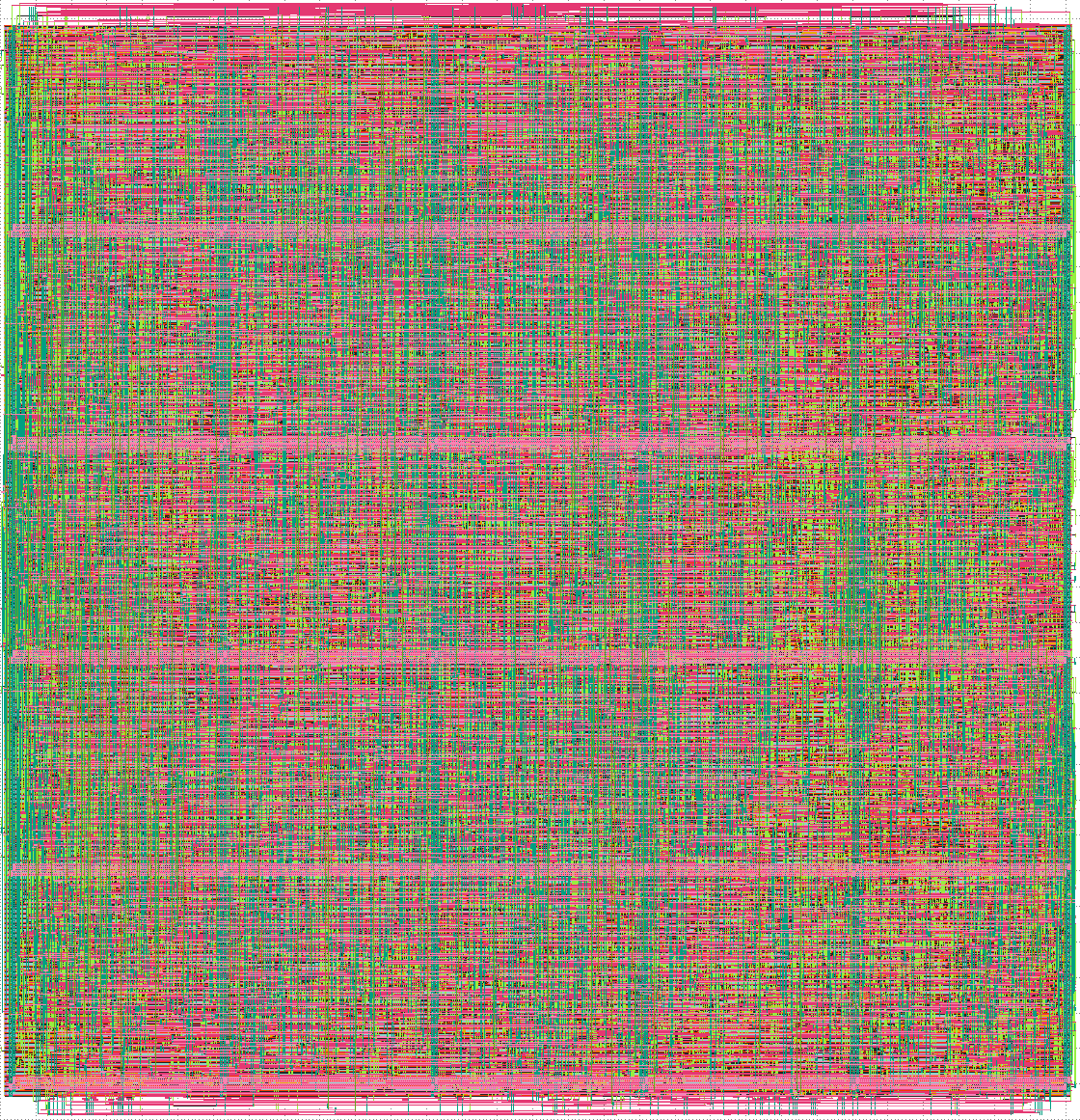

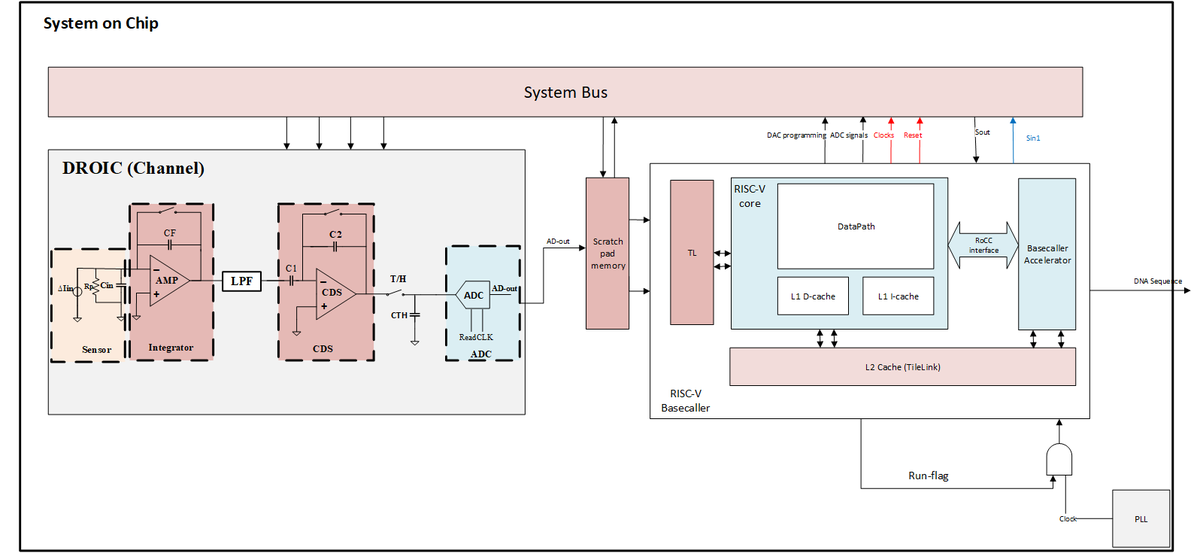

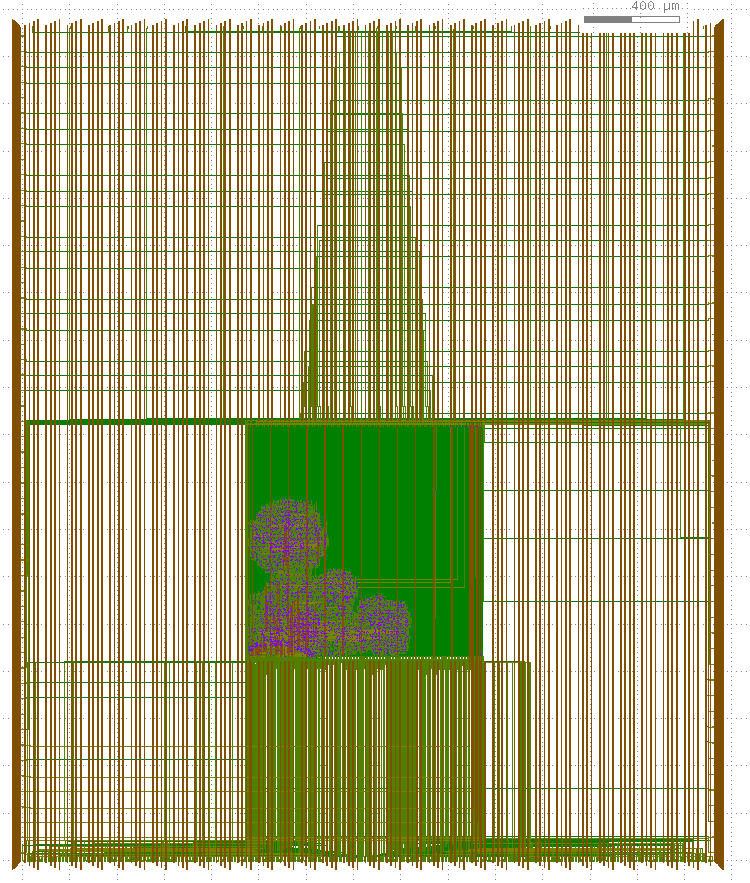

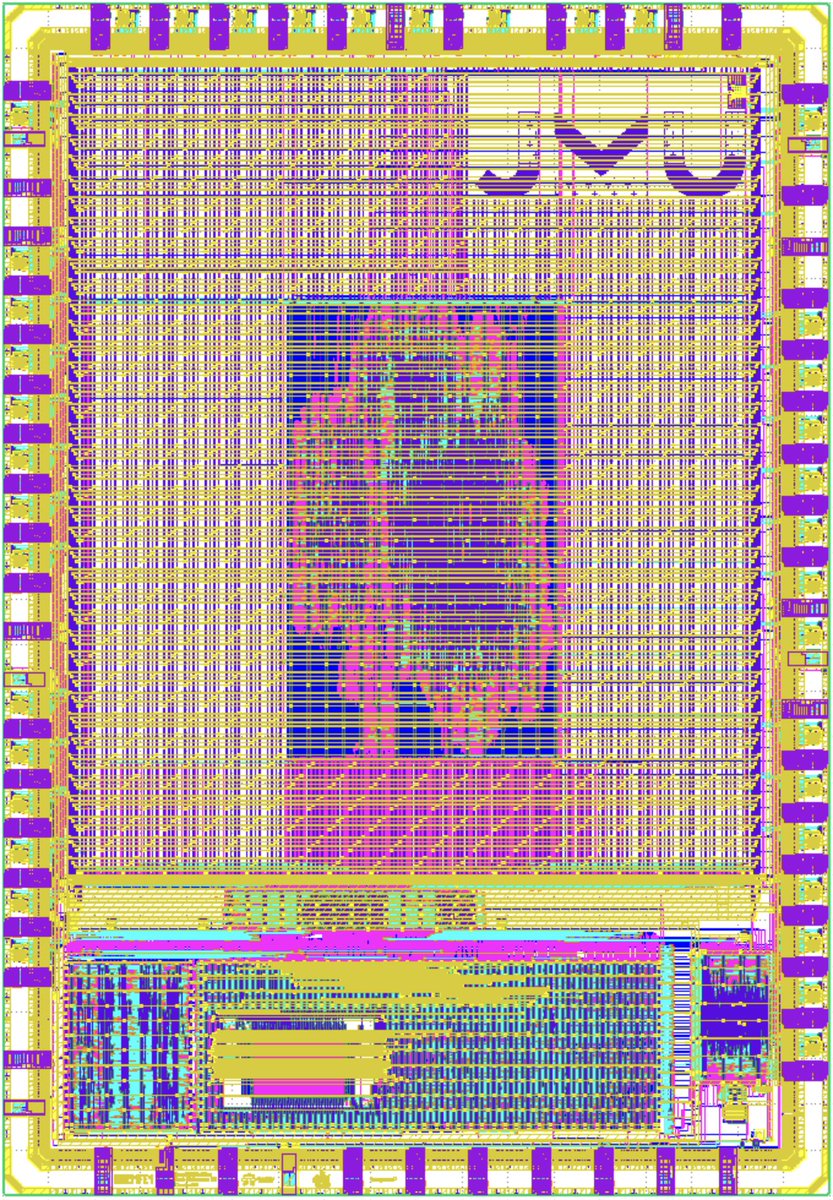

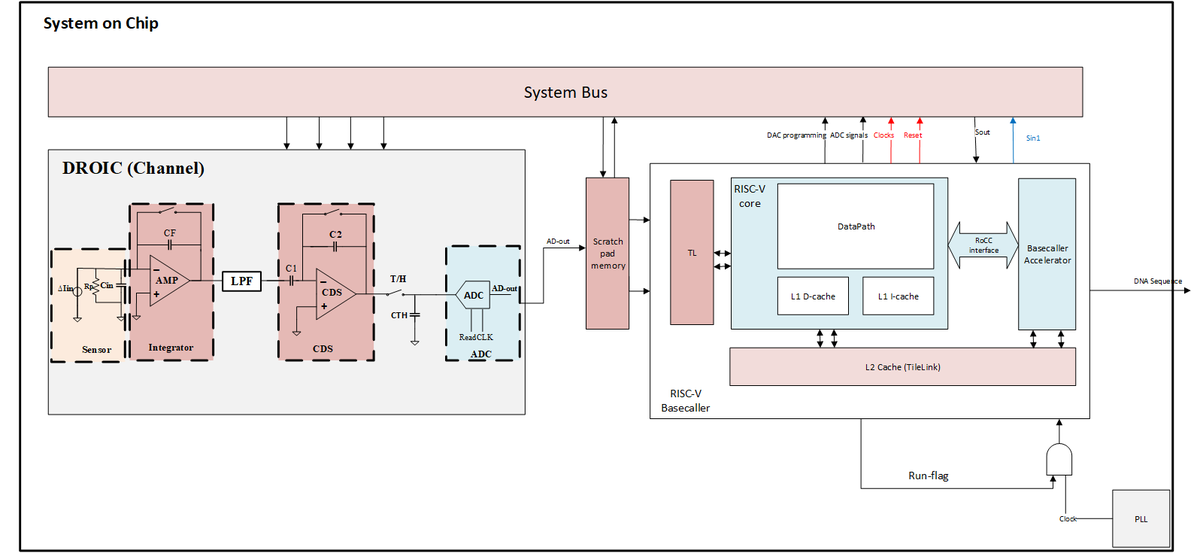

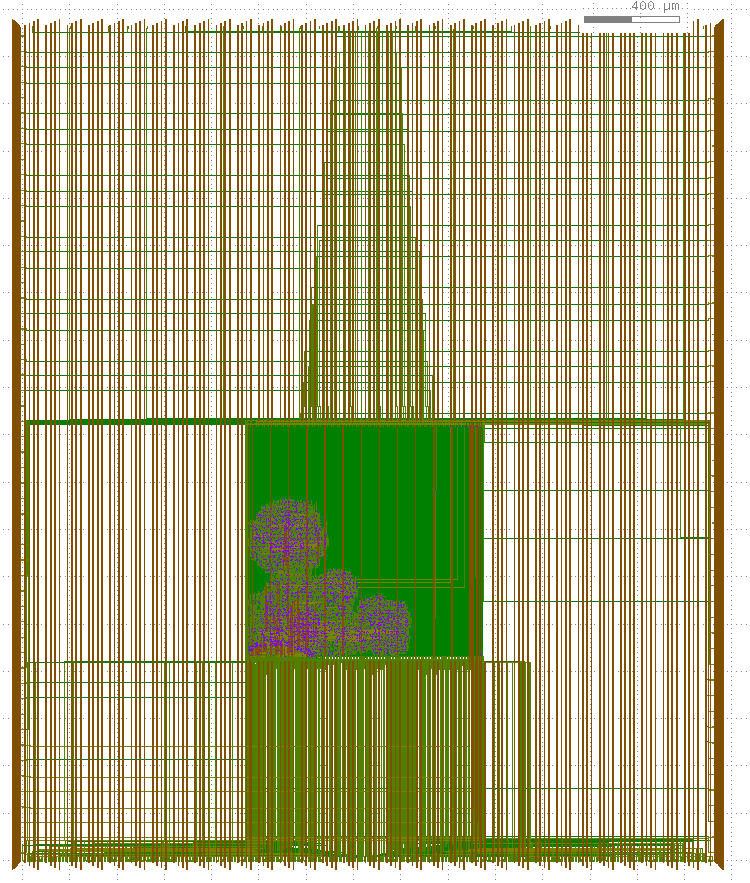

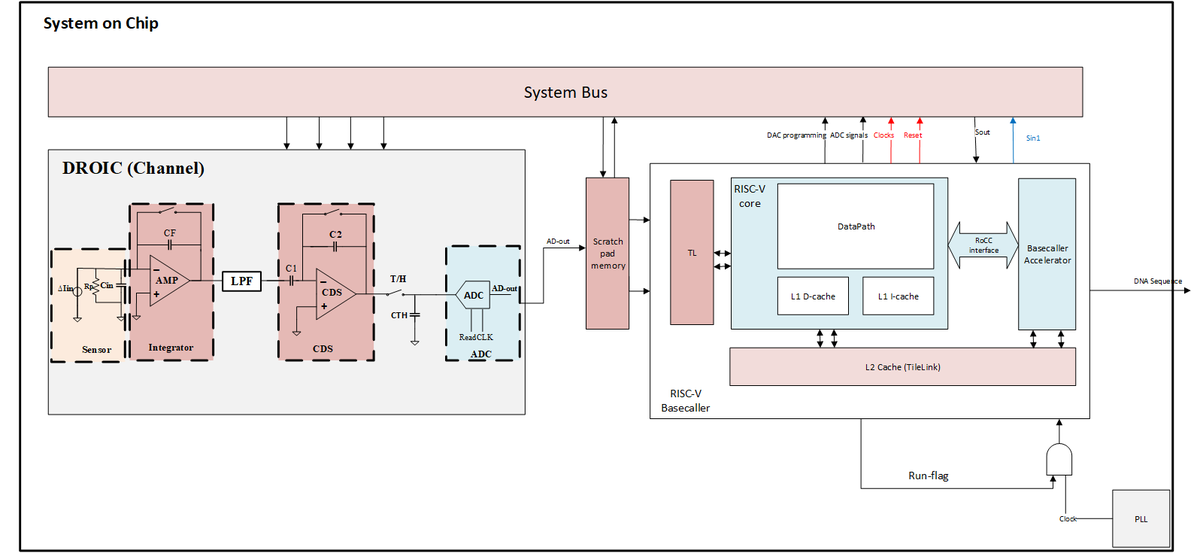

#OpenSourceASIChighlight: MPW8 mixed-signal submission on low-power / scalable SoC for 3rd gen nanopore-based DNA sequencing from York Univ, testing the digital readout and bioinfo processing units to measure pico-amp scale currents. #ASIC github.com/EMIL-YORKU/Sen…

#OpenSourceASIChighlight “Subservient” design from @sekreterar implementing an ASIC-adapted version of the award-winning bit-serial RISC-V processor SERV on @Efabless MPW2. Klas just received his chips - can’t wait to see how the design turns out! linkedin.com/posts/klas-nor…

#OpenSourceASIChighlight On the first #GF180 tapeout (!) there’s a xmas tree controller by Julien Oury with an IR receiver, stepper motor controller, LED string controller and pseudo-random generator. github.com/JulienOury/Chr… #ASIC #engineering

#OpenSourceASIChighlight @danrr_au made an #ASIC graphics generator on MPW1. Called VDP-Lite, it runs using the PicoRV32 + WB interface of the Caravel SoC. The sprite generator is a minimized variant from Dan’s opensource FPGA gaming platform. platform.efabless.com/projects/1

RT @matthewvenn@chaos.social #OpenSourceASIChighlight SOFA (Skywater Opensource FPGAs) are open-source FPGA IPs using the open-source Skywater 130nm PDK and OpenFPGA, an open-source FPGA IP generator for highly-customizable FPGA architectures. #ASIC (1/2)

RT @matthewvenn@chaos.social #OpenSourceASIChighlight Johannes Kepler Universität implemented a stereo delta-sigma audio DAC. The digital DS-modulator features a single-bit output, and thus two digital GPIO (per channel) as outputs. The design was designed for (1/2)

#OpenSourceASIChighlight “Subservient” design from @sekreterar implementing an ASIC-adapted version of the award-winning bit-serial RISC-V processor SERV on @Efabless MPW2. Klas just received his chips - can’t wait to see how the design turns out! linkedin.com/posts/klas-nor…

RT @matthewvenn@chaos.social #OpenSourceASIChighlight Johannes Kepler Universität implemented a stereo delta-sigma audio DAC. The digital DS-modulator features a single-bit output, and thus two digital GPIO (per channel) as outputs. The design was designed for (1/2)

#OpenSourceASIChighlight @jkulinz implemented a stereo delta-sigma audio DAC. The digital DS-modulator features a single-bit output, and thus two digital GPIO (per channel) as outputs. The design was designed for #Skywater130 and submitted to @Efabless MPW5.

#OpenSourceASIChighlight @danrr_au made an #ASIC graphics generator on MPW1. Called VDP-Lite, it runs using the PicoRV32 + WB interface of the Caravel SoC. The sprite generator is a minimized variant from Dan’s opensource FPGA gaming platform. platform.efabless.com/projects/1

#OpenSourceASIChighlight On the first #GF180 tapeout (!) there’s a xmas tree controller by Julien Oury with an IR receiver, stepper motor controller, LED string controller and pseudo-random generator. github.com/JulienOury/Chr… #ASIC #engineering

RT @matthewvenn@chaos.social #OpenSourceASIChighlight SOFA (Skywater Opensource FPGAs) are open-source FPGA IPs using the open-source Skywater 130nm PDK and OpenFPGA, an open-source FPGA IP generator for highly-customizable FPGA architectures. #ASIC (1/2)

#OpenSourceASIChighlight SOFA (Skywater Opensource FPGAs) are open-source FPGA IPs using the open-source Skywater 130nm PDK and OpenFPGA, an open-source FPGA IP generator for highly-customizable FPGA architectures. #ASIC #UofU github.com/lnis-uofu/SOFA

#OpenSourceASIChighlight Super Hitachi (SH)-2 CPU with 2-Stage Pipeline on MPW8. Shumpei Kawasaki submitted this processor based on patents that expired in 2014. This chip appears to have computational power w/a small footprint. #ASIC platform.efabless.com/projects/1542

#OpenSourceASIChighlight: MPW8 mixed-signal submission on low-power / scalable SoC for 3rd gen nanopore-based DNA sequencing from York Univ, testing the digital readout and bioinfo processing units to measure pico-amp scale currents. #ASIC github.com/EMIL-YORKU/Sen…

#OpenSourceASIChighlight HEHECore by the RIOS Lab (rioslab.org) is a 64-bit, dual-issue, out-of-order RISC-V processor designed in Verilog. The creators seek to lower the threshold for CPU design using #opensource tools. Great work! github.com/b224hisl/riosc…

Wednesday's #OpenSourceASIChighlight! VLSIFFRA for creating fast and efficient standard cell-based adders and multipliers by @antonblanchard of @IBM. The designs are fast, configurable and verified using @YosysHQ. The same algorithms were used in the Bluegene Q supercomputer!

#OpenSourceASIChighlight Super Hitachi (SH)-2 CPU with 2-Stage Pipeline on MPW8. Shumpei Kawasaki submitted this processor based on patents that expired in 2014. This chip appears to have computational power w/a small footprint. #ASIC platform.efabless.com/projects/1542

#OpenSourceASIChighlight SOFA (Skywater Opensource FPGAs) are open-source FPGA IPs using the open-source Skywater 130nm PDK and OpenFPGA, an open-source FPGA IP generator for highly-customizable FPGA architectures. #ASIC #UofU github.com/lnis-uofu/SOFA

Wednesday's #OpenSourceASIChighlight! VLSIFFRA for creating fast and efficient standard cell-based adders and multipliers by @antonblanchard of @IBM. The designs are fast, configurable and verified using @YosysHQ. The same algorithms were used in the Bluegene Q supercomputer!

#OpenSourceASIChighlight @jkulinz implemented a stereo delta-sigma audio DAC. The digital DS-modulator features a single-bit output, and thus two digital GPIO (per channel) as outputs. The design was designed for #Skywater130 and submitted to @Efabless MPW5.

#OpenSourceASIChighlight HEHECore by the RIOS Lab (rioslab.org) is a 64-bit, dual-issue, out-of-order RISC-V processor designed in Verilog. The creators seek to lower the threshold for CPU design using #opensource tools. Great work! github.com/b224hisl/riosc…

#OpenSourceASIChighlight On the first #GF180 tapeout (!) there’s a xmas tree controller by Julien Oury with an IR receiver, stepper motor controller, LED string controller and pseudo-random generator. github.com/JulienOury/Chr… #ASIC #engineering

#OpenSourceASIChighlight: MPW8 mixed-signal submission on low-power / scalable SoC for 3rd gen nanopore-based DNA sequencing from York Univ, testing the digital readout and bioinfo processing units to measure pico-amp scale currents. #ASIC github.com/EMIL-YORKU/Sen…

#OpenSourceASIChighlight “Subservient” design from @sekreterar implementing an ASIC-adapted version of the award-winning bit-serial RISC-V processor SERV on @Efabless MPW2. Klas just received his chips - can’t wait to see how the design turns out! linkedin.com/posts/klas-nor…

Something went wrong.

Something went wrong.

United States Trends

- 1. Kanata 17.1K posts

- 2. The BIGGЕST JUP AlRDROP 23.6K posts

- 3. #GMMTVxTPDA2025 35K posts

- 4. Lakers 49.4K posts

- 5. Dillon Brooks 7,407 posts

- 6. Hololive 14.1K posts

- 7. Bron 25.3K posts

- 8. Giants 86.5K posts

- 9. Patriots 134K posts

- 10. Dart 36.8K posts

- 11. #WWERaw 73.1K posts

- 12. #AvatarFireAndAsh 3,267 posts

- 13. Collin Gillespie 2,116 posts

- 14. Suns 19.6K posts

- 15. STEAK 10.5K posts

- 16. Drake Maye 24.7K posts

- 17. James Cameron 4,958 posts

- 18. Devin Williams 7,853 posts

- 19. Pats 16.2K posts

- 20. Diaz 33.7K posts