#riscv search results

Green screen #DOOM ! This was my favourite bug we found running DOOM on the @Tenstorrent Ascalon #RISCV CPU in pre silicon testing. We initially thought it was a chip RTL issue, but it turned out to be both a gcc bug gcc.gnu.org/bugzilla/show_… and a QEMU bug lists.nongnu.org/archive/html/q…

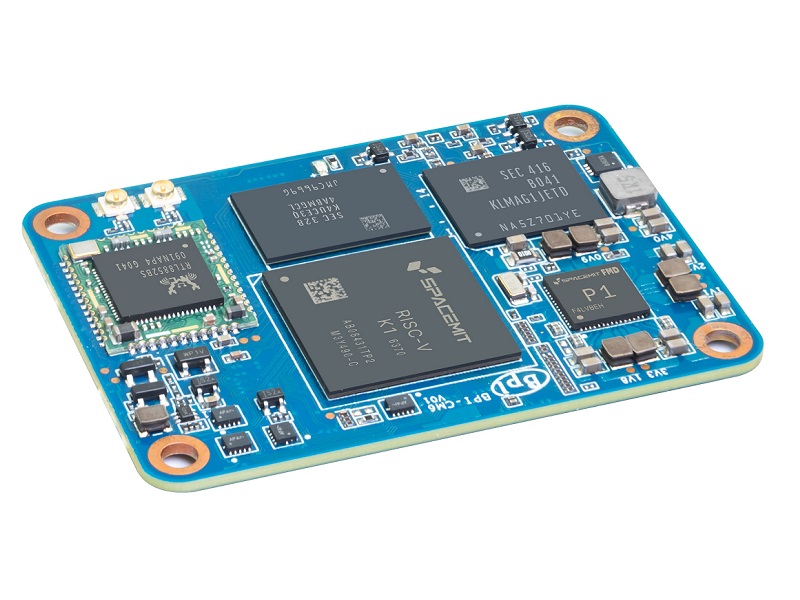

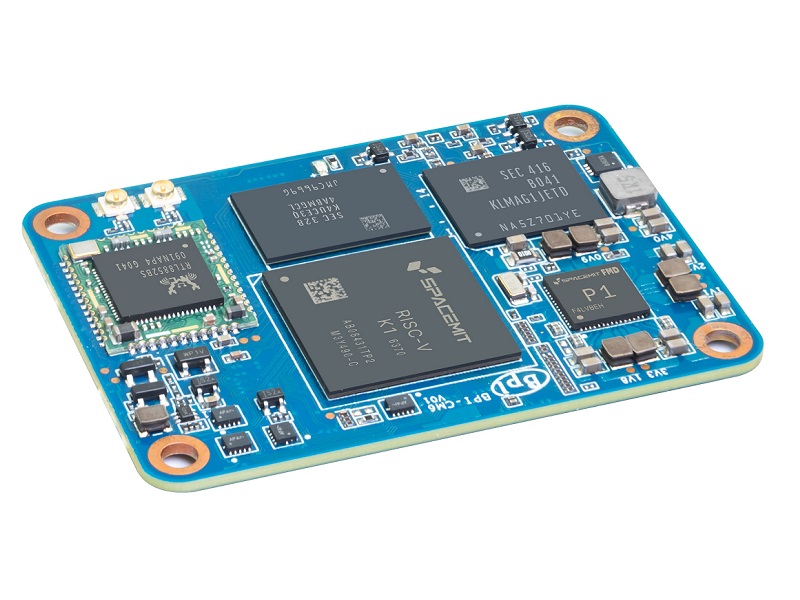

Banana Pi BPI-CM6 design with SpacemiT K1 8 core RISC-V chip, CPU integrates 2.0 TOPs AI computing power. 8/16G DDR and 8/16/32/128G eMMC. support DeepX AI. will comming soon. docs.banana-pi.org/en/BPI-CM6/Ban… #riscv #EdgeComputing #bananapi #raspberrypi

If you're writing assembler, I heartily recommend Compiler Explorer. I wrote about this from a RISC-V perspective a while back. #asm #riscv projectf.io/posts/riscv-co…

XMRIG ON #RISCV! I dare say, at this point, I run the smollest #Monero miner at 22.86x35.56mm! Powered directly on the PCB so the USB-C port is available for flash storage to act as swap (4-5x faster than the micro SD card). I used @MoneroOcean for testing

At Embedded World, Mark Throndson spoke on “Networking Native RISC-V Processor for the Datacenter,” discussing several optimizations that can be achieved within a standard #RISCV solution that tailor the implementation to networking. He highlighted the multi-threaded,…

At #RISCVSummit North America 2025, DeepComputing Founder & CEO @Yuning_XC5 will share how we’re bringing intelligent media experiences to life on RISC-V AI SoCs. Join us to explore how RISC-V is redefining the way AI applications run at the edge and beyond. #RISCV…

Oh yeah finally got the #milkv duo (256mb). Even came with a very useful SMD ruler (I needed one of those anyway). The #riscv adventures are going to be fun!!

MIPS' Sean Murphy took the stage at Embedded World, sharing how MIPS is creating #RISCV custom instructions to accelerate real-rime applications. He unveiled a novel solution for accelerating real-time motor control algorithms using a MIPS defined trigonometric math custom…

Excited to bring @DeepComputingio + @risc_v + @FrameworkPuter to @FOSS_for_All — sharing the power of open computing with the community! #RISCV #Opensource

I've just run into the image below. It seems to somehow formally describe RV32I ISA. What language is this and what is it used for? #RISCV

Last day at @MakerFaireRome 2025 🇮🇹 Showed the RISC-V in action with @DeepComputingio DC-ROMA RISC-V AI PC inside the @FrameworkPuter Laptop. Excited to keep spreading the word about #RISCV #OpenSource, and #OpenHardware in Rome!

Banana Pi BPI-RV2 Risc-V gateway board Siflower SF21H8898 bpi-shop.com/products/banan… #riscv #openwrt #bananapi #gateway #network

Great talk by Jing Yang from XuanTie at @risc_v #Summit. The C930, providing RVA23, sounds very exciting. XuanTie cores have been crucial for #hpc in #riscv and in @EPCCed benchmarking has helped understand where the ecosystem is for #hpc and future opportunities

Come see us at the Summit, just a week away. We've got some exciting demos and our team will be there to answer questions. #riscv.

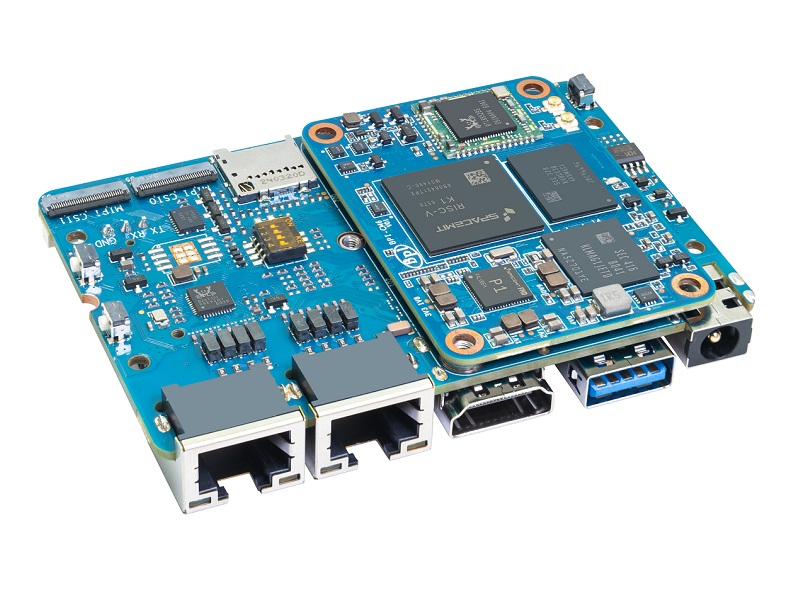

Banana Pi BPI-F3 SBC , 8 Core RISC-V SpacemiT K1, 2Tops of Fused Performance for Versatile Computing,2/4/8/16G RAM and 8-128G eMMC docs.banana-pi.org/en/BPI-F3/Bana… #riscv #SBC #opensource #AI #AIoT #NAS #robotics #edgecomputing

The dev zone at #RISCVSummit was crammed full of interesting things and very popular this week, here I chat to Austin @risc_v about the #HPC #RISCV demo we had brought from @EPCCed . Thanks to Carl for providing the hardware and installing things!

The future of intelligent media is open — and RISC-V is stepping into that future. At @VideoLan Developer Days, @Yuning_XC5 will show VLC running with STT and T2T on our 40-TOPS RISC-V laptop. Come see RISC-V in action. The open media era starts here. #RISCV #VLC #OpenHardware

Do you want to see the KianV SoC running Linux kernel 2.6.17-rc6 today?

36 vote · Final results

XMRIG ON #RISCV! I dare say, at this point, I run the smollest #Monero miner at 22.86x35.56mm! Powered directly on the PCB so the USB-C port is available for flash storage to act as swap (4-5x faster than the micro SD card). I used @MoneroOcean for testing

Firmy #LAUTERBACH i @tenstorrent ogłaszają strategiczną współpracę nad rozwojem motoryzacyjnych układów #RISCV SoC, które wyznaczą nowy standard w branży! To połączenie mocy, elastyczności i innowacji – idealne dla ery #SDV. 👉 tiny.pl/xx-3y6fz #embedded #automotive #SoC

Just finished writing a bare-metal #RISCV SG90 servo motor driver with an ESP32-C3 entirely in Assembler. I will be releasing it soon for others to learn from and expand their Embedded #ReverseEngineering skills for this incredible open-source platform.

Excited to bring @DeepComputingio + @risc_v + @FrameworkPuter to @FOSS_for_All — sharing the power of open computing with the community! #RISCV #Opensource

New episode of the AI Master Podcast is out! 🎧 Guest: Christian Stenzel, Director of Sales EMEA at @tenstorrent We talk about open AI hardware, RISC-V, chiplets, and the future of silicon. Listen on your favorite platform! #AIMasterPodcast #AI #RISCv #Tenstorrent #OpenHardware

C107は落ちましたので例によって@tceoo1さんの所に 委託の予定です。 新作は以下の2点+αのとなる予定です。 ・DTMFデコーダIC 改 ・低ピン数スイッチマトリクス読取回路基板(仮) with RISC-V命令デコード表示ファームウェア (・拙作の技術解説ペーパーorコピー本) #C107 #riscv

Compiler Explorer is a great way to understand the effect of #riscv extensions or compare CPU arch. You can even compare rv32 and armv7 to a 486. 🤔 For example, an endian swap takes 11 instructions with the base RISC-V ISA, but only 1 instruction (rev8) with the Zbb extension.

If you're writing assembler, I heartily recommend Compiler Explorer. I wrote about this from a RISC-V perspective a while back. #asm #riscv projectf.io/posts/riscv-co…

📢 RISC-V Open Hours 🗓️ Thu, Nov 13, 11:00 AM – 12:00 PM (GMT+8) 🔗 Event: community.riscv.org/events/details… ✨ Community forum beyond mailing lists ✨ Focus on RISC-V in open source projects & dev boards ✨ Updates, tech topics & new ecosystem highlights 🚀 #RISCV #RVOH @risc_v

Green screen #DOOM ! This was my favourite bug we found running DOOM on the @Tenstorrent Ascalon #RISCV CPU in pre silicon testing. We initially thought it was a chip RTL issue, but it turned out to be both a gcc bug gcc.gnu.org/bugzilla/show_… and a QEMU bug lists.nongnu.org/archive/html/q…

At Embedded World, Mark Throndson spoke on “Networking Native RISC-V Processor for the Datacenter,” discussing several optimizations that can be achieved within a standard #RISCV solution that tailor the implementation to networking. He highlighted the multi-threaded,…

📄A Performance Analysis of Autovectorization on RVV RISC-V Boards Lorenzo Carpentieri, Mohammad Vazirpanah, Biagio Cosenza Euromicro International Conference on Parallel, Distributed and Network-based Processing (𝐏𝐃𝐏), 2025 #RISCV

Thanks @risc_v for the invite to give a keynote at #RISCVSummit a couple of weeks ago. We have seen great progress in #RISCV for #HPC, and given promises by vendors and progress in the sw ecosystem I predict that 2026 could be a watershed year. youtu.be/ItA-NS4vxsU?si…

youtube.com

YouTube

Keynote: Reimagining the Future of High Performance Computing...

💡 Every AtlasChip carries a blockchain identity — making technology transparent, traceable, and trustworthy. Investment link 👇 sidrastart.com/project/3f4e7b… #AtlasChipWeb3 #RISCv #SmartTech #HalalFinance

How to setup an OpenBSD RISCV64 Virtual Machine in QEMU - Post by Hiltjo Posthuma #OpenBSD #RiscV codemadness.org/openbsd-riscv6…

MIPS' Sean Murphy took the stage at Embedded World, sharing how MIPS is creating #RISCV custom instructions to accelerate real-rime applications. He unveiled a novel solution for accelerating real-time motor control algorithms using a MIPS defined trigonometric math custom…

Banana Pi BPI-CM6 design with SpacemiT K1 8 core RISC-V chip, CPU integrates 2.0 TOPs AI computing power. 8/16G DDR and 8/16/32/128G eMMC. support DeepX AI. will comming soon. docs.banana-pi.org/en/BPI-CM6/Ban… #riscv #EdgeComputing #bananapi #raspberrypi

Machines build machines - AI creates a bootable VM: popovicu.com/posts/ai-creat… I successfully managed to build a bootable #RISCV VM almost entirely with #AI. It boots #OpenSBI, paving the way to boot #Linux. How far can we push the AI? #FPGA implementation next?

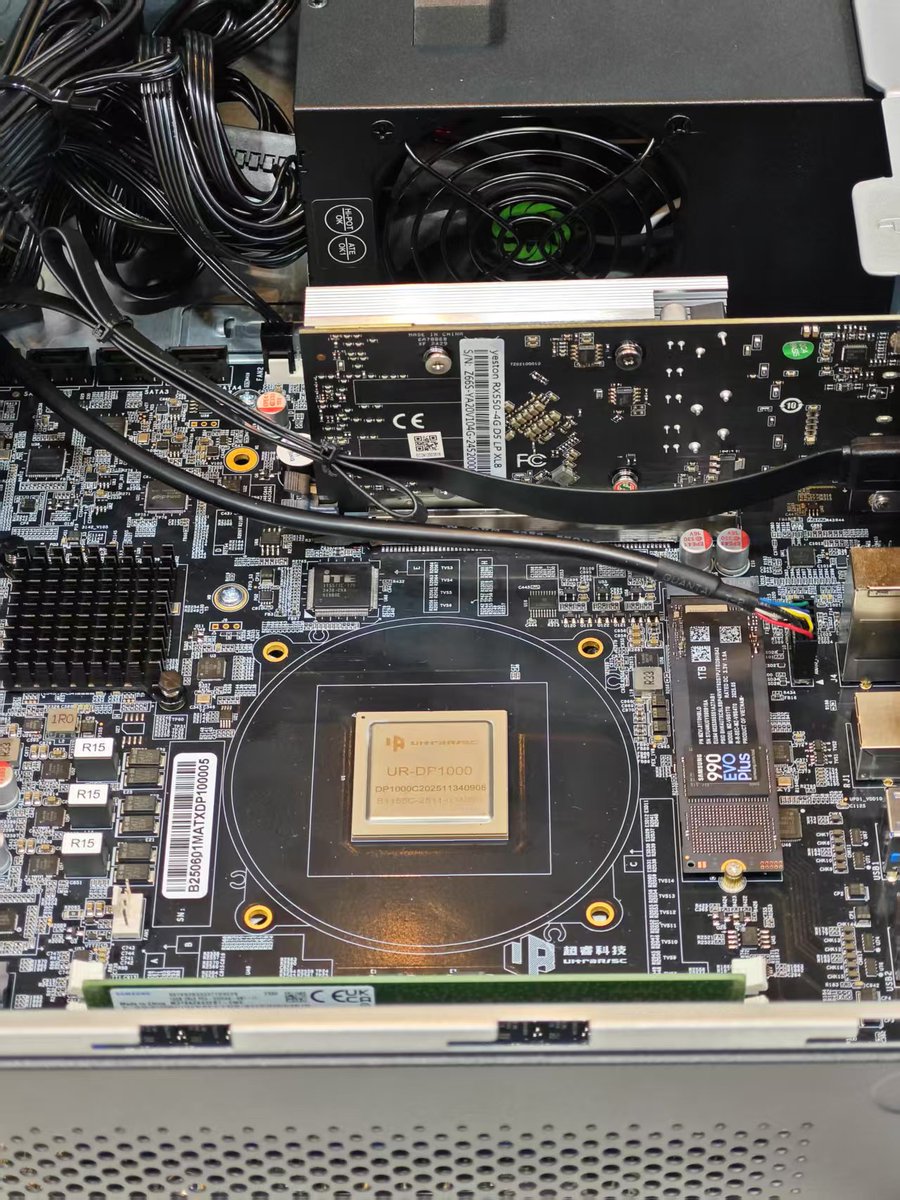

🚀 We’re back with the ultimate RISC-V MINI ITX - Milk-V Titan! Powered by UltraRISC UR-DP1000, the most powerful RISC-V CPU in production yet! Supports UEFI boot & plug-and-play high-end GPUs. PRE-ORDER Now! Get $50 off for just $5 on Arace.tech🔥#riscv #ultrarisc

🚀 Milk-V Titan Update More features, same price! Our BMC is now fully upgraded and built right into Titan — no extra module needed. ✅ Remote power control ✅ Real-time load & status monitoring Learn more👉: milkv.io/titan #RISCV

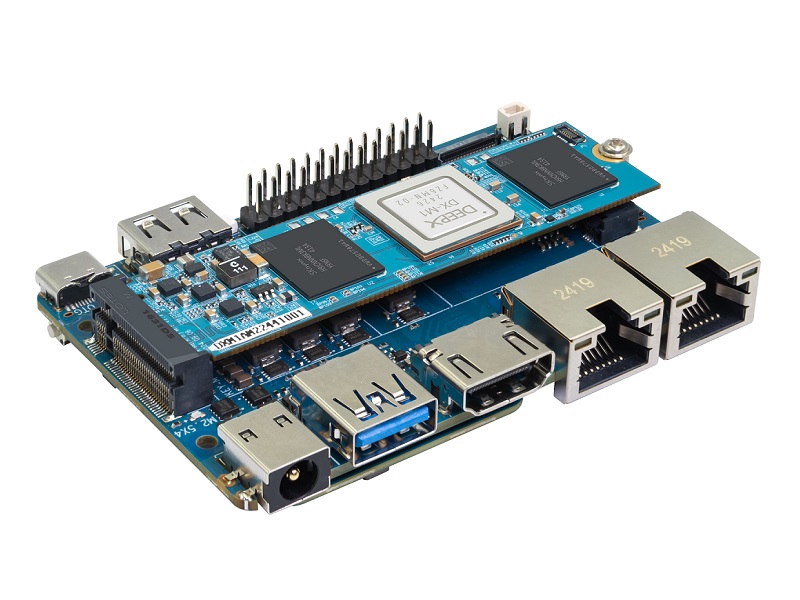

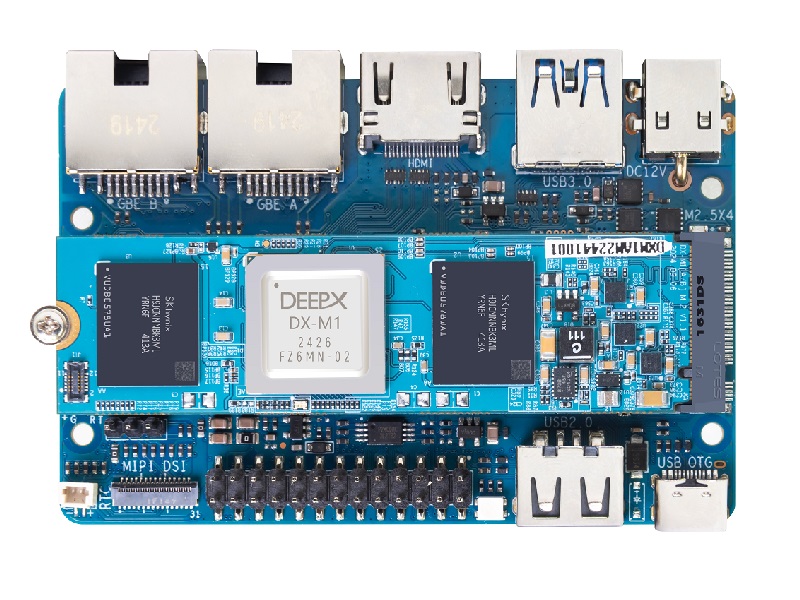

Banana Pi BPI-CM6 SpacemiT K1 8 core RISC-V board with Deepx for AI Edge Computing Gateway docs.banana-pi.org/en/BPI-CM6/Ban… #riscv #deepx #SpacemiT #ai #edgecomputer #bananapi #raspberrypi #orangepi

Last day at @MakerFaireRome 2025 🇮🇹 Showed the RISC-V in action with @DeepComputingio DC-ROMA RISC-V AI PC inside the @FrameworkPuter Laptop. Excited to keep spreading the word about #RISCV #OpenSource, and #OpenHardware in Rome!

Excited to bring @DeepComputingio + @risc_v + @FrameworkPuter to @FOSS_for_All — sharing the power of open computing with the community! #RISCV #Opensource

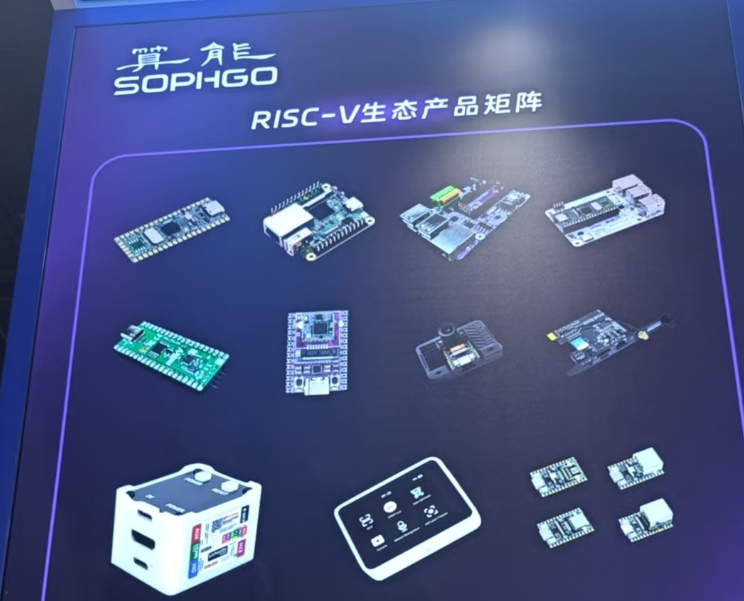

Visiting RISC-V Submit China ! #RVSC More powerful RISCV chips coming out this year, 2 of them even outperforming the RK3588 ! #RISCV chip is catching up, just waiting for software ecosystem ...

I've just run into the image below. It seems to somehow formally describe RV32I ISA. What language is this and what is it used for? #RISCV

MIPS' Sean Murphy took the stage at Embedded World, sharing how MIPS is creating #RISCV custom instructions to accelerate real-rime applications. He unveiled a novel solution for accelerating real-time motor control algorithms using a MIPS defined trigonometric math custom…

If you're writing assembler, I heartily recommend Compiler Explorer. I wrote about this from a RISC-V perspective a while back. #asm #riscv projectf.io/posts/riscv-co…

Oh yeah finally got the #milkv duo (256mb). Even came with a very useful SMD ruler (I needed one of those anyway). The #riscv adventures are going to be fun!!

Exciting news from #RISCVSummitChina, as Frans Sijstermans from NVIDIA announces CUDA is coming to RISC-V! This port will enable a RISC-V CPU to be the main application processor in a CUDA-based AI system. #RISCV #RISCVEverywhere

NVIDIA just bent the knee at the RISC-V Summit. CUDA now runs on the same architecture China is using to escape U.S. tech control. Here's why that should terrify Washington RISC-V’s Ascent Could Reshape The Global Compute Landscape share.google/1uysrSEflxhmhY…

At #RISCVSummit North America 2025, DeepComputing Founder & CEO @Yuning_XC5 will share how we’re bringing intelligent media experiences to life on RISC-V AI SoCs. Join us to explore how RISC-V is redefining the way AI applications run at the edge and beyond. #RISCV…

Pues hoy me ha llegado un juguete nuevo, a ver si lo pruebo a fondo, pero tiene muy buena pinta #nanoKVM, un KVM basado en un procesador #RISCV con un linux embebido . Y permite subir imágenes para arrancar desde CD/DVD. Aleeee al tajo!!!

Banana Pi BPI-RV2 Risc-V gateway board Siflower SF21H8898 bpi-shop.com/products/banan… #riscv #openwrt #bananapi #gateway #network

This couldn't have been a better commit number to switch from ch32v003fun to #ch32fun. Glad to be able to help serve the community surrounding everyone's favorite line of #RISCV microcontrollers. Thank you to all the contributors for getting this project to go the distance.

Banana Pi CamMV-K230D-Zero review magazinmehatronika.com/banana-pi-camm… #riscv #bananapi #raspberrypi #SBC #Canaan #k230d

Something went wrong.

Something went wrong.

United States Trends

- 1. #DWTS 4,992 posts

- 2. Elaine 67.8K posts

- 3. Veterans Day 451K posts

- 4. Jeezy 2,639 posts

- 5. Woody 20.6K posts

- 6. Tom Bergeron N/A

- 7. Tangle and Whisper 5,721 posts

- 8. Jaire 3,173 posts

- 9. Pat Murphy 1,634 posts

- 10. Stephen Vogt 1,275 posts

- 11. Keyshawn Hall N/A

- 12. State of Play 37.2K posts

- 13. Manager of the Year 3,232 posts

- 14. Toy Story 5 27.4K posts

- 15. #aurora 1,326 posts

- 16. Dame Sarr N/A

- 17. College Football Playoff 3,252 posts

- 18. Another 40 5,902 posts

- 19. #LHHMIA N/A

- 20. Errtime N/A