你可能會喜歡

Aquí hablan muy bien de Arduino UNO Q y explica todo el potencial real que tiene youtube.com/watch?v=KCXdNu…

youtube.com

YouTube

Por qué TODOS están PREOCUPADOS por la COMPRA de ARDUINO?

Qualcomm y su Arduino UNO Q (polémica) youtube.com/watch?v=zJh4XZ…

youtube.com

YouTube

El fin de una era: adiós a Arduino como lo conocíamos

Por si alguien quiere auto-regalarse esta navidades una computadora mecánica (estilo canicas) youtube.com/watch?v=GHPWwA…

youtube.com

YouTube

HAN CREADO UN ORDENADOR SIN ELECTRICIDAD *INVENTO DEL SIGLO*

Qualcomm compra a Arduino youtube.com/shorts/0ef819O…

youtube.com

YouTube

Qualcomm compra a Arduino #arduino #qualcomm #raspberrypi

Fallo tecnológico vs fallo humano vs fallo de mantenimiento (también humano) youtube.com/watch?v=w225BY…

youtube.com

YouTube

La Escalera Mecánica Más Peligrosa De Roma

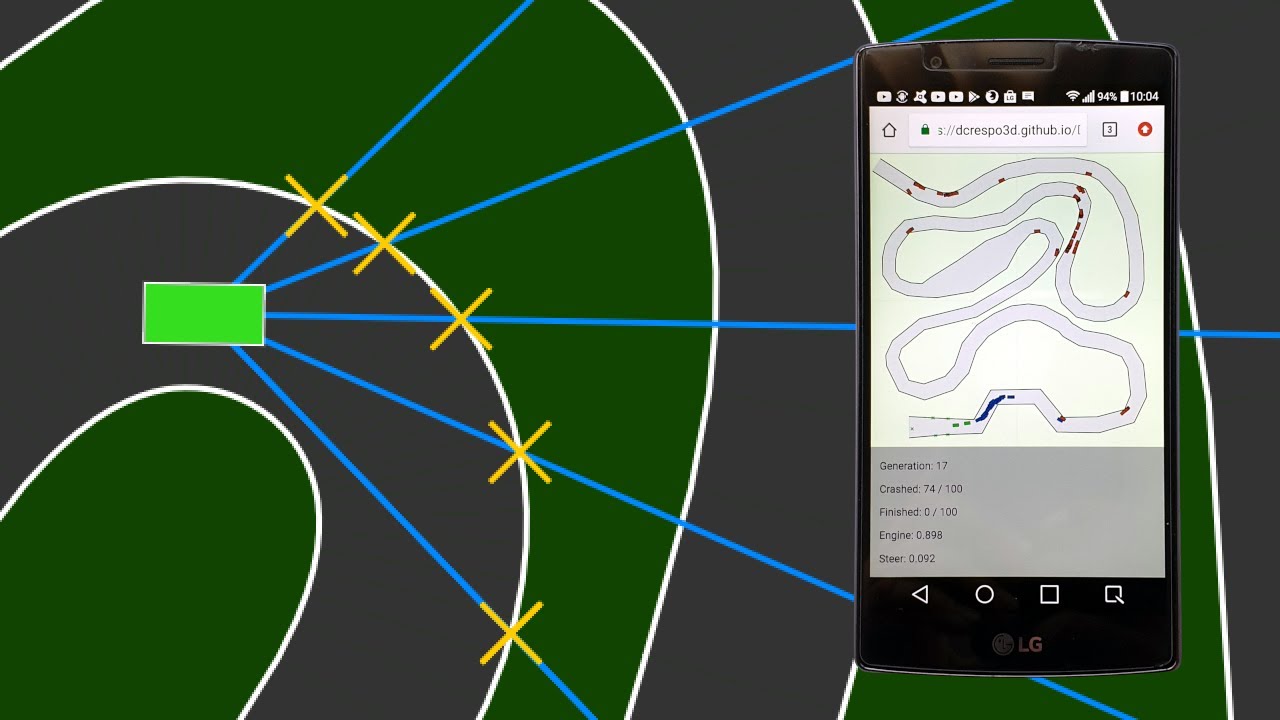

Redes neuronales junto a algoritmos genéticos: youtube.com/watch?v=RFTnK_…

youtube.com

YouTube

Estos coches APRENDEN a circular

Fantastic explanation of all 6 axes of the robot! 🦾 “Tell me and I will forget, show me and I may remember; involve me and I will understand.” I think that the quote fits here really well! 💬 Kawasaki Robotics compares specific robot axes to human body parts in a wonderful…

Por qué casi nadie usa Linux (aunque sea mejor) youtube.com/watch?v=daDc5z…

youtube.com

YouTube

Por qué casi nadie usa Linux (aunque sea mejor)

Un héroe invisible: youtube.com/watch?v=5vkRPp…

youtube.com

YouTube

Xerox vs el mundo: cómo sus ideas inspiraron a Apple y Microsoft

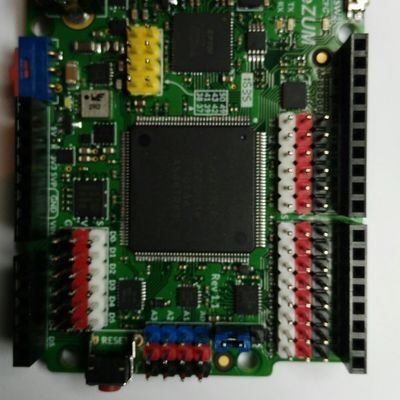

GreatScott! (canal de YT de más de 2M de suscriptores) Compara una FPGA con un microcontrador y aparece Icestudio (no es la primera vez) youtube.com/watch?v=l3d8uF…

youtube.com

YouTube

The Harsh Truth about FPGAs (You Should Avoid Them?!)

Ya he terminado la segunda sesión del tutorial de programación en python: L2: Salida por consola github.com/Obijuan/Learn-…

He creado una página en el Blog de Libros de Spectrum, son imágenes con enlaces a los libros en archive.org, es solo visual. Todo el contenido de los libros es gracias, y está en la web trastero.speccy.org . brownym.blogspot.com/p/libros-de-pr…

Estoy escribiendo un simulador de una pantalla de 16x12 leds para la consola, en python. Es muy útil para hacer pruebas del algoritmo de bresenham para renderizar líneas en la pantalla github.com/Obijuan/Learn-…

Probando el Venus-Risc-V simulator. Es una extensión de VSCode github.com/hm-riscv/vscod… Permite ejecutar paso a paso los programas en ensamblador, e incluye periféricos como una matriz de LEDs He programado la típica bola que rebota en las paredes, para probarlo #RISCV

También tiene una placa virtual con 2 LEDs, 2 pulsadores y 2 display de 7 segmentos Todo esto viene muy bien para hacer ejemplos de programación más avanzados, y más visuales #RISCV

Todos los ejemplos que estoy haciendo los estoy subiendo a este repositorio en github: github.com/Obijuan/Venus-… Aunque todavía no he generado documentación de cómo se usan #RISCV

Aprendizaje por refuerzo de forma mecánica (sin cables) youtube.com/watch?v=lo6yl6… Documento: gwern.net/doc/reinforcem…

youtube.com

YouTube

¿Puede una CAJA DE CERILLAS vencer a un Gran Maestro de Ajedrez? |...

* Lámina 49: Divisor del reloj del sistema entre 2 github.com/Obijuan/Icestu… * Generacion de una señal periodica de frecuencia Fsys/2 * Ej. Alhambra-II: la frecuencia de OUT es de 6Mhz * Se utiliza un contador unario módulo 2 * El ciclo de trabajo es del 50% #FPGAwars #Icestudio

* Lámina 47: Contador unario módulo 3 github.com/Obijuan/Icestu… * Contador unario de 0 a 2 (II), y comienza de nuevo desde 0 * Es el primer circuito que nunca para, realizando periódicamente la cuenta de 0 a 2 a la velocidad del reloj del sistema #FPGAwars #Icestudio

United States 趨勢

- 1. Columbus 76.7K posts

- 2. #WWERaw 31.7K posts

- 3. #SwiftDay 8,838 posts

- 4. #IDontWantToOverreactBUT N/A

- 5. #IndigenousPeoplesDay 3,498 posts

- 6. Middle East 170K posts

- 7. Marc 37.8K posts

- 8. Knesset 129K posts

- 9. #TSTheErasTour 2,294 posts

- 10. Seth 26.9K posts

- 11. Victory Monday 1,968 posts

- 12. Thanksgiving 45K posts

- 13. Good Monday 41.9K posts

- 14. Flip 49.9K posts

- 15. The Vision 84.4K posts

- 16. Bron Breakker 2,904 posts

- 17. Branch 49.6K posts

- 18. Happy 250th 2,497 posts

- 19. Broadcom 2,258 posts

- 20. Heyman 3,514 posts

Something went wrong.

Something went wrong.