#hdl4fpga search results

Hard work with emard to get working #hdl4fpga IPv4 core on a Half Duplex 100 Mbps LAN phy on #ULX3S. Nping rtt 7us, 0.05% packet loss. nano DHCP, ARP and of course ICMP protocols working

Some progress has been made on the USB core. The captured frames screenshot is a raw bitstream with bit stuffing extraction. CRC is included. Octets are MSB first. The screenshot data capture is done on the #ULX3S board using #HDL4FPGA's ser_debug app.

Having fun with the graphic adapter demo on #hdl4fpga. Loaded three #1920x1080 #24bpp images on #DDR at different addresses, and then by sending the base address by #UDP to the adapter, I swapped them. Video mode #1080p #60fps. Pretty much mesmerizing. Porting it now to #ULX3S.

Uploaded a 800x600x24bpp raw image into #ULX3S through USB, utilizing the #hdl4fpga USB link core. The process completed in 1.969s, achieving a transfer rate of 745,000 Bytes/s github.com/hdl4fpga/hdl4f…

Control flow and #FCS have been added to #hdl4fpga to transfer data reliably. A a picture of 970320 bytes (800 x 600 x 16 bits + some metadata) is uploaded in 4.16 seconds on #ULX3S using its #UART at 3MBd. Effective data transfer speed approx. 2330000 Bd.

First look at frame buffer. This is on Spartan3A DSP grade 4(the lower grade), #hdl4fpga open source core DDR* working at 166 MHz constrained or 333 MT/s, topping 170 MHz. Application includes a DHCP client, ARP and UDP decoding, and mutilple DMA channels. github.com/hdl4fpga/hdl4f…

They weren't write glitches but packet losses . But now some read glitches can be appreciate at specific address #hdl4fpga #DDR #framebuffer. #iguazufalls

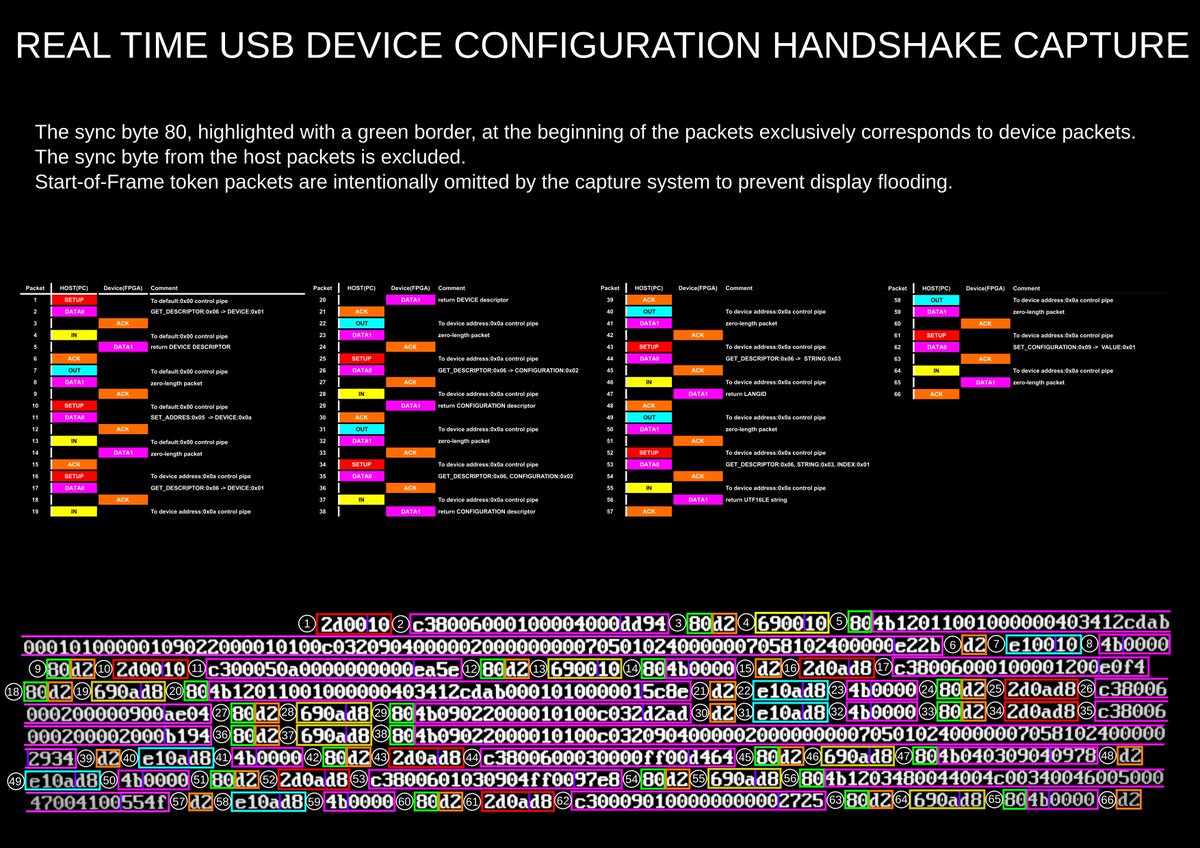

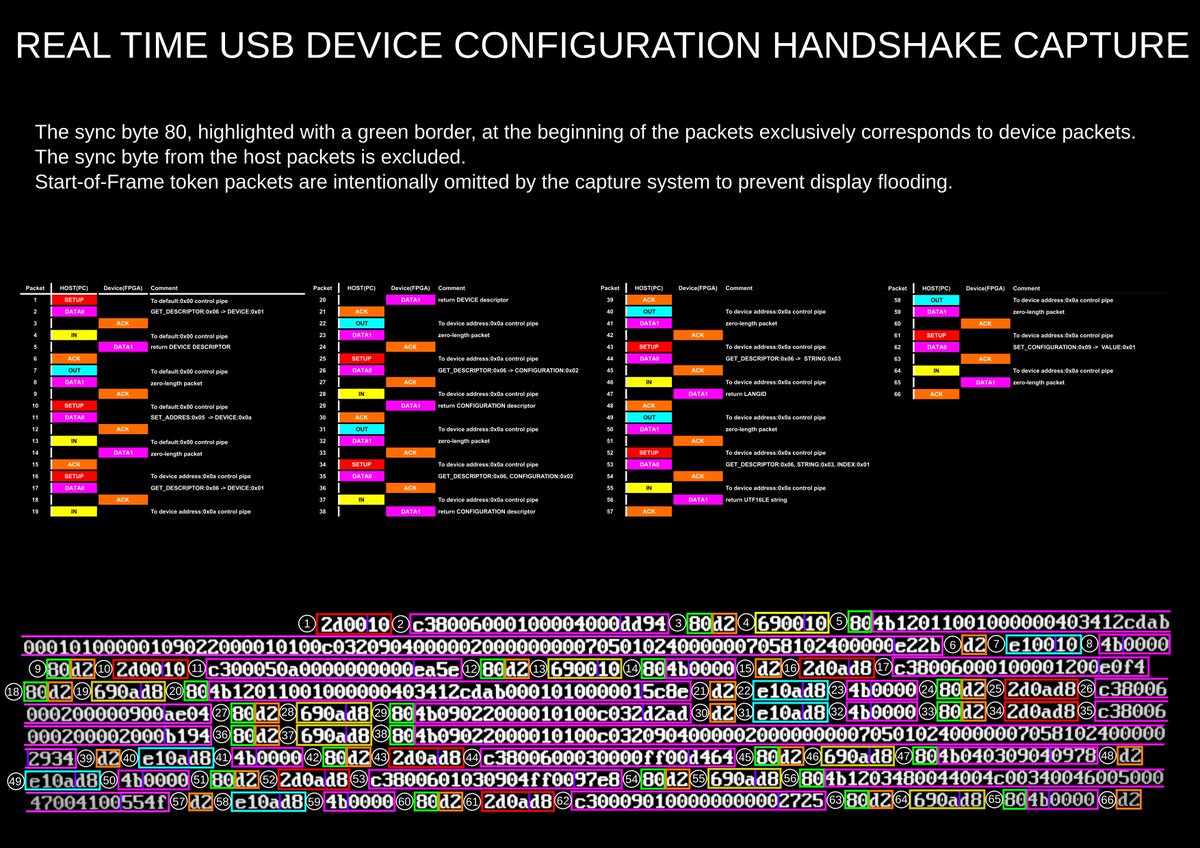

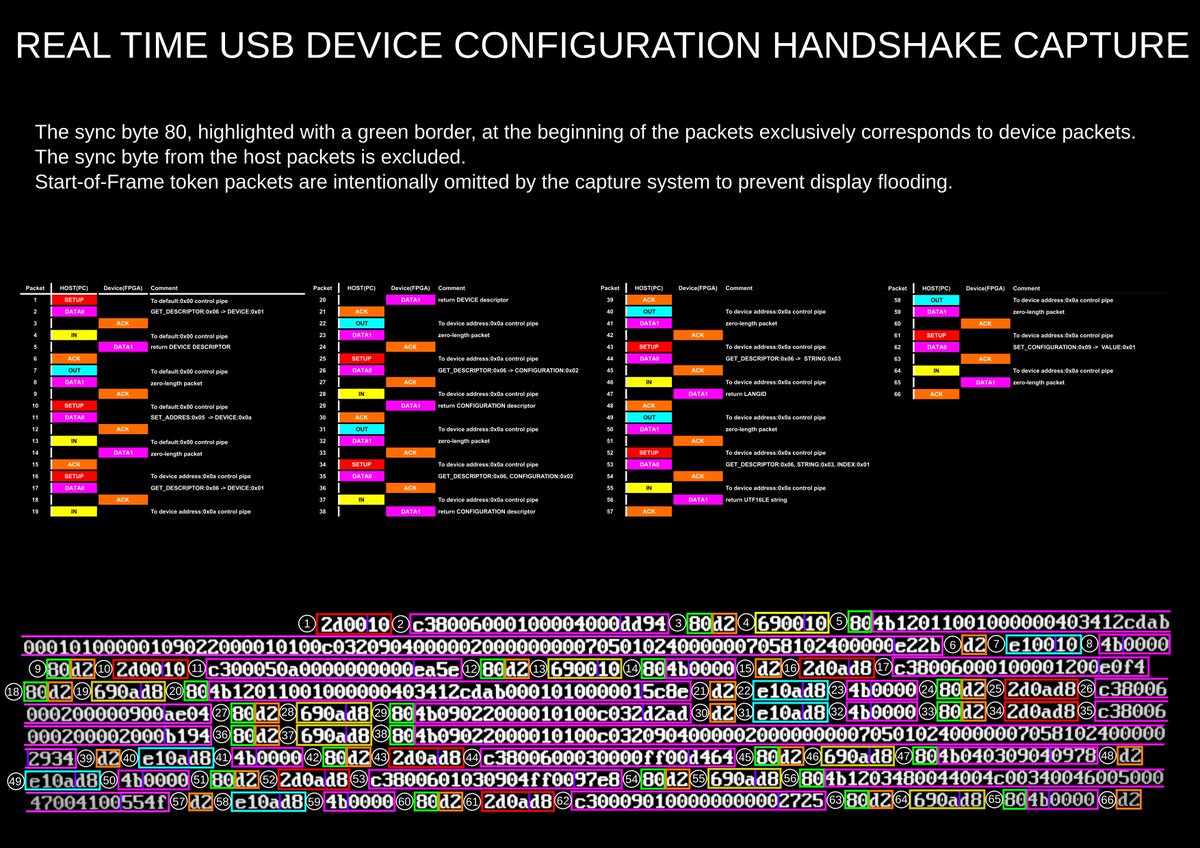

The #USB device communication link for #hdl4fpga is operational on the #ULX3S board. Here is a real-time configuration handshake capture. I hope it assists others in developing their own USB designs. It would have been helpful for me

First look at #framebuffer on #ULXS3 using #hdl4fpga #ddr core running on #SDRAM. #800x600@60hz #16bpp. READ/WRITE Burst cycle. BL selectable. Clock #133MHz. Everything looks good. Diamond project github.com/hdl4fpga/hdl4f…

#hdl4fpga #demo_graphics on #ULX4M github.com/intergalaktik/… 1080p30 #DDR3 #400MHz #800MTs #FPGA #ECP5 grade 7 thanks @GMahovlic to test it abroad.

This VHDL code is compatible with VHDL '87 and synthesis tools like Lattice Diamond, Quartus WEB, Xilinx ISE, and Vivado, and has been tested on #HDL4FPGA projects. Learn more: github.com/hdl4fpga/hdl4f… #VHDL #FPGA #ULX3S @radionaorg

summarizing. #hdl4fpga #DDR core runs on spartan3 grade 4 at 333 MT/s or 166 MHz and on grade 5 400MTs/s or 200 MHz

Proof of work of #hdl4fpga portable open source DDRx core. After fixing glitches, adding support for SDRAM as DDR core version 0

#HDL4FPGA #DDR3 @800MT/s has been ported to #Orangecrab orangecrab-fpga.github.io/orangecrab-har… github.com/hdl4fpga/hdl4f…. Thanks to @GMahovlic and @suarezvictor for testing on 25F and 85F version respectively

This VHDL code is compatible with VHDL '87 and synthesis tools like Lattice Diamond, Quartus WEB, Xilinx ISE, and Vivado, and has been tested on #HDL4FPGA projects. Learn more: github.com/hdl4fpga/hdl4f… #VHDL #FPGA #ULX3S @radionaorg

Uploaded a 800x600x24bpp raw image into #ULX3S through USB, utilizing the #hdl4fpga USB link core. The process completed in 1.969s, achieving a transfer rate of 745,000 Bytes/s github.com/hdl4fpga/hdl4f…

The #USB device communication link for #hdl4fpga is operational on the #ULX3S board. Here is a real-time configuration handshake capture. I hope it assists others in developing their own USB designs. It would have been helpful for me

Some progress has been made on the USB core. The captured frames screenshot is a raw bitstream with bit stuffing extraction. CRC is included. Octets are MSB first. The screenshot data capture is done on the #ULX3S board using #HDL4FPGA's ser_debug app.

#HDL4FPGA #DDR3 @800MT/s has been ported to #Orangecrab orangecrab-fpga.github.io/orangecrab-har… github.com/hdl4fpga/hdl4f…. Thanks to @GMahovlic and @suarezvictor for testing on 25F and 85F version respectively

#hdl4fpga #demo_graphics on #ULX4M github.com/intergalaktik/… 1080p30 #DDR3 #400MHz #800MTs #FPGA #ECP5 grade 7, @GMahovlic running memtest on the PC. Noisy image is an #LFSR writing and reading to check issues, while at the same time 4KB burst cycle is running by the video core

#hdl4fpga #demo_graphics on #ULX4M github.com/intergalaktik/… 1080p30 #DDR3 #400MHz #800MTs #FPGA #ECP5 grade 7 thanks @GMahovlic to test it abroad.

Hard work with emard to get working #hdl4fpga IPv4 core on a Half Duplex 100 Mbps LAN phy on #ULX3S. Nping rtt 7us, 0.05% packet loss. nano DHCP, ARP and of course ICMP protocols working

Control flow and #FCS have been added to #hdl4fpga to transfer data reliably. A a picture of 970320 bytes (800 x 600 x 16 bits + some metadata) is uploaded in 4.16 seconds on #ULX3S using its #UART at 3MBd. Effective data transfer speed approx. 2330000 Bd.

summarizing. #hdl4fpga #DDR core runs on spartan3 grade 4 at 333 MT/s or 166 MHz and on grade 5 400MTs/s or 200 MHz

Having fun with the graphic adapter demo on #hdl4fpga. Loaded three #1920x1080 #24bpp images on #DDR at different addresses, and then by sending the base address by #UDP to the adapter, I swapped them. Video mode #1080p #60fps. Pretty much mesmerizing. Porting it now to #ULX3S.

First look at #framebuffer on #ULXS3 using #hdl4fpga #ddr core running on #SDRAM. #800x600@60hz #16bpp. READ/WRITE Burst cycle. BL selectable. Clock #133MHz. Everything looks good. Diamond project github.com/hdl4fpga/hdl4f…

They weren't write glitches but packet losses . But now some read glitches can be appreciate at specific address #hdl4fpga #DDR #framebuffer. #iguazufalls

Proof of work of #hdl4fpga portable open source DDRx core. After fixing glitches, adding support for SDRAM as DDR core version 0

First look at frame buffer. This is on Spartan3A DSP grade 4(the lower grade), #hdl4fpga open source core DDR* working at 166 MHz constrained or 333 MT/s, topping 170 MHz. Application includes a DHCP client, ARP and UDP decoding, and mutilple DMA channels. github.com/hdl4fpga/hdl4f…

#hdl4fpga #demo_graphics on #ULX4M github.com/intergalaktik/… 1080p30 #DDR3 #400MHz #800MTs #FPGA #ECP5 grade 7 thanks @GMahovlic to test it abroad.

Hard work with emard to get working #hdl4fpga IPv4 core on a Half Duplex 100 Mbps LAN phy on #ULX3S. Nping rtt 7us, 0.05% packet loss. nano DHCP, ARP and of course ICMP protocols working

Some progress has been made on the USB core. The captured frames screenshot is a raw bitstream with bit stuffing extraction. CRC is included. Octets are MSB first. The screenshot data capture is done on the #ULX3S board using #HDL4FPGA's ser_debug app.

They weren't write glitches but packet losses . But now some read glitches can be appreciate at specific address #hdl4fpga #DDR #framebuffer. #iguazufalls

First look at #framebuffer on #ULXS3 using #hdl4fpga #ddr core running on #SDRAM. #800x600@60hz #16bpp. READ/WRITE Burst cycle. BL selectable. Clock #133MHz. Everything looks good. Diamond project github.com/hdl4fpga/hdl4f…

First look at frame buffer. This is on Spartan3A DSP grade 4(the lower grade), #hdl4fpga open source core DDR* working at 166 MHz constrained or 333 MT/s, topping 170 MHz. Application includes a DHCP client, ARP and UDP decoding, and mutilple DMA channels. github.com/hdl4fpga/hdl4f…

The #USB device communication link for #hdl4fpga is operational on the #ULX3S board. Here is a real-time configuration handshake capture. I hope it assists others in developing their own USB designs. It would have been helpful for me

This VHDL code is compatible with VHDL '87 and synthesis tools like Lattice Diamond, Quartus WEB, Xilinx ISE, and Vivado, and has been tested on #HDL4FPGA projects. Learn more: github.com/hdl4fpga/hdl4f… #VHDL #FPGA #ULX3S @radionaorg

Something went wrong.

Something went wrong.

United States Trends

- 1. #UFC322 131K posts

- 2. Valentina 15.2K posts

- 3. Morales 35.3K posts

- 4. Prates 33.8K posts

- 5. Sark 5,971 posts

- 6. Kirby 18.8K posts

- 7. Georgia 85.7K posts

- 8. Zhang 26.5K posts

- 9. #GoDawgs 9,626 posts

- 10. Leon 74.8K posts

- 11. Ole Miss 12K posts

- 12. Sean Brady 6,660 posts

- 13. Makhachev 35.4K posts

- 14. Arch 22.4K posts

- 15. Dillon Danis 9,170 posts

- 16. Ahmad Hardy 1,250 posts

- 17. Bo Nickal 6,989 posts

- 18. Texas 201K posts

- 19. Bama 22.6K posts

- 20. Gunner Stockton 2,187 posts