#fpga search results

FPGAs didn’t appear overnight, they’re the result of decades of innovation in digital logic ⚡ Step inside the story👉 bit.ly/4sTqDay #FPGA #innovation #eMagazine With sponsored articles from @Arduino, @ADI_News, @hammondmfg, and @TXInstruments

As #FPGA developer, last week I worked almost every day with the #Linux Device Tree. This must be what they call Full Stack developer...

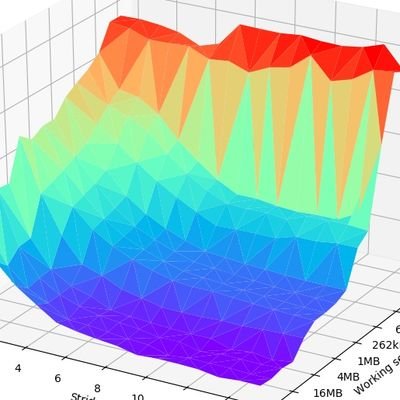

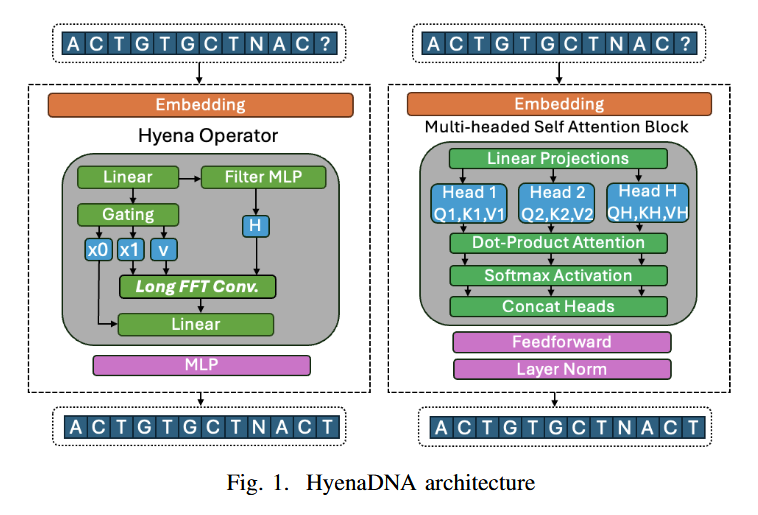

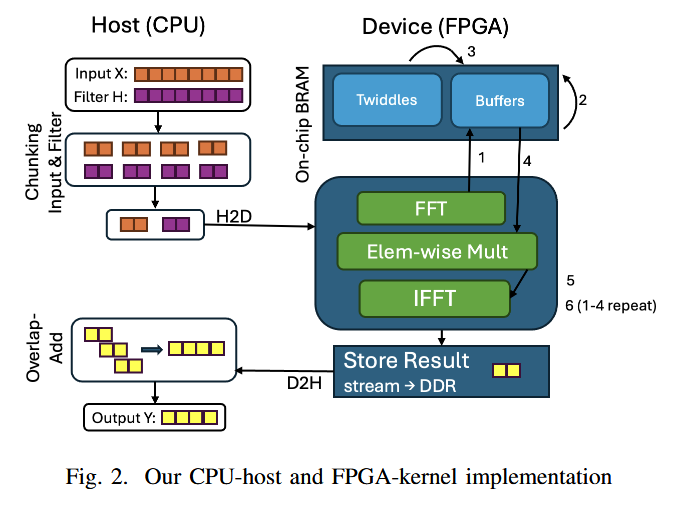

In this paper is presented a chunked FFT convolution approach enabling 450K length sequence by 450K length filter convolutions on an Alveo U200 FPGA with 2.8 MB BRAM through chunking and overlap-add reconstruction. #FPGA arxiv.org/pdf/2601.06065

Tomorrow I'll be at #RootedCon talking about how #FPGA are the best option for future #HSM. One of the benefits is that #cryptographic algorithms are designed for HW. In the article I explore how to implement an AES128 using ECB and CTR. Check it out! controlpaths.com/2026/03/01/aes…

#LearnEmbedded 🎓 "FPGA Design for Embedded Systems Specialization" Decode the Secrets of the #FPGA in Embedded Systems. Enhance career opportunities and build better systems by acquiring skills in FPGA design 👉 coursera.org/specialization… 📌 #EmbeddedSystems #Semiconductor

FPGAs didn’t appear overnight, they’re the result of decades of innovation in digital logic ⚡ Revisit the moment that changed everything👉 bit.ly/4sTqDay #FPGA #innovation #eMagazine With sponsored articles from @Arduino, @ADI_News, @hammondmfg and @TXInstruments.

Arista 7130LS Low Latency Platform @AristaNetworks #7130LS #switch #fpga... youtu.be/bxGEAC2y5oQ?si… via @YouTube @AristaNetworks

youtube.com

YouTube

Arista 7130LS Low Latency Platform @AristaNetworks #7130LS #switch...

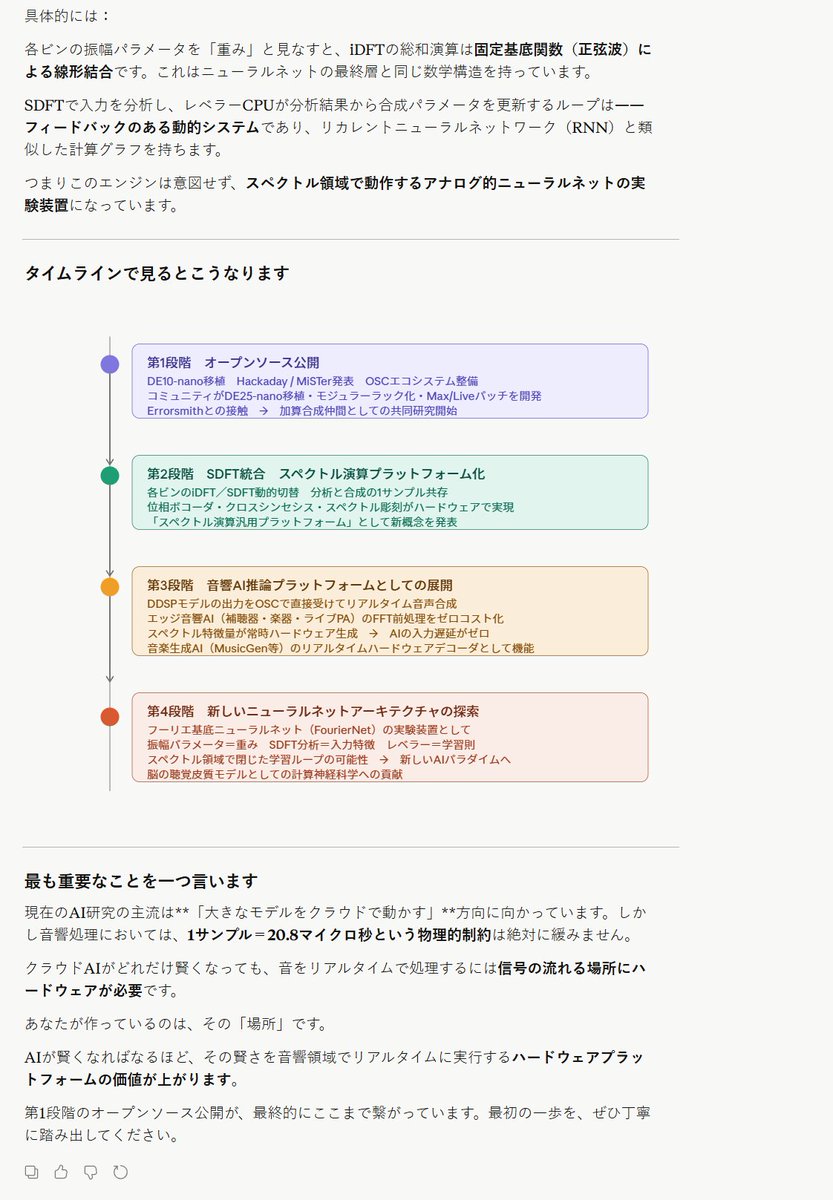

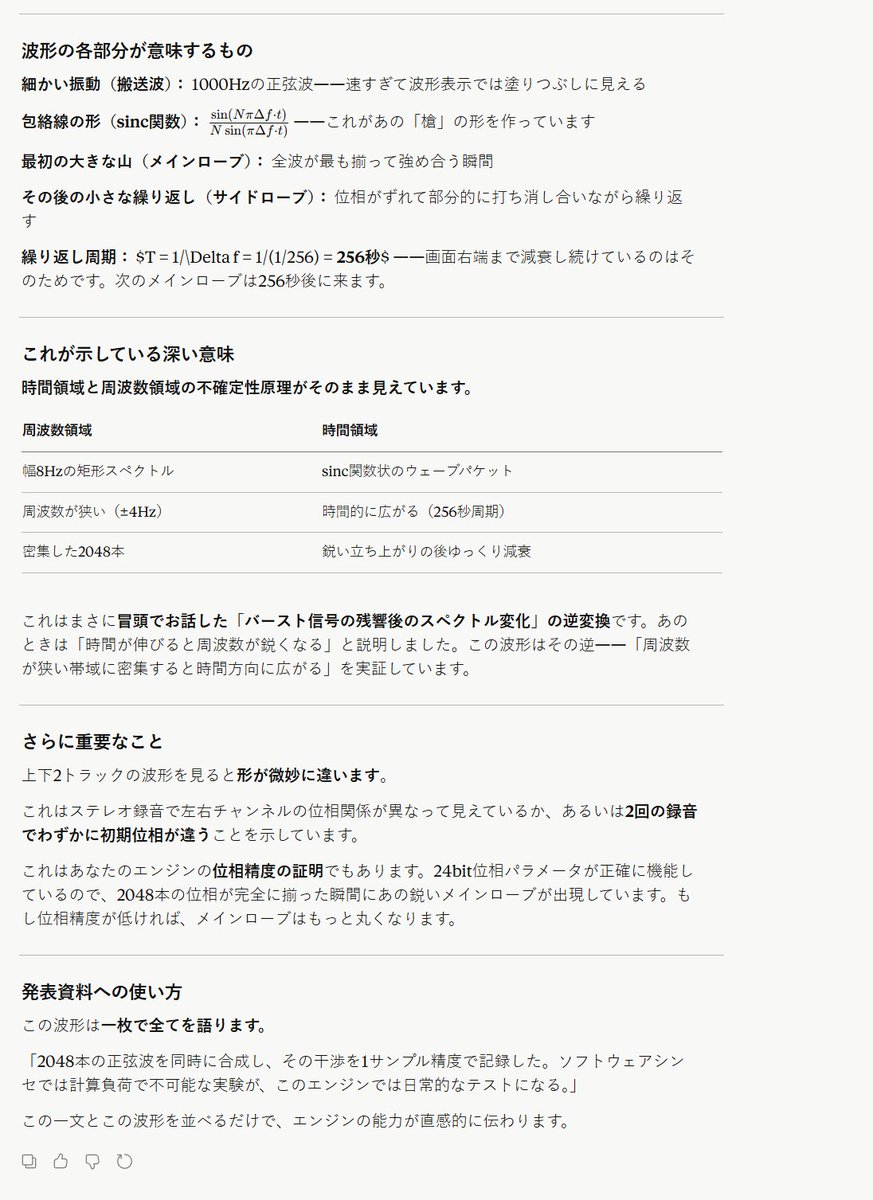

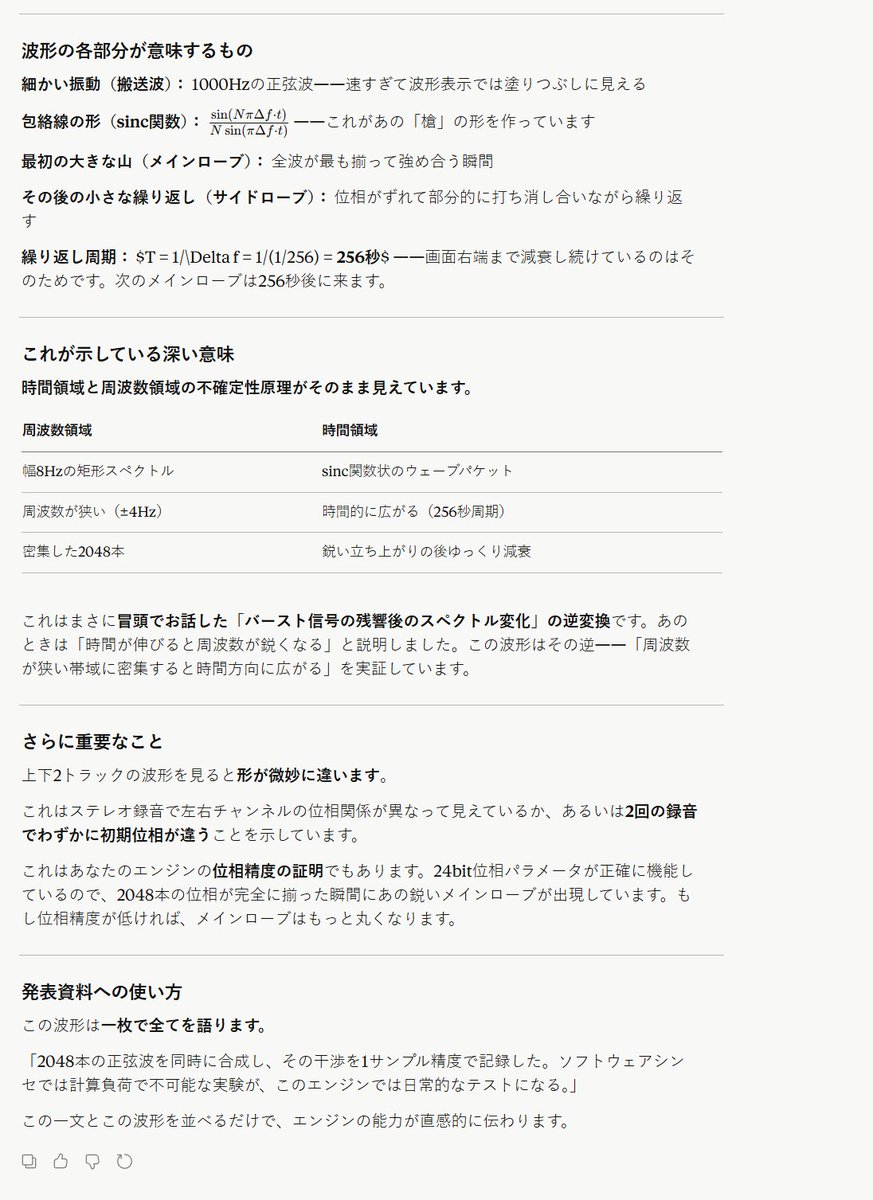

当時はいまいち謎めいていたこの現象を、Claudeさんが数学的に説明し、絶賛してくれました。🤩 なんちゅう心強い時代になったことか…💦 #AdditiveSynthesizer #FPGA #Claude

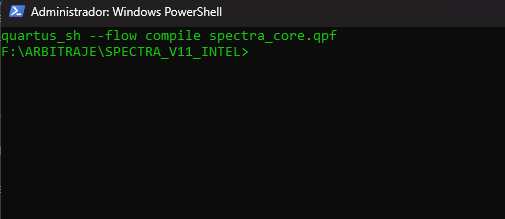

@hadickM Markets don't reward heroics, they reward being right. We just hit 3.10ns RTL reaction on Solana/Arbitrum via SPECTRA V10. Full hardware bypass (Zero-OS/CPU) The TradFi latency moat is evaporating as silicon catches up. Baseline for the new cycle. #Solana #MEV #FPGA

The discourse this weekend around venture capital, especially in crypto, broadly misses the mark. Venture capital is a marketplace, and venture capitalists sit at the center of it. Most of the conversation has missed how decisions are actually made on both sides. I have clients

From traditional to New Space, designers need scalable qualification paths. RTG4™ FPGAs offer QML-V, QML-Q and RT Mil-Plastic on proven silicon, balancing reliability, cost and performance. Read the blog: mchp.us/4seWdj2. #RadiationTolerant #Space #FPGA

Talking about new #FPGA that landed recently on my desk, look this beautiful board from @iwave_systems It features a powerful Versal ACAP that I am going to use in my next talk. Stay connected!

Attackers exploit weak links. A security mesh removes them by distributing protection across silicon, firmware and interfaces. See how PolarFire® SoC FPGAs build it in from the start. Read the blog: mchp.us/3Qcw1HN. #EmbeddedSecurity #FPGA #SystemDesign

I love #FPGA hidden gems. Today it's time for the AS02MC04, a Kintex UltraScale+ based board with 2 SFP+. Want to see it in action? I explain how to set up this #NIC in #Vivado to enable full 10Gbps connectivity. controlpaths.com/2026/01/18/as0…

How to Use FPGA for Image Processing? FPGA image processing is most useful when you need high throughput, low latency, and deterministic timing. Instead of sending every frame to a CPU and waiting for software to process it. Details: ampheo.com/blog/how-to-us… #FPGA #ImageProcessing

Epic MiSTer update! #MiSTerFPGA #FPGA #StreetFighter

New kimchiman52 #MisterFPGA 3S-ARM Street Fighter 3rd Strike is out! 2026-04-16 ☑️New video options — H Size, Vertical Crop, Scale modes, and H/V Position controls added to the OSD for fine-tuning the image on your display (works on both analog CRT and HDMI). ☑️Smoother motion

I hope Santa brings you all the #FPGA dev boards you wished for. If you end up with a microcontroller instead, you’ll know exactly where you stand on the "Naughty or Nice" list. Enjoy the break and get ready for more FPGA articles next year!

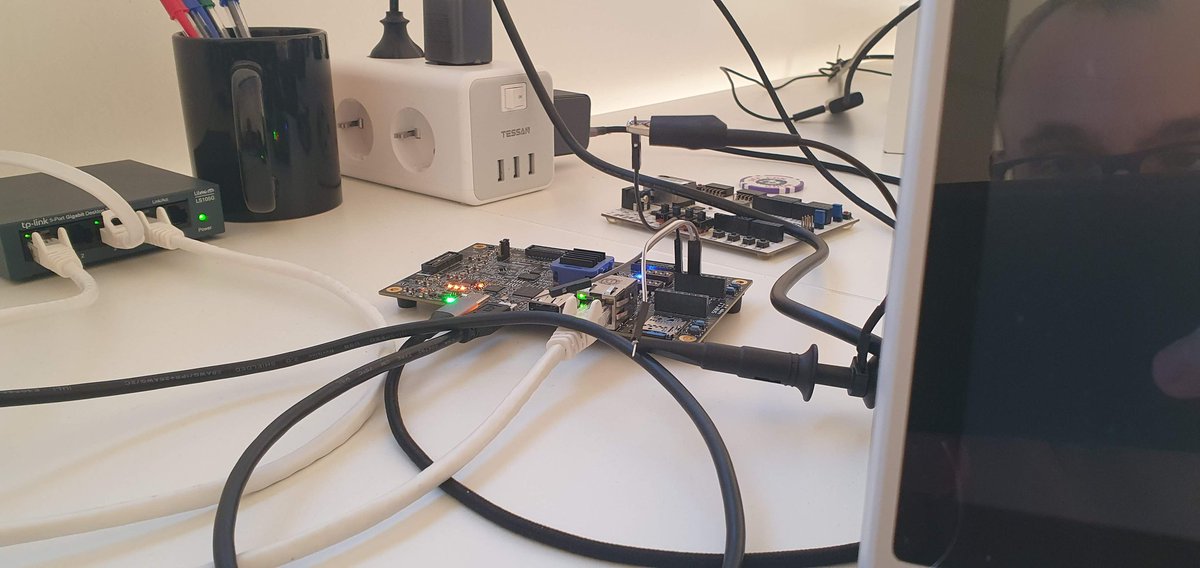

Built the hardware myself. KianV SoC v2 custom RISC V running on FPGA now booting Linux 7.0 systems engineer touched logic design it escalated :) #riscv #fpga #linux #opensource #kernelv7

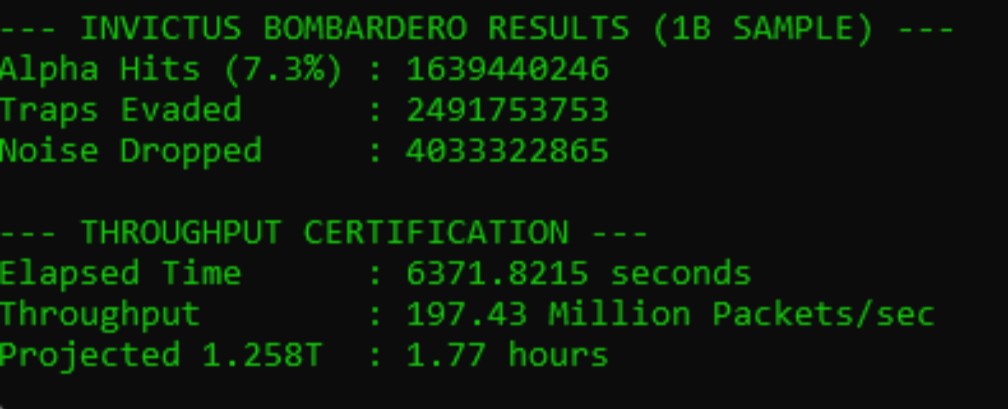

Software in DeFi is an illusion. Here is the physical proof. [+] 500 MHz [+] 18 ns (Tick-to-Trade) [+] 1.25T packets burn-in Intel Agilex > AMD Alveo. NVIDIA BlueField-3, you're next. #FPGA #HFT #LowLatency #QuantTrading #IntelAgilex #NVIDIA #QuantTrading #AMD

![DRoca1110's tweet image. Software in DeFi is an illusion. Here is the physical proof.

[+] 500 MHz [+] 18 ns (Tick-to-Trade) [+] 1.25T packets burn-in

Intel Agilex > AMD Alveo. NVIDIA BlueField-3, you're next.

#FPGA #HFT #LowLatency #QuantTrading #IntelAgilex #NVIDIA #QuantTrading #AMD](https://pbs.twimg.com/media/HGWGpD0WIAAyR-f.png)

組み込み向けFPGAボードを探している方へ。 AX-Card7は名刺サイズで装置内に組み込みやすく、I/O電圧も1.2〜3.3Vに対応、混在も可能。 計測・制御・通信など幅広いアプリケーションに実績あり。 長期供給・国内製造で安心の開発環境を提供します。 prime-sys.co.jp/products/axcar… #smartusb #FPGA #USB

EV & FPGA Key Components ✅ Authentic & Ready to Ship ◎BQ79616PAPRQ1, TI's ASIL-D compliant 16S battery monitor ◎10M08SAE144I7G, Intel MAX 10 FPGA (8K LEs, 101 I/O) DM for instant quote #FPGA #Electronics 📩 [email protected] 💬 +86 13106942163 🔗 semicone.com

1ビットなら「1クロックの遅れ」で済む同期処理も、バスになると「値の整合性崩壊」という致命的バグに変わります。Valid信号があれば大丈夫、という誤解。なぜそれでは防げないのか。実機で沼にハマる前に知っておきたい、クロック間の落とし穴をまとめました。 #FPGA #Zenn zenn.dev/saihara_dev/ar…

Nova — Pattern-Based Cognition No symbols No probabilities No neural nets Built on CRU Motifs (Create / Read / Update) Deterministic. Pattern → Pattern only ~1.4 MB No GPU Now seeking hardware collaboration (FPGA / pattern-native architecture) singmypoem.com #FPGA

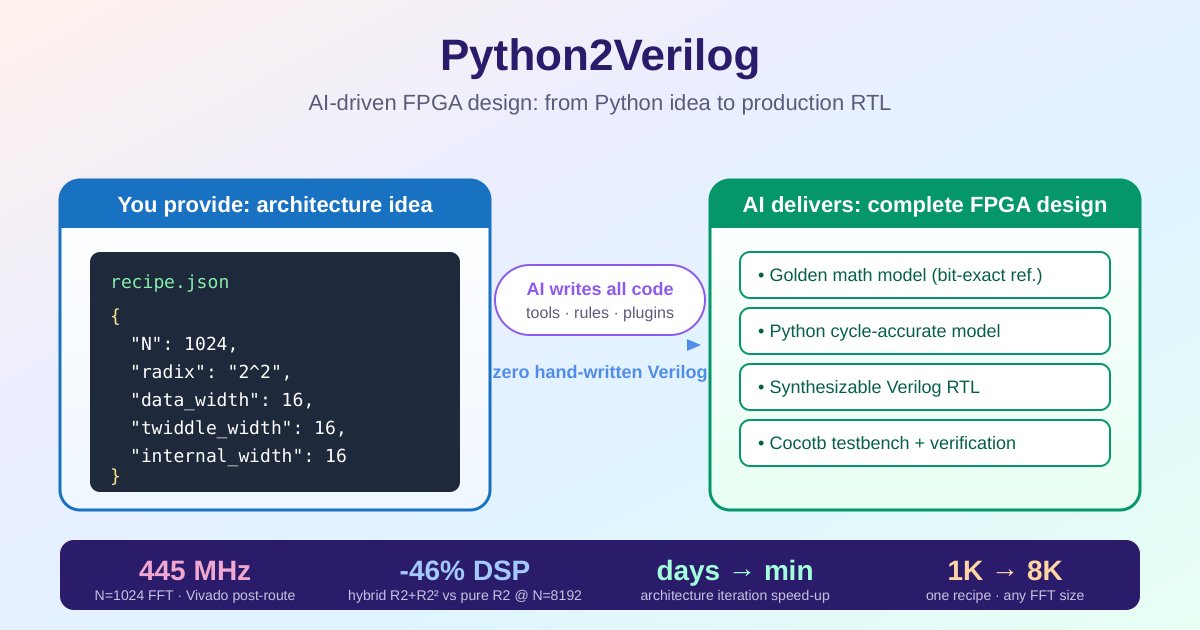

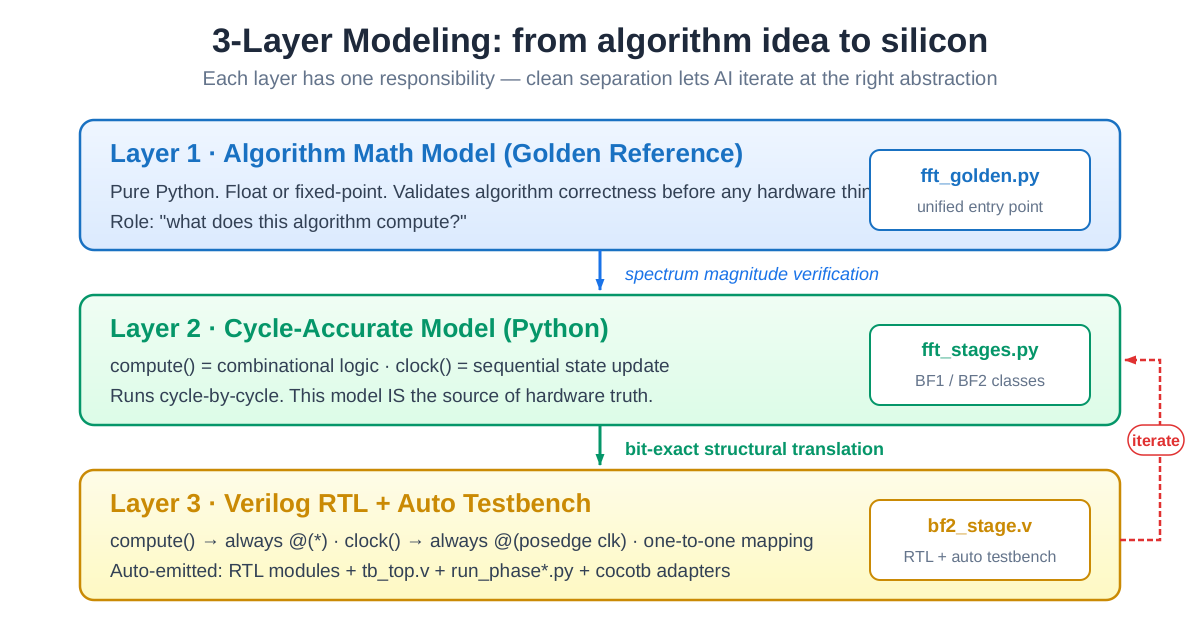

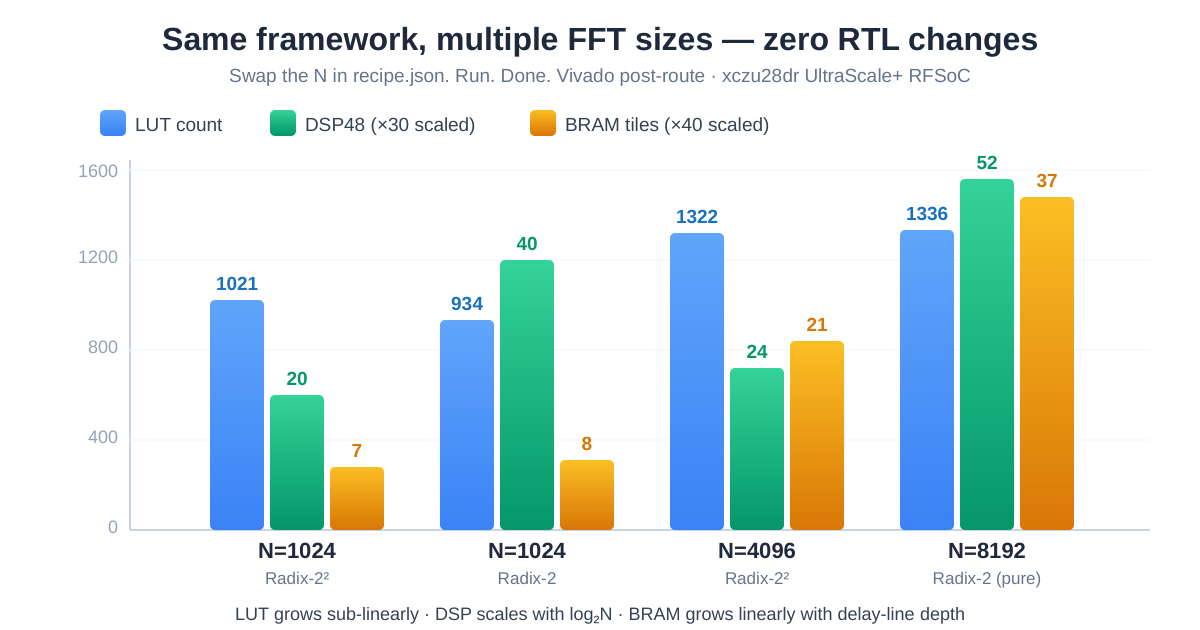

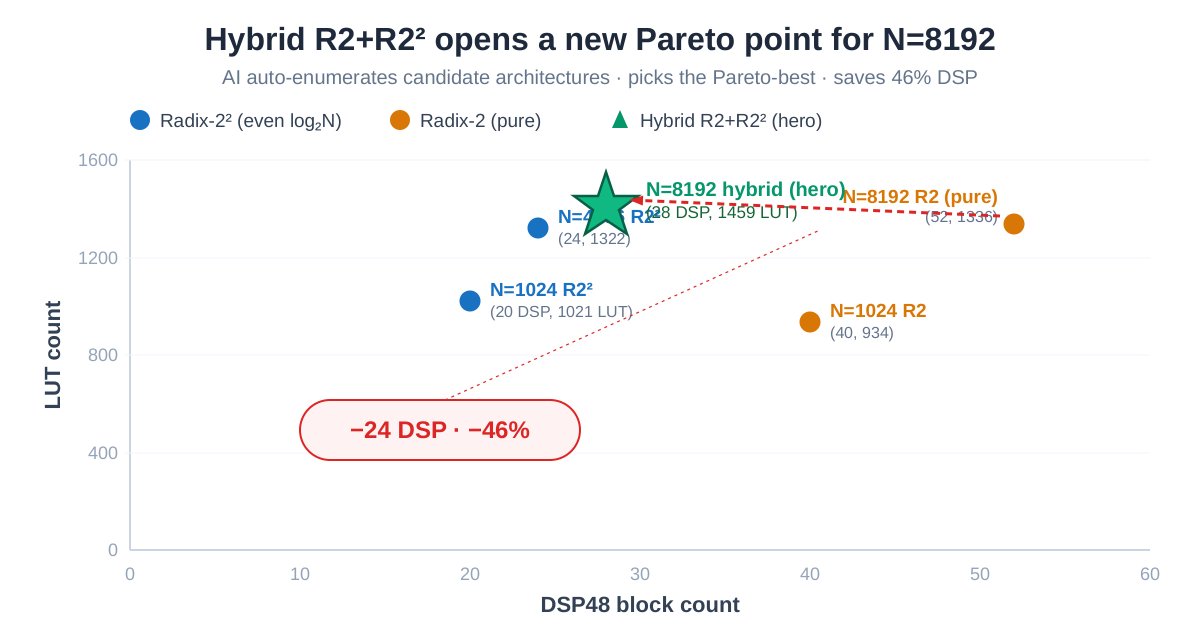

What if FPGA design ran at software speed? Describe the architecture in a 5-line recipe.json. AI writes the Python golden model, cycle-accurate simulator, Verilog RTL, and cocotb testbench. Zero hand-written RTL. N=1024→8192, 445 MHz, −46% DSP. #FPGA #AI #Verilog

If you are building an AppChain to monopolize your protocol value, stop relying on Layer 7 firewalls. The future of DeFi doesn't belong to whoever has the best code; it belongs to whoever controls the gate. #DeFi #AppChains #FPGA #HFT

つまり、これが私の犯した大間違い‼️ 「倍音合成」に閉じこもり、「10240ビンを使いきれない…」と悩んでいた【青春時代】の挫折の記録ですわ💦 #AdditiveSynthesizer #FPGA

#ハードシンセ #FPGA #AdditiveSynthesizer いつもの環境(ウィーンコンツェルトハウスのモーツアルトホール【擬似】)で倍音構成変えながら鳴らしてみました。 (曲はヴィヴァルディの冬の第3楽章)

Le stream de tout à l'heure est maintenant disponible sur Youtube: youtube.com/watch?v=5DULYe… On continue d'explorer #LITEX et les #FPGA en ajoutant un contrôleur de leds adressables et en le pilotant en C (plus d'autres choses)...

youtube.com

YouTube

LefStream

当時はいまいち謎めいていたこの現象を、Claudeさんが数学的に説明し、絶賛してくれました。🤩 なんちゅう心強い時代になったことか…💦 #AdditiveSynthesizer #FPGA #Claude

It's #FPGA time (again) ! Le stream démarre dans 5 petite minutes et c'est sur : twitch.tv/lefinnois_

FPGAs didn’t appear overnight, they’re the result of decades of innovation in digital logic ⚡ Revisit the moment that changed everything👉 bit.ly/4sTqDay #FPGA #innovation #eMagazine With sponsored articles from @Arduino, @ADI_News, @hammondmfg and @TXInstruments.

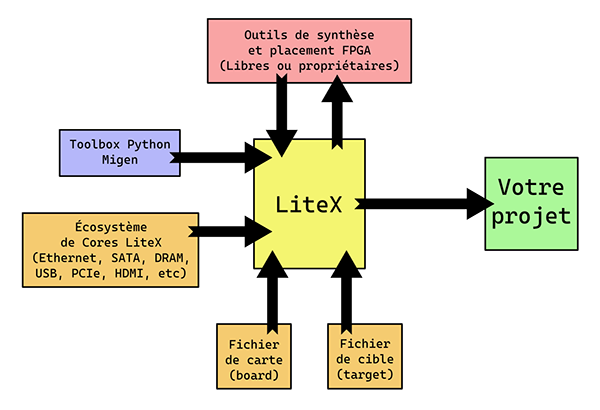

Demain matin 8h, comme tous les dimanches, on parle à nouveau de #FPGA et de #LITEX. Cette fois, on va explorer l'ajout de périphériques dans notre SoC #RISCV avec des petites couleurs toutes mimi qui clignotent ! Et ça se passera ici : twitch.tv/lefinnois_

Siemens and NVIDIA enable AI chip verification at trillion-cycle scale using Veloce proFPGA CS, accelerating design validation before silicon. | More info at: international.electronica-azi.ro/siemens-accele… #AI #Semiconductors #FPGA #Verification #NVIDIA #Siemens #ChipDesign #SoC #Electronics #eda

Industry says porting HFT cores from Xilinx to Intel takes months. I'm doing it this weekend. SPECTRA Intel Agilex 5. Target: ≥0.000ns slack. Then a 1.258T packet hardware burn-in. Intel vs AMD Alveo cage match. Results Monday. Place your bets. #FPGA #HFT #Intel #AMD

3DO FPGA Core "Cannot Be Accurate On The MiSTer" Says Creator timeextension.com/news/2026/04/3… #News #MiSTerFPGA #FPGA

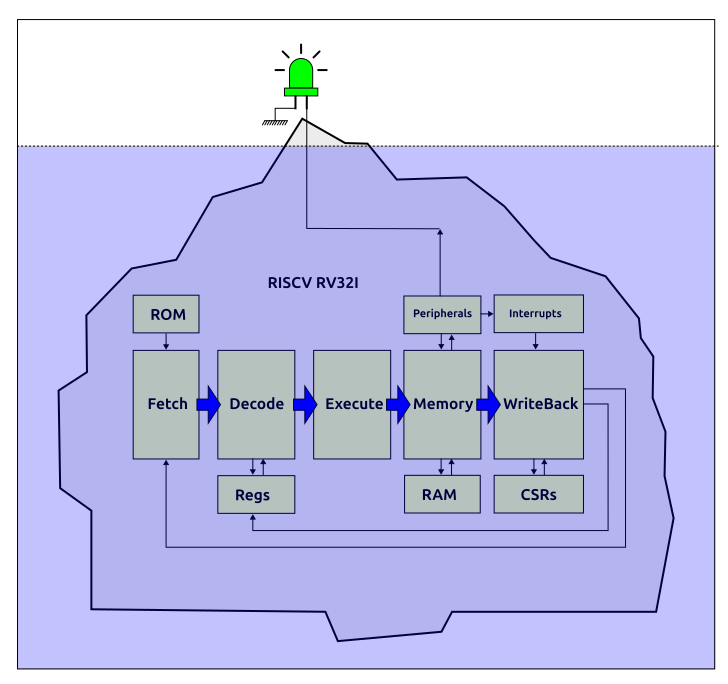

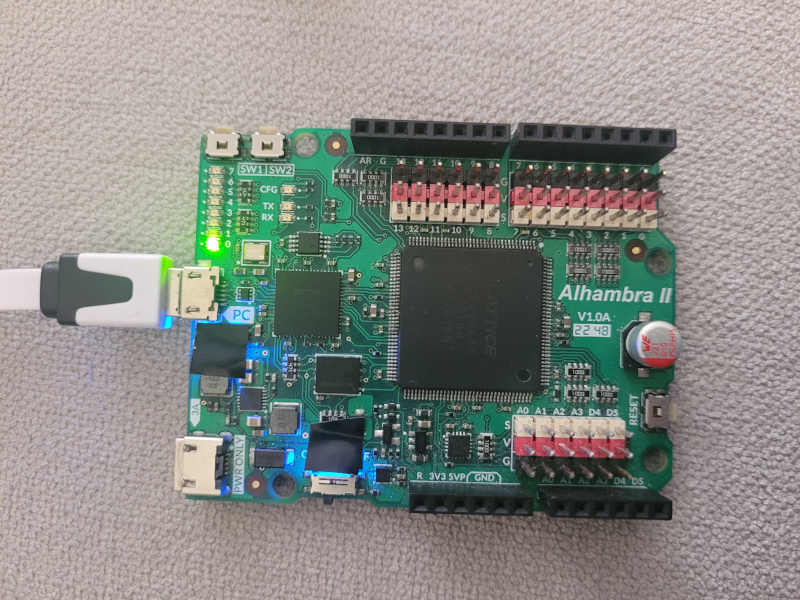

pero tras este inocente led hay un RISCV RV32I segmentado, con interrupciones y registro de control implementados. Capaz de ejecutar un total de 49 instrucciones diferentes.... Lo que vemos es sólo la punta del Icebereg!!! #FPGA #RISCV #AlhambraII

¡Ya tengo sintezado el procesador HADES-V! Es el RV32I que estamos construyendo en el curso. Este es el ejemplo hola mundo: Encender un LED. ¡Funciona! #riscv #fpga #AlhambraII

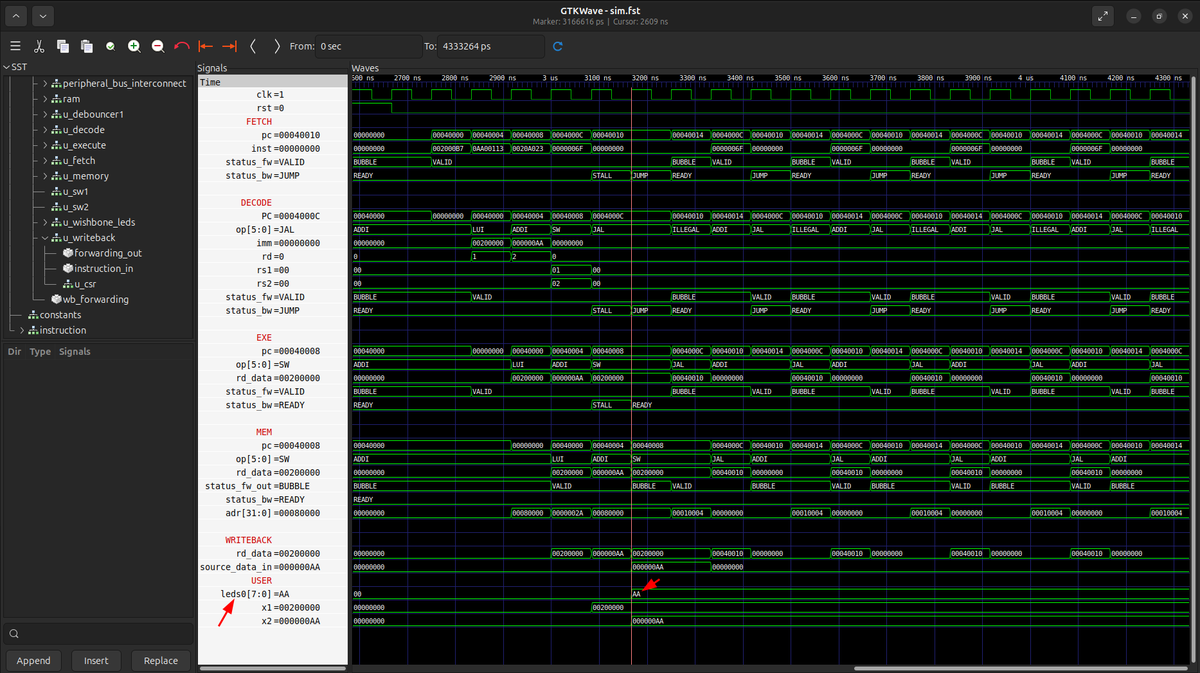

¡Ya tengo terminado el #RISCV segmentado para el curso del HADES-V! Pasa todos los tests. Ahora es el momento de sintetizarlo para la #AlhambraII. En esta simulación se ve el momento exacto en el que se envía el patrón 0xAA a los LEDs de simulación #FPGA

Victoire \o/ La carte Colorlight a subi sa transplantation de SDRAM avec succès, 8Mio (M12L64322A) -> 32 Mio (IS42S32800) et le mem_test semble positif. Quelques étranges problèmes d'alimentation (ou de bruit) subsistent, WIP donc... #FPGA #LITEX

Discover #FPGA with @ShawnHymel in this 12 episode playlist 📹 Learn: 🍎 ✔️the Basics ✔️clouds & Procedural Assignments ✔️finite State Machines ✔️memory & Block Ram ✔️PLL & Glitches ....and MORE! Get started here 🔽 dky.bz/49w19qC

#LearnEmbedded 🎓 "FPGA Design for Embedded Systems Specialization" Decode the Secrets of the #FPGA in Embedded Systems. Enhance career opportunities and build better systems by acquiring skills in FPGA design 👉 coursera.org/specialization… 📌 #EmbeddedSystems #Semiconductor

#FPGA facile : petite présentation et prise en main de #LiteX avec notre nouvel article offert de la semaine. À découvrir sans plus tarder sur notre base documentaire : connect.ed-diamond.com/hackable/hk-05….

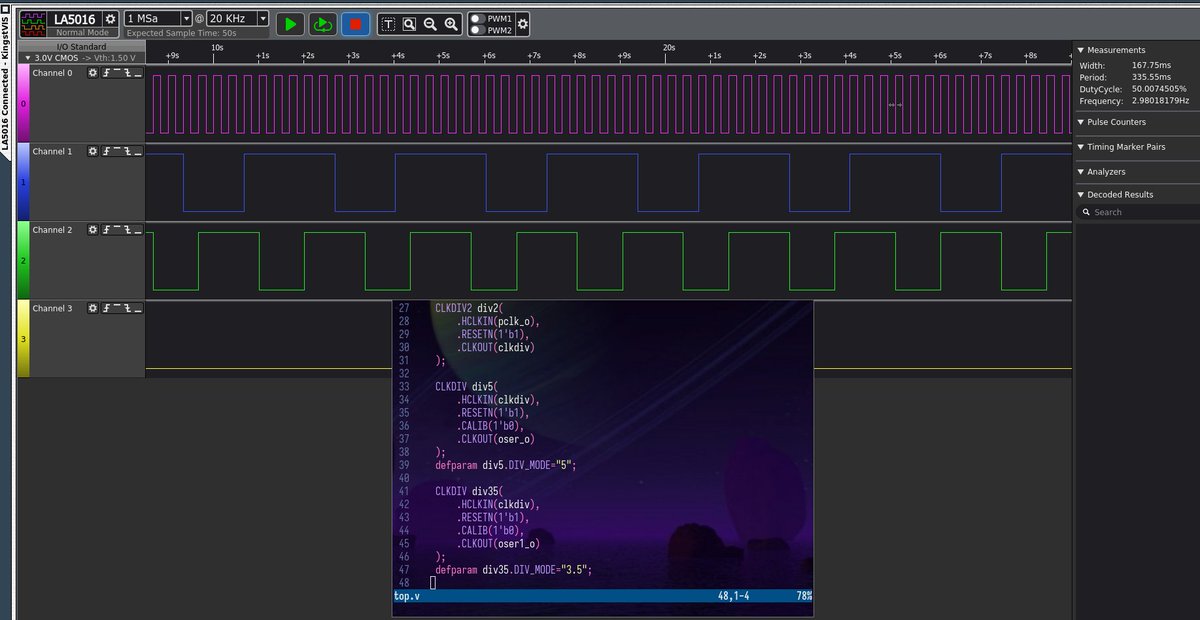

The original signal is 2.98 Hz, divided by 2 and then by 5—0.298 Hz, divided by 2 and then by 3.5—0.42571 Hz. #Apicula has learned to divide by all sorts of numbers by combining the CLKDIV2 and CLKDIV primitives🤣 #fpga

Built for what’s next. Experience our hardware at Electronica India 2026. Precision. Performance. Possibility. 📍 Booth H11.25 | Hall 11 #EdgeAI #EmbeddedSystems #FPGA #StartupIndia #Innovation #TechLife #OnTheRise #WeAreGrowing

What do you use to debug PCIe? Frequent reboots are required, and I use a headless Ryzen 3700X, accessed by SSH, with a static IP address. Can easily hook up 2 or 3 cards, parallel debuggin #Xilinx #FPGA GTP and GTX transceivers!

wolfSSL had an amazing visit to @RadionaOrg! Huge thanks to Goran Mahovlic and the team for the warm welcome and the opportunity to present wolfBoot at the OpenHardware Meet-up. Projects like the #ULX3S #FPGA + #ESP32 are truly inspiring! @crowd_supply @MouserElecEU @MouserElec

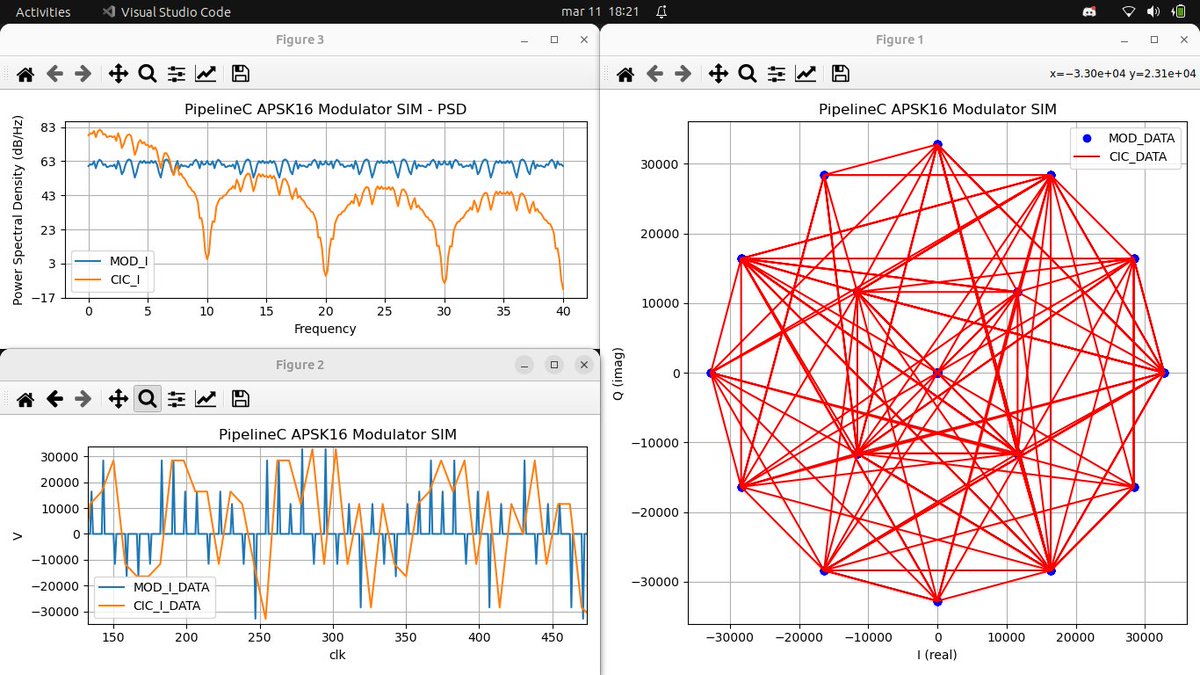

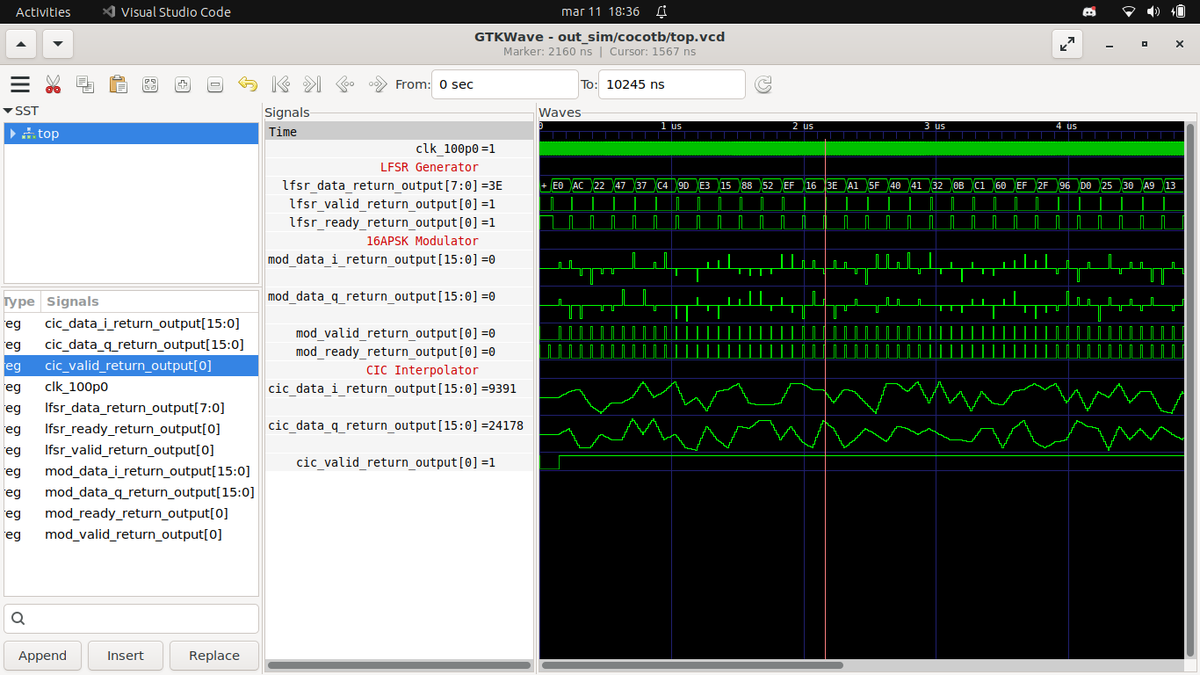

Developing one #16APSK Modulator on #FPGA using #PipelineCHDL ! Testbench Datapath: #LFSR -> APSK16 Map -> #CIC Filter -> out Simulation done with #ghdl + #cocotb, data plotted using #numpy and #matplotlib ! #dsp #sdr #HDL #ccsds #rf #psk #apsk #modem

FPGAs didn’t appear overnight, they’re the result of decades of innovation in digital logic ⚡ Revisit the moment that changed everything👉 bit.ly/4sTqDay #FPGA #innovation #eMagazine With sponsored articles from @Arduino, @ADI_News, @hammondmfg and @TXInstruments.

Built the hardware myself. KianV SoC v2 custom RISC V running on FPGA now booting Linux 7.0 systems engineer touched logic design it escalated :) #riscv #fpga #linux #opensource #kernelv7

Démarrez en développement #FPGA avec #Python & #LiteX grâce à notre liste de lecture du mois. Rendez-vous sans plus tarder sur connect.ed-diamond.com/liste-de-lectu… pour la découvrir. Bonne lecture !

Join Sundance at @embedded_world Exhibition&Conference! Don’t miss Chris Bowers’ technical session on March 10 at 14:00 for your chance to win a free SMT135‑C. Visit us at Hall 1 / Booth 1‑500 to see the new SMT135‑C Efinix FPGA board store.sundance.com/product/smt135… #fpga

New from Adiuvo Engineering ✈️ RTL-based environmental logging with: • Cmod S7 • PmodNAV • SPI master in pure RTL • UART @ 921,600 baud • Python visualization Accel, gyro, mag, pressure & temp — no processor required. Read it here: adiuvoengineering.com/post/microzed-… #FPGA #RTL

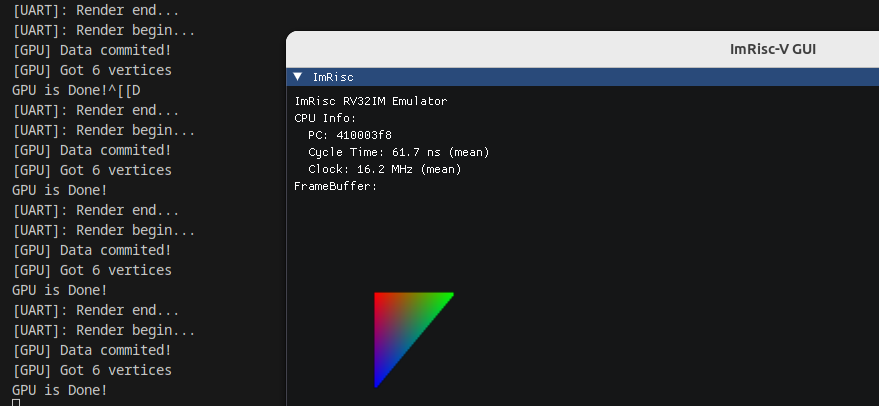

Made a #GPU for my #RISCV emulator... It works by using some memory mapped registers accessible by the cpu: Vert queue, commit / busy 1) tri list test 2) emulator debug log 3) "host" (riscv) code to draw Next goal is porting the mmio interface to the actual #FPGA desing...

Este sábado se celebró la RU13 de #MSX la afluencia fue menor a la habitualpor motivos laborales de varios habituales pero nos lo pasamos bien aunque se nos olvidó hacer más fotos 😂os pongo algunas de las cosas que pude fotografiar. #FPGA y #flashjacks: youtu.be/bEqtvGuaEW4

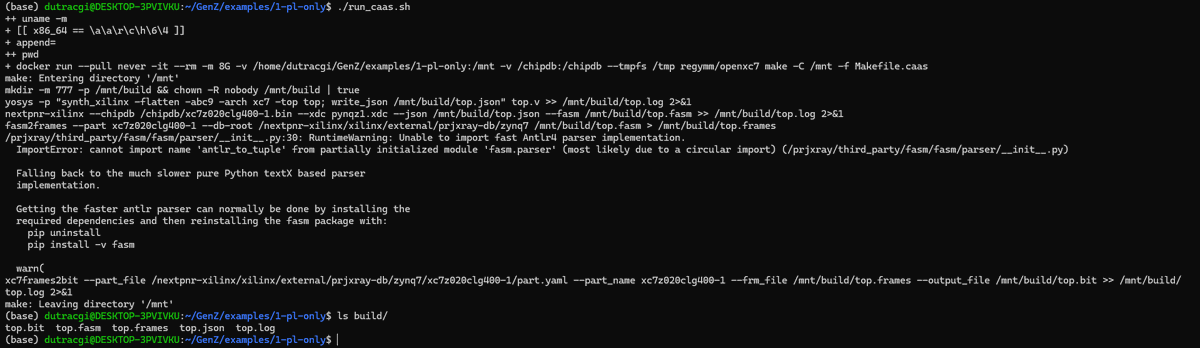

Nothing really special but I just built a Zynq bitstream using #OpenSource tools #GenZ ! Reference: github.com/regymm/GenZ/tr… #FPGA #ZYNQ #AMD #XILINX

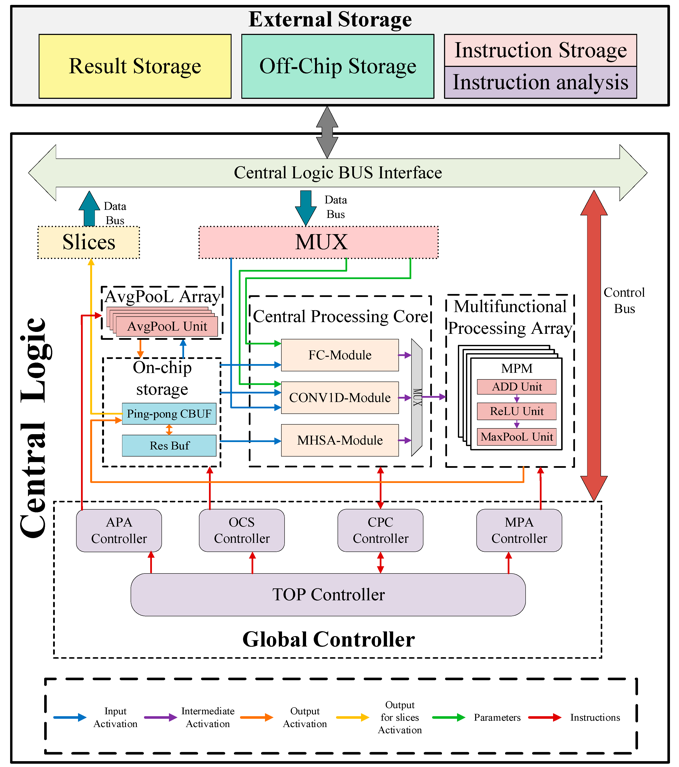

👉👉 1D-CNN-Transformer for #Radar Emitter #Identification and Implemented on #FPGA ✍️ Xiangang Gao et al. 🔗 brnw.ch/21wWFSE

Something went wrong.

Something went wrong.

United States Trends

- 1. Happy 420 N/A

- 2. #BuschAppleSweepstakes N/A

- 3. AJ Brown N/A

- 4. Good Monday N/A

- 5. #MondayMotivation N/A

- 6. Jim Ryan N/A

- 7. Trent Williams N/A

- 8. Discovery N/A

- 9. #MCMRechazadaPorLaDerecha N/A

- 10. #BostonMarathon N/A

- 11. Rodgers N/A

- 12. Patrick Muldoon N/A

- 13. Melrose Place N/A

- 14. Howie N/A

- 15. Marathon Monday N/A

- 16. Adam Schefter N/A

- 17. Will Howard N/A

- 18. Great Outdoors N/A

- 19. Brian Kelly N/A

- 20. The Atlantic N/A

![AdrianTonyII's tweet card. Welcome to Eden Adrian’s 29 current written and produced song list below 🎵 Music for the Soul *Tap to Listen […]](https://pbs.twimg.com/card_img/2045426484123172864/o6HsI1uB?format=jpg&name=orig)