#mrisc32 resultados da pesquisa

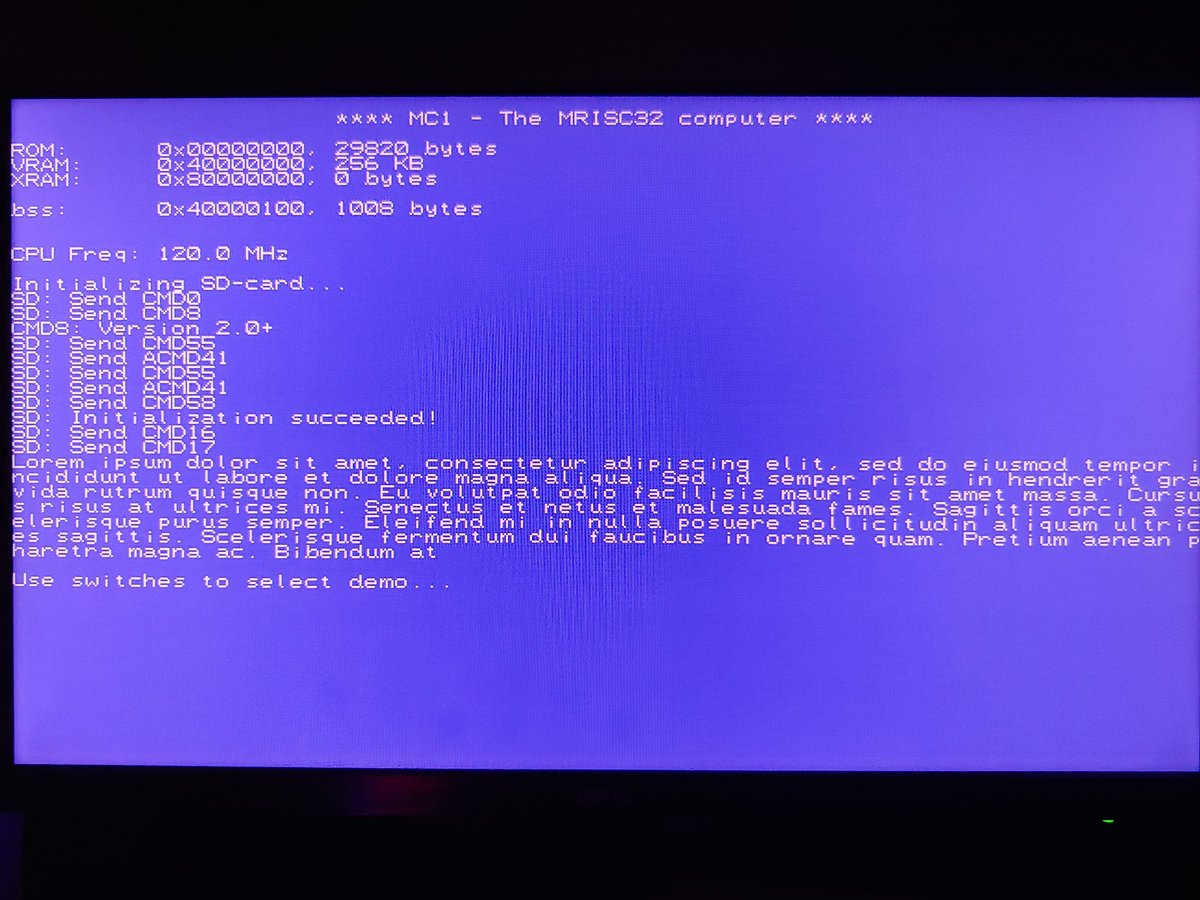

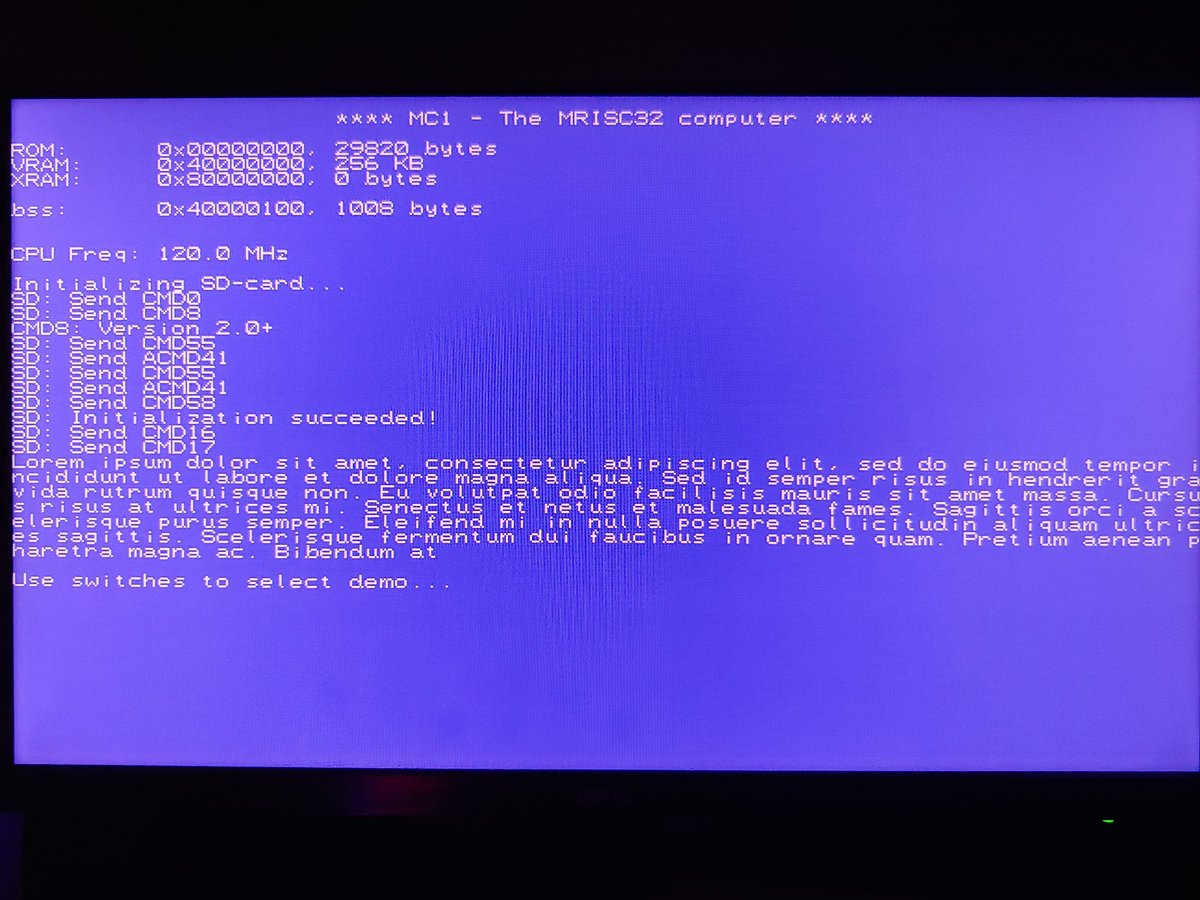

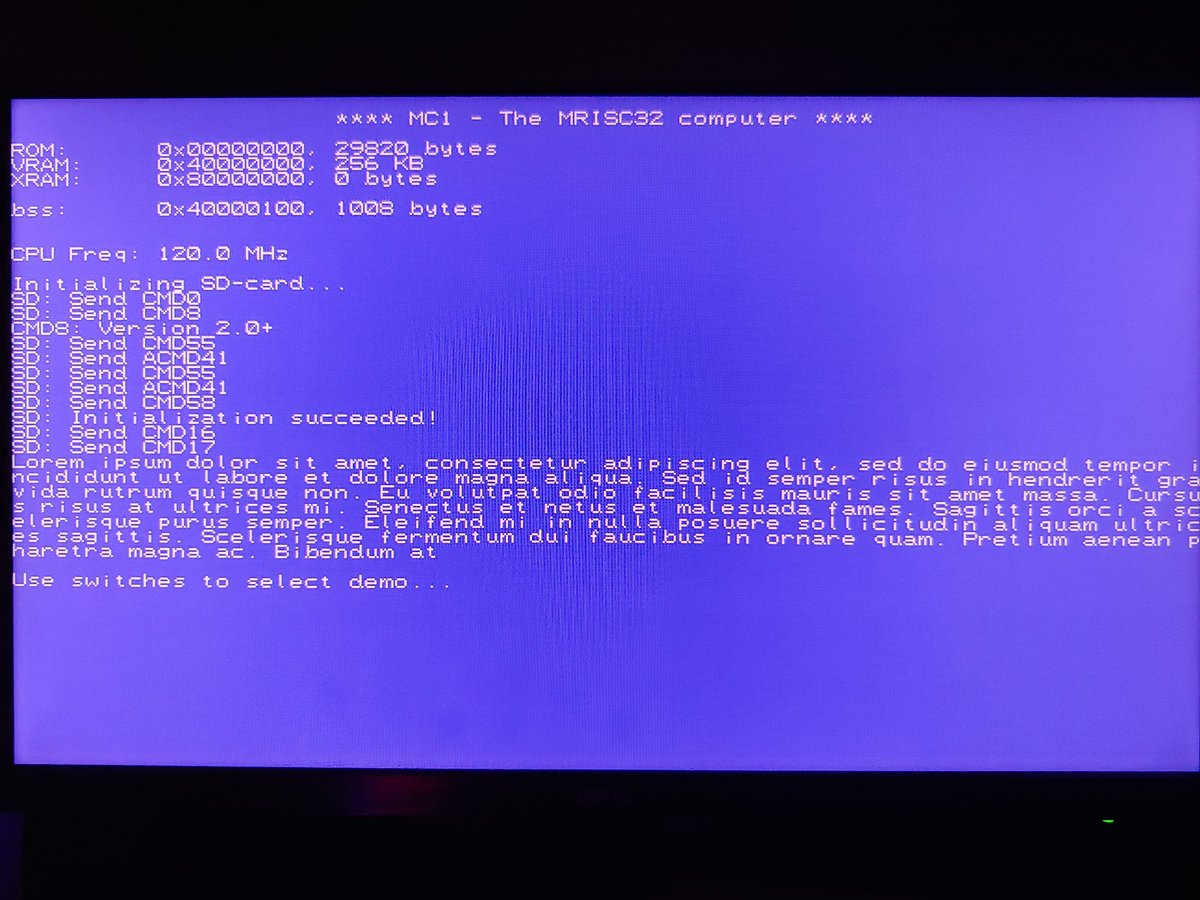

Success! The MC1 computer can now read from an SD card (first block of the card contains Lorem ipsum as ASCII). #MRISC32 #FPGA

Want to run #DOOM. Need something to run it on. ✔️ Develop new CPU ISA. ✔️ Write new GCC backend. ✔️ Implement CPU and VGA gfx in FPGA. ✔️ Write a minimal OS. ✔️ Port DOOM to the new CPU & platform. ✔️ Optimize rendering code. Now I can run DOOM 🤘 @romero #MRISC32 #FPGA

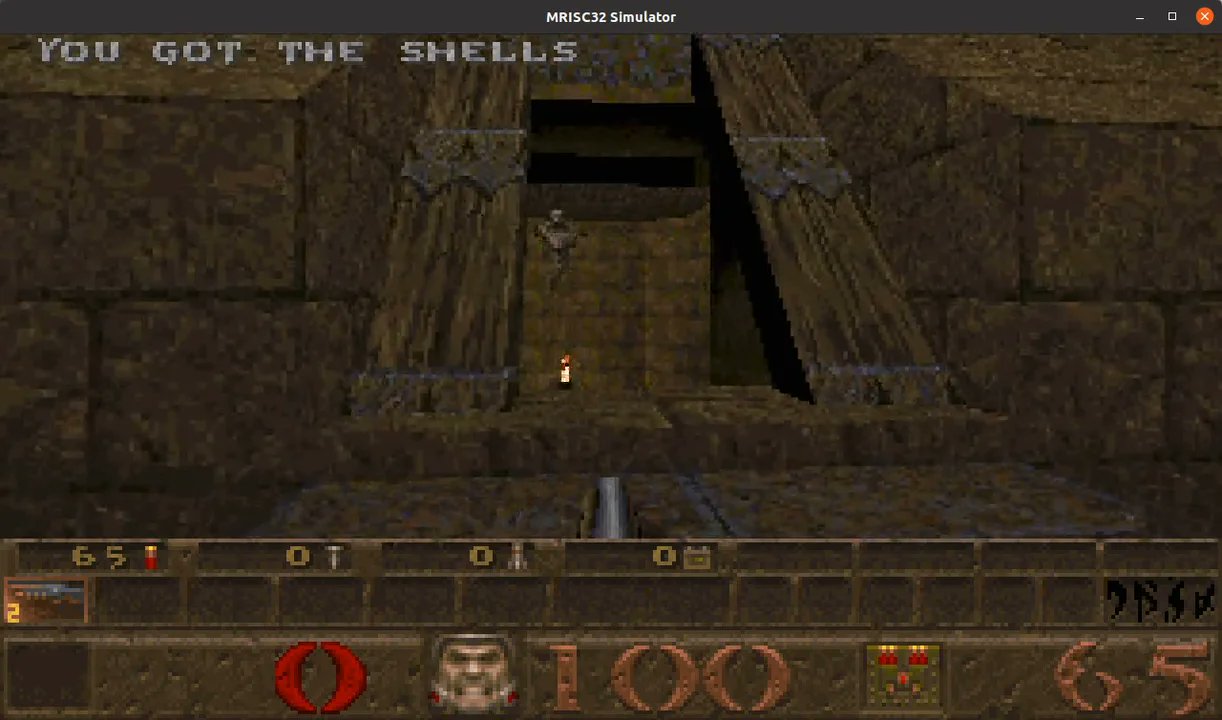

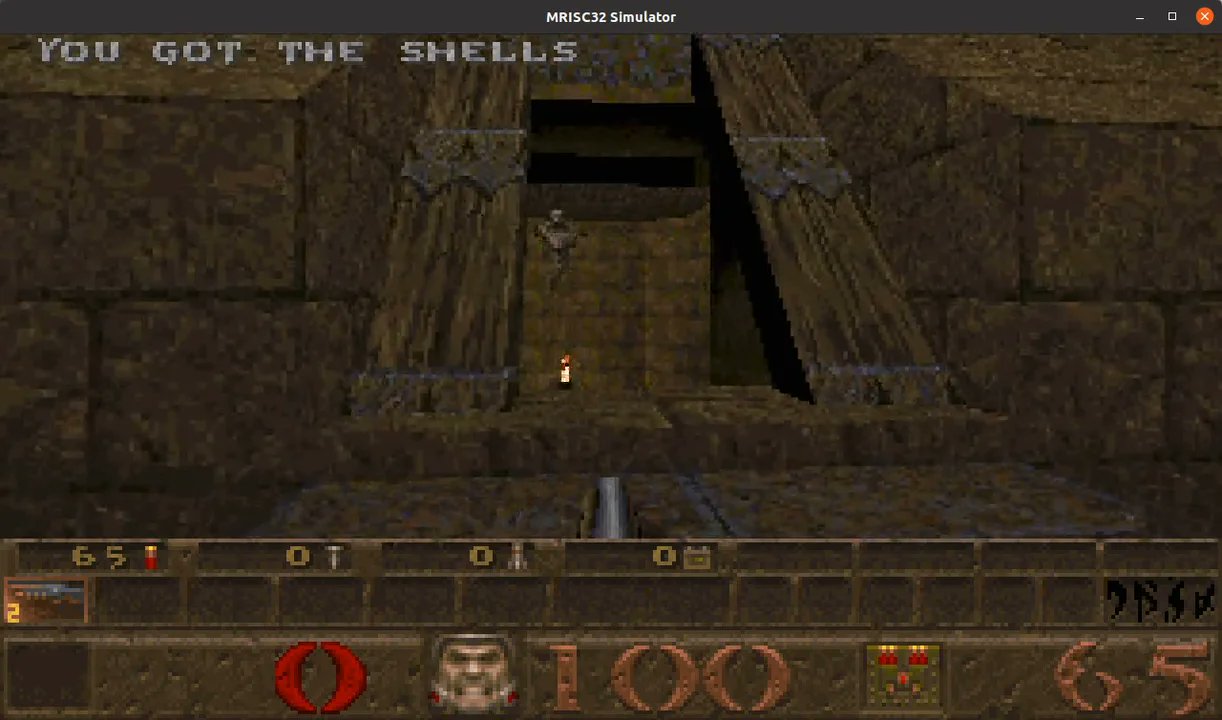

Making some progress on optimizing the #Quake2 software renderer for #MRISC32 (running in simulator so far). How it started: 632 frames, 272.2 seconds: 2.3 fps How it's going: 632 frames, 126.8 seconds: 5.0 fps Reducing the resolution to 320x160 makes it ALMOST fluent 😁

There we go. Finally! #DOOM running on my custom #MRISC32 based #FPGA computer, and at decent frame rates too (despite the very slow SDRAM, 7-10 cycles/access). With 256KB VRAM, 64MB SDRAM, GCC 13 + newlib, SD-card I/O + FAT filesystem, it can run other things than DOOM, too.

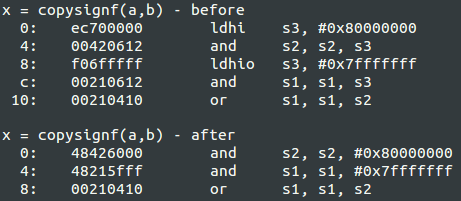

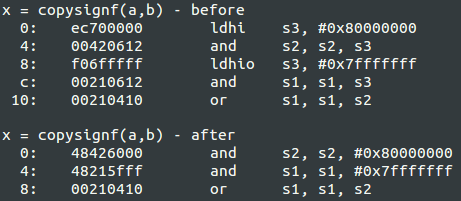

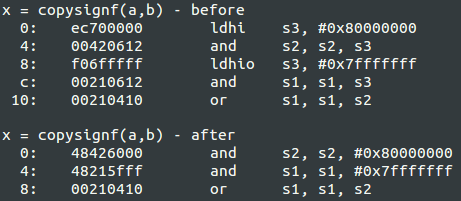

Introduced a new, smarter immediate value encoding for #MRISC32 instructions: 14-bit value plus a hi/lo bit (place value in upper/lower 14 bits of a 32-bit word). Useful for masks and such. Now the copysignf() code generated by GCC is 40% shorter 👍

Finally! #Doom compiling and running in the #MRISC32 simulator! Had to fix a few more #GCC (and Doom) bugs. The GCC toolchain is in a pretty good shape now. @ID_AA_Carmack Thanks for this magnificient piece of code - it's perfect for porting to new platforms!

MC1: A custom computer with a custom CPU based on a custom ISA bitsnbites.eu/mc1-a-custom-c… #fpga #mrisc32 #cpu

Not sure if it's the MRISC32 simulator, the GCC or the Doom that is acting up. It's doing something, but it's not exactly right. #MRISC32 #DOOM #cpu #GettingCloser

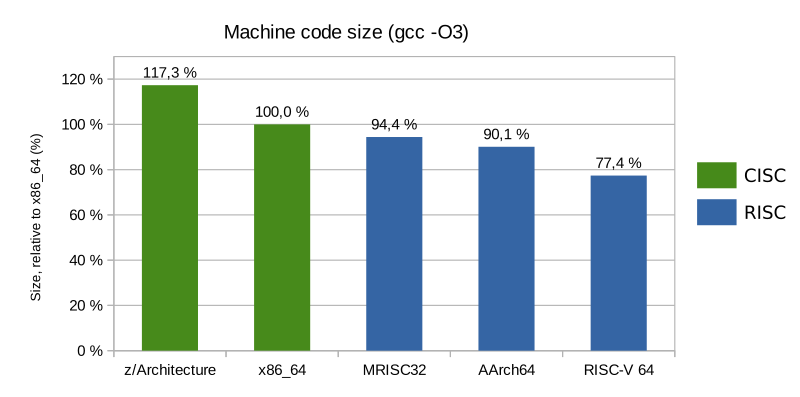

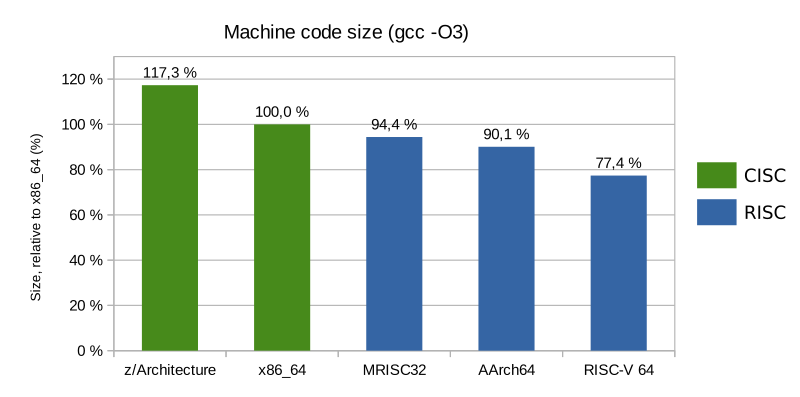

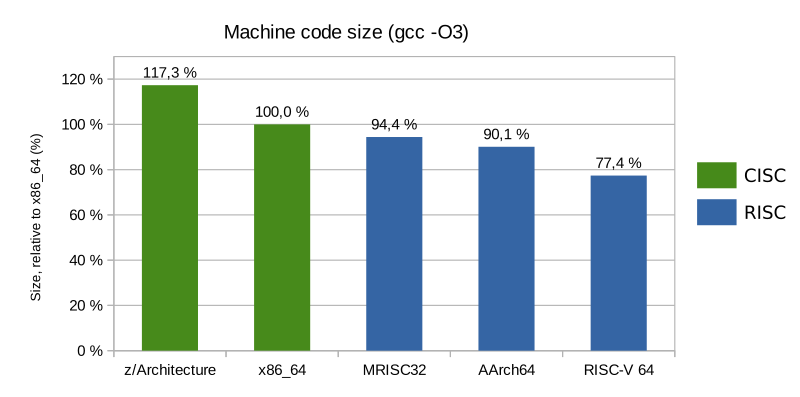

Some people still believe that CISC ISAs (x86, z/Arch) have denser machine code than RISC ISAs (#ARMv8 #RISCV #MRISC32). I beg to differ... bitsnbites.eu/cisc-vs-risc-c…

Okeey! Quake II builds, and runs in the MRISC32 simulator. ...although at painfully slow framerates (and not on the FPGA yet - possibly some memory/buffer-overrun issues?). Optimizations ... may now begin 😎 #FPGA #Quake2 #MRISC32

What to do with the pure-software bit-banging 2 MB/s SD card reader & boot loader of the #MRISC32 based MC1 #FPGA computer? Play an uncompressed version of the #BadApple video of course! (608x456x2bpp @ 30FPS) Boot code: gist.github.com/mbitsnbites/86…

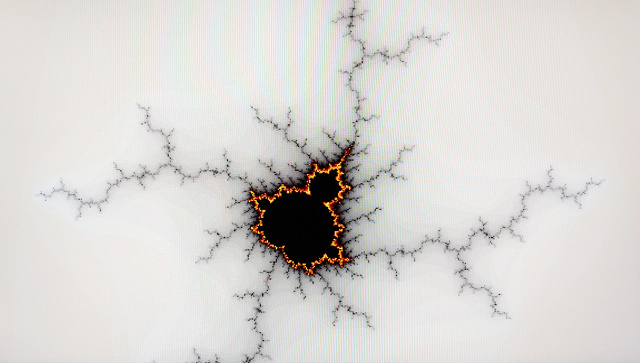

Trying out the MC1 SDK with a simple demo. Video capture from a Cyclone V FPGA. Nice art by @Fc_Arts_ . Bonus points if you recognize the 32x32 font 🙂 github.com/mrisc32/mc1-sdk #FPGA #MRISC32 #MC1 #retro #demoscene

Just discovered that @ffmpeg is VERY portable. The whole thing built out-of-the-box for my #MRISC32 CPU (no OS)! Great stuff for measuring instruction frequencies and tuning the compiler back end etc.

Did some optimizations of the Quake core rendering routines (using #MRISC32 vector instructions), and now it runs pretty smoothly in the simulator. vimeo.com/512692453

vimeo.com

Vimeo

Quake in the MRISC32 simulator

This is awesome! 🎉 Many thanks to @partouf and @mattgodbolt for helping with bringing #MRISC32 support to #CompilerExplorer !! godbolt.org/z/K679j9aon

The MRISC32 – A vector first CPU design bitsnbites.eu/the-mrisc32-a-… #Mrisc32 #Cpu

Getting started with MRISC32: bitsnbites.eu/getting-starte… #cpu #mrisc32 #programming #fpga

This is a project I started in 2018, #MRISC32. It inspired the new V16 ISA that I'm currently working on. V16 is not ready for DOOM yet, but rest assured that it will be one of the first programs I'll use for tuning and benchmarking the ISA 😉 See: bitsnbites.eu/the-mrisc32-a-…

This is a project I started in 2018, #MRISC32. It inspired the new V16 ISA that I'm currently working on. V16 is not ready for DOOM yet, but rest assured that it will be one of the first programs I'll use for tuning and benchmarking the ISA 😉 See: bitsnbites.eu/the-mrisc32-a-…

Want to run #DOOM. Need something to run it on. ✔️ Develop new CPU ISA. ✔️ Write new GCC backend. ✔️ Implement CPU and VGA gfx in FPGA. ✔️ Write a minimal OS. ✔️ Port DOOM to the new CPU & platform. ✔️ Optimize rendering code. Now I can run DOOM 🤘 @romero #MRISC32 #FPGA

Making some progress on optimizing the #Quake2 software renderer for #MRISC32 (running in simulator so far). How it started: 632 frames, 272.2 seconds: 2.3 fps How it's going: 632 frames, 126.8 seconds: 5.0 fps Reducing the resolution to 320x160 makes it ALMOST fluent 😁

Okeey! Quake II builds, and runs in the MRISC32 simulator. ...although at painfully slow framerates (and not on the FPGA yet - possibly some memory/buffer-overrun issues?). Optimizations ... may now begin 😎 #FPGA #Quake2 #MRISC32

Challenge: I'd like to see a RISC-V core running on an FPGA match the performance of the MRISC32-A1. (It shouldn't be terribly hard - the MRISC32-A1 is an in-order, single issue CPU, and I know there are good RISC-V cores out there) #riscv #fpga #mrisc32

Some people still believe that CISC ISAs (x86, z/Arch) have denser machine code than RISC ISAs (#ARMv8 #RISCV #MRISC32). I beg to differ... bitsnbites.eu/cisc-vs-risc-c…

...in my #MRISC32 ISA you have the SHUF instruction that readily does ARGB to/from BGRA, RGBA, ABGR etc in a single cycle. Works on scalar regs and vector regs alike. Not that it will be of any use to you, I guess 😉

There we go. Finally! #DOOM running on my custom #MRISC32 based #FPGA computer, and at decent frame rates too (despite the very slow SDRAM, 7-10 cycles/access). With 256KB VRAM, 64MB SDRAM, GCC 13 + newlib, SD-card I/O + FAT filesystem, it can run other things than DOOM, too.

The #MRISC32 simulator can now load ELF32 binaries directly (very convenient). github.com/mrisc32/mrisc3… I borrowed and hacked the ELF loader from github.com/BrunoLevy/lear… by @BrunoLevy01 (hope you don't mind), and it worked great!

Just discovered that @ffmpeg is VERY portable. The whole thing built out-of-the-box for my #MRISC32 CPU (no OS)! Great stuff for measuring instruction frequencies and tuning the compiler back end etc.

This is awesome! 🎉 Many thanks to @partouf and @mattgodbolt for helping with bringing #MRISC32 support to #CompilerExplorer !! godbolt.org/z/K679j9aon

Getting started with MRISC32: bitsnbites.eu/getting-starte… #cpu #mrisc32 #programming #fpga

Boom! 🎉 Pre-built versions of the #MRISC32 #GCC toolchain are now available for #Linux, #macOS and #Windows Feel free to try it out 🔧🔨 github.com/mrisc32/mrisc3…

github.com

GitHub - mrisc32/mrisc32-gnu-toolchain: A top level repository for building the MRISC32 GNU...

A top level repository for building the MRISC32 GNU toolchain - mrisc32/mrisc32-gnu-toolchain

Did some optimizations of the Quake core rendering routines (using #MRISC32 vector instructions), and now it runs pretty smoothly in the simulator. vimeo.com/512692453

vimeo.com

Vimeo

Quake in the MRISC32 simulator

Trying out the MC1 SDK with a simple demo. Video capture from a Cyclone V FPGA. Nice art by @Fc_Arts_ . Bonus points if you recognize the 32x32 font 🙂 github.com/mrisc32/mc1-sdk #FPGA #MRISC32 #MC1 #retro #demoscene

What to do with the pure-software bit-banging 2 MB/s SD card reader & boot loader of the #MRISC32 based MC1 #FPGA computer? Play an uncompressed version of the #BadApple video of course! (608x456x2bpp @ 30FPS) Boot code: gist.github.com/mbitsnbites/86…

Success! The MC1 computer can now read from an SD card (first block of the card contains Lorem ipsum as ASCII). #MRISC32 #FPGA

Wanna help out with #MRISC32? Make a minimal core for FPGA? Or a massively parallel (vector) one? Write an LLVM back end? mrisc32.bitsnbites.eu

Just in case you missed the glorious MC1/#MRISC32 demo video from the end of 2020, here it is (this time with correct gamma/brightness): vimeo.com/494653227 #FPGA #CPU #demoscene

Introduced a new, smarter immediate value encoding for #MRISC32 instructions: 14-bit value plus a hi/lo bit (place value in upper/lower 14 bits of a 32-bit word). Useful for masks and such. Now the copysignf() code generated by GCC is 40% shorter 👍

Success! The MC1 computer can now read from an SD card (first block of the card contains Lorem ipsum as ASCII). #MRISC32 #FPGA

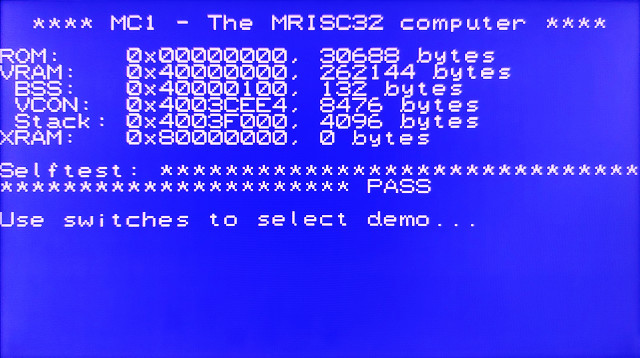

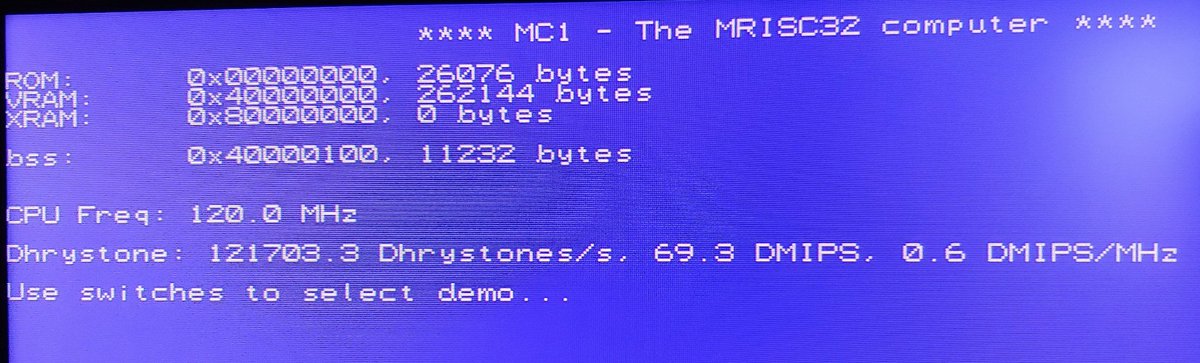

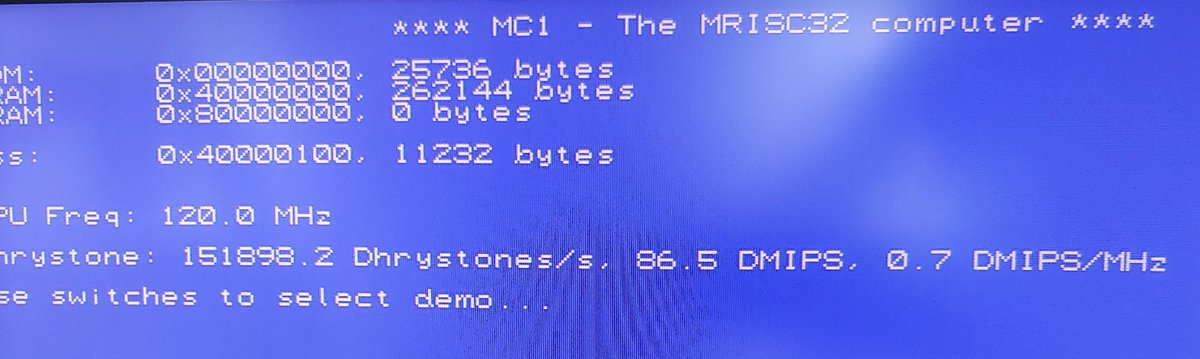

Happily running the MC1 #FPGA computer @ 120 MHz, after patching my broken DE0-CV board with a new oscillator via GPIO pins (off screen, wires to the right). github.com/mrisc32/mc1 #MRISC32 #CPU #VHDL #opensource

MC1: A custom computer with a custom CPU based on a custom ISA bitsnbites.eu/mc1-a-custom-c… #fpga #mrisc32 #cpu

Tried #Dhrystone on #MRISC32 today. Seeing 0.58 DMIPS/MHz was kind of disappointing. But expected, since Dhrystone is very memory + libc intensive. New goals: - Add instruction cache. - Optimize standard libc routines.

Introduced a new, smarter immediate value encoding for #MRISC32 instructions: 14-bit value plus a hi/lo bit (place value in upper/lower 14 bits of a 32-bit word). Useful for masks and such. Now the copysignf() code generated by GCC is 40% shorter 👍

Did some hand-optimizations to #MRISC32 libc routines (memcpy and friends) and gained 25% in Dhrystone performance. Now at 0.72 DMIPS/MHz. Next up: A silly 4KB instruction cache (that's enough to hold the Dhrystone+libc code).

Some people still believe that CISC ISAs (x86, z/Arch) have denser machine code than RISC ISAs (#ARMv8 #RISCV #MRISC32). I beg to differ... bitsnbites.eu/cisc-vs-risc-c…

Something went wrong.

Something went wrong.

United States Trends

- 1. Black Friday 324K posts

- 2. #FanCashDropPromotion N/A

- 3. #releafcannabis N/A

- 4. Good Friday 52.8K posts

- 5. #SkylineSweeps N/A

- 6. Mainz Biomed N.V. N/A

- 7. CONGRATULATIONS JIN 31.1K posts

- 8. #ENHYPEN 255K posts

- 9. #CurrysPurpleFriday 8,854 posts

- 10. ARMY Protect The 8thDaesang 58.5K posts

- 11. Clark Lea N/A

- 12. GreetEat Corp. N/A

- 13. 2025 MAMA Awards 593K posts

- 14. Third World Countries 44.9K posts

- 15. Cyber Monday 5,489 posts

- 16. Victory Friday N/A

- 17. Mr. President 21.4K posts

- 18. Message Boards N/A

- 19. RED Friday 8,640 posts

- 20. yeonjun 72.5K posts