#systemverilog ผลการค้นหา

Become SVA Ninja 2 hours | 46 students | July 2021 release 🆓 LINK => comidoc.net/udemy/sva-ninj… #Udemy #SystemVerilog

The #FPGA Programming Handbook Second Edition An essential guide to FPGA design for transforming ideas into hardware using #SystemVerilog and VHDL Frank #Bruno Guy #Eschemann

📢Job Opportunity for an FPGA Engineer in Los Angeles! We are working with a pioneering space technology company developing next-generation RF and satellite communication systems. Apply today! 👉buff.ly/evkMDwi #fpga #systemverilog #c++ #aerospace #losangeles

SystemVerilog Interface - get, set, go! 1 hour | 2526 students | June 2021 release 🆓 LINK => comidoc.net/udemy/sverilog… #Udemy #SystemVerilog

Do you find yourself copying and pasting chunks of Verilog/SystemVerilog code and wishing that you had created a new function or task? Our DVT IDE can do this at the click of a button: techdesignforums.com/practice/techn… #Verilog #SystemVerilog #CodeRefactoring #DVTIDE #DesignVerification

We are delighted to add SystemVerilog for New Designers to the Doulos self-paced training portfolio! This course is designed to help you gain the essential skills for FPGA and ASIC design. Find out more below! doulos.com/training/soc-d… #doulostraining #systemverilog

As of tomorrow, we'll be at @DVConEurope . If you're there, stop by and say hi! 👋 #VHDL #Verilog #SystemVerilog #EDAsoftware #EDA #DesignAutomation #IDE #HDL #Productivity

[Qu'est-ce que la Vérification SV-UVM ?] 🔍 Hugo, ingénieur FPGA chez ELSYS Design, vous l’explique en 30s. 👉 Envie d’aller plus loin ? Vous pouvez visionner notre webinar « Introduction à la vérification UVM » 🔗 lp.advans-group.com/introduction-m… #uvm #svuvm #SystemVerilog

⭐ ⭐ ⭐ ⭐ ⭐ Debashis De, Senior Member Technical Staff at Verific, uses Undo to quickly debug large SystemVerilog test cases and resolve customer-reported issues. Read what else he has to say here ➡️ hubs.ly/Q02TGbdh0 #cpp #cplusplus #systemverilog

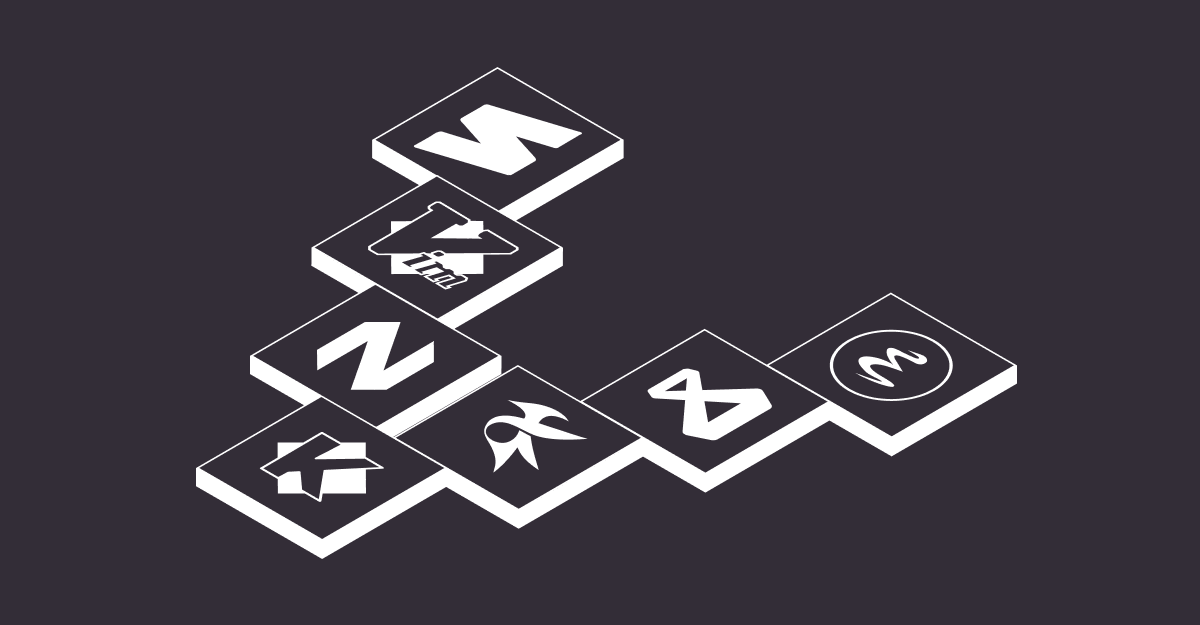

The #Verible language server brings #SystemVerilog code editing support to popular editors and #IDEs such as VS @code, #Vim, @Neovim, #Emacs, #SublimeText, #Kakoune & Kate. Read more for integration details: antmicro.com/blog/2023/02/i… @CHIPSAlliance @Google @sublimehq @kdecommunity

Check out NEW #DoulosKnowHow Tips available on our YouTube channel! Wire vs Variable Assignments in SystemVerilog: youtube.com/watch?v=Y3cvjL… Reviews wire and variable data types, and explains how not to make common mistakes when assigning values in #SystemVerilog.

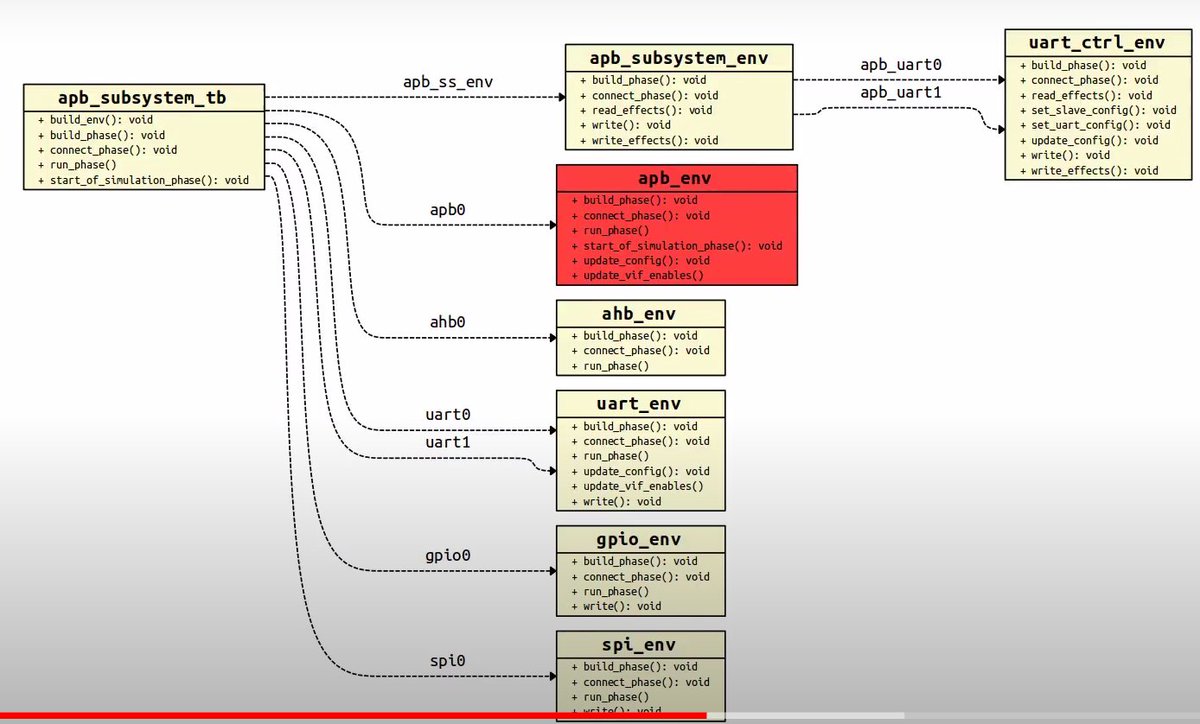

This video walks you through the DVT features that help you with OOP code. See how to employ them in the development and debugging of UVM testbenches. dvteclipse.com/demo-movies/ho… #oop #debugging #systemverilog

Tomorrow’s webinar: Become an SVA Expert in One Hour This #webinar explores the core principles necessary to understand and use #SystemVerilog Assertions, focusing on the aspects of SVA that are applicable to both formal verification and simulation. doulos.com/webinars/becom…

Our latest blog looks at the differences between ANSI and non-ANSI port declarations in #Verilog. Which do you prefer? Read the article: zurl.co/6784 #Verilog #SystemVerilog #EDAsoftware #EDA #DesignAutomation #IDE #HDL #Productivity

Are you looking to learn SystemVerilog, but don’t have any previous experience of using hardware description languages? SystemVerilog for New Designers is the perfect course for you! View course description: doulos.com/training/soc-d… #SystemVerilog #Training #DoulosTraining

Use #Verible's capabilities directly in your code editor with a language server and a dedicated VS @code extension and improve your #SystemVerilog #ASIC development process using #opensource tools: antmicro.com/blog/2023/02/i… @CHIPSAlliance @Google @Microsoft

Tomorrow’s #webinar: Maximize Design Productivity using Vivado ML with SystemVerilog ⏰ Europe & Asia: 10am (BST) & Americas: 10am (PDT) Explores the features of #SystemVerilog that are useful for RTL synthesis using #Vivado™ ML Editions from AMD...doulos.com/webinars/maxim…

Super annoying that #systemverilog strings don't behave like arrays. Want to get the number of characters? No `size()` for you, use `len()`... Want to find all occurrences of a character using `find()`? Tough luck...

It's so funny how the leading `'` in #SystemVerilog array assignment patterns really trips up AI assistants. I always get back stuff like `foo = '{ 0, 42, 100 }';` (note the `'` after the closing `}`).

Something went wrong.

Something went wrong.

United States Trends

- 1. The BONK 83.5K posts

- 2. Good Thursday 30.6K posts

- 3. #thursdayvibes 1,611 posts

- 4. Happy Friday Eve N/A

- 5. #PiratasDelImperio 1,136 posts

- 6. Godzilla 25.1K posts

- 7. Usher 4,122 posts

- 8. Shaggy 2,497 posts

- 9. Trey Songz N/A

- 10. JUNGKOOK FOR CHANEL BEAUTY 136K posts

- 11. Dolly 14.7K posts

- 12. #ThursdayThoughts 2,019 posts

- 13. Doug Dimmadome 14.9K posts

- 14. Lupin 3,853 posts

- 15. Oracle 22.1K posts

- 16. Confessions 5,034 posts

- 17. #PutThatInYourPipe N/A

- 18. Zane 6,411 posts

- 19. Code Pink 3,045 posts

- 20. Ukraine and Israel 6,281 posts