Arduissimo

@arduissimo

RISC-V 32-Bit project. System Hyper Pipelining, Dynamic Multithreading, Wave-Pipelining, MultiCore Arduino on FPGA and ASIC, Virtual Peripherals.

You might like

It is with great pleasure to announce the release of the open source Arduissimo project on github. Open source MPSoC running 620 MIPS (CHStone) of RISC-V (RV32iMC) programs on the ARTY board (XC7A35T). #riscv #shp #cubev github.com/cloudxcc/Ardui…

How about giving this one a quick sponno, or just a star if you're feeling alternative? A fully open source Rust EtherCAT controller😎 github.com/ethercrab-rs/e…

| ̄ ̄ ̄ ̄ ̄ ̄ ̄ ̄ ̄ ̄ ̄| | Normalize sponsoring | | open-source projects! | |___________| \ (•◡•) / \ / —— | | _| |_

Oh, the NIST PQC Draft standard PDFs are out! FIPS 203 ipd: Kyber (ML-KEM): csrc.nist.gov/pubs/fips/203/… FIPS 204 ipd: Dilithium (ML-DSA) csrc.nist.gov/pubs/fips/204/… FIPS 205 ipd: SPHINCS+ (SLH-DSA): csrc.nist.gov/pubs/fips/205/…

Made some updates to my #riscv in Spade :) Now it has memory mapped HDMI output, runs rust, and uses Spade's dynamic pipelines for stalling and flushing. It is also the first Spade project to not use a Verilog top module. No more error prone Shims🎉

I was looking for inspirations for my wave-pipelining RISC-V project, and found a paper on wave-pipelining in superconducting quantum computing, well, why not. www2.ece.rochester.edu/users/friedman…

I posted a paper on arXiv that shows that GPT-4 has a deep and comprehensive understanding of mathematical logic and functional languages. But this paper has a twist. arxiv.org/abs/2305.12196

2023 Free Silicon Conference (FSiC) will take place in Paris (Sorbonne) on July 10,11,12 2023. Submissions are open. wiki.f-si.org/index.php/FSiC…

Been there. It's actually very similar. Unfortunately, as designs get larger, these solutions tend to face the classic memory wall far too quickly. But certainly the right direction in an exciting field of research. ieeexplore.ieee.org/document/74991…

Researchers have developed an architecture for parallel RTL simulation which leverages a static bulk-synchronous parallel execution model that virtually eliminates dynamic overheads of RTL simulation through static scheduling. arxiv.org/pdf/2301.09413…

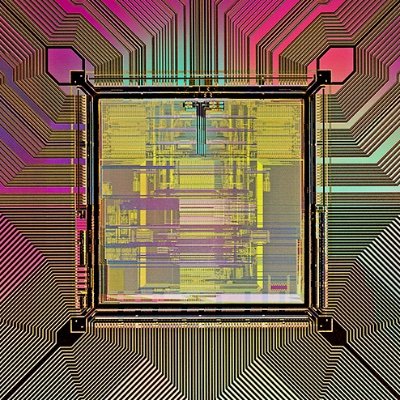

It's a TAPEOUT !!! I have been informed, that my ASIC is accepted by @Efabless (MPW-8). The CUBE-V #RISCV CPU uses WAVE-PIPELINING and dynamic-interleaved multi-threading. A 25-year-old dream comes true. Thanks @Google for sponsorship + all the many helpers on Slack @OpenROAD_EDA

The 'Myths' paper is out: Satoshi Matsuoka, Jens Domke, Mohamed Wahib, Aleksandr Drozd, Torsten Hoefler. "Myths and Legends in High-Performance Computing" arxiv.org/abs/2301.02432" undergoing peer review. Hopefully the community will be engaged in yes/no discussions on Twitter!

I asked ChatGPT to write a script for a video on "The importance of open hardware (from a fablab perspective)". Then I used pictory to generate a video with auto-generated voice-over. Here is the result. youtu.be/PstbcRCCWrc

Awesome new open source asynchronous design flow released. Aaahhhh, so many interesting projects, so little time. github.com/asyncvlsi/

I really miss the days when Alex created the excellent real-time, ad hoc summaries of RISC-V events. #RISCV ambassadors, attendees, OS-enthusiasts, please share some exciting takeaways from last week's #RISVsummit ? What happened that wasn't covered by all that marketing slides?

So the execution order of a C++ function call is right to left ? a ( b(...), c(...) ) It is always the case that c() is evaluated before b() ? Is it a specified right to left presedence ?

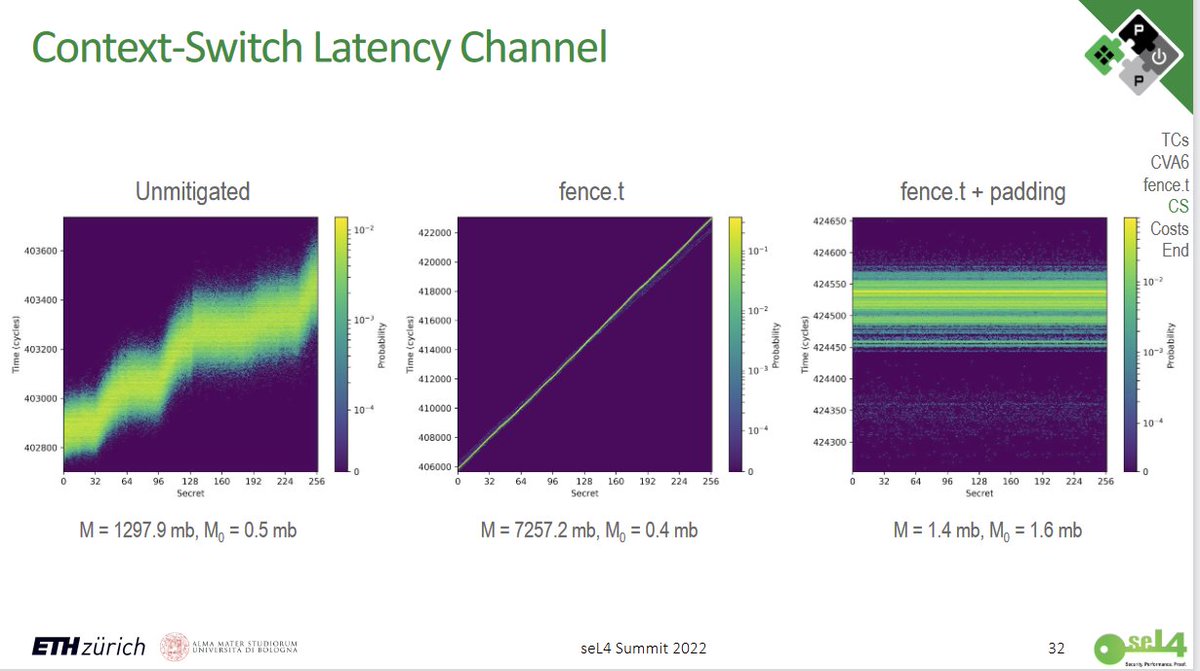

Would you like to learn more about fence.t instruction? Nils's @niwist slides from sel4 Summit presenting this novel RISC-V instruction that clears the processor's microarchitectural state are now online as well: sel4.systems/Foundation/Sum…

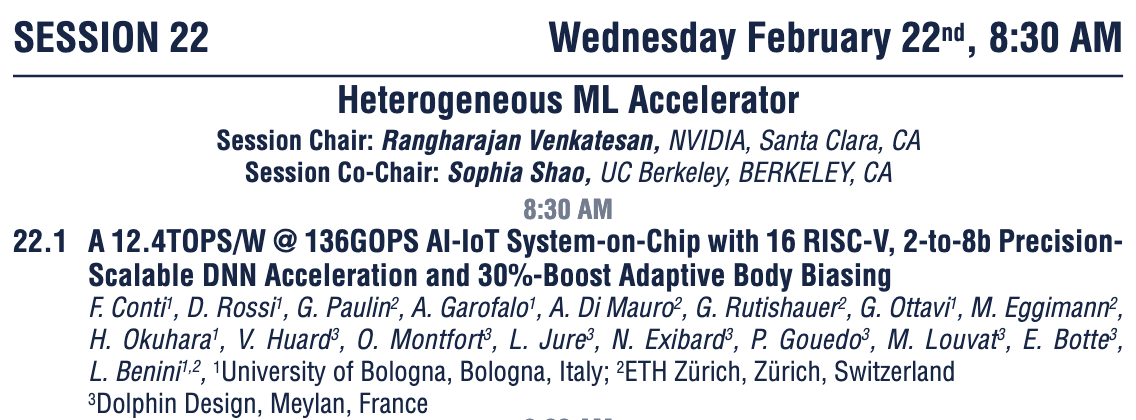

As the #ISSCC23 program is out, it's my pleasure to announce our work on #Marsellus will be in the Heterogeneous ML Accelerator session! It is a @pulp_platform SoC with 16 #riscv cores and a flexible DNN accel for 12.4TOPS/W@136 GOPS AI. @duav_red @GiannaPaulin @LucaBeniniZhFe

United States Trends

- 1. Cloudflare 32.8K posts

- 2. Cowboys 74.4K posts

- 3. #heatedrivalry 30.9K posts

- 4. Happy Farmers 2,162 posts

- 5. Warner Bros 35K posts

- 6. LeBron 116K posts

- 7. Wizkid 184K posts

- 8. Jake Tapper 45.3K posts

- 9. Pickens 15.4K posts

- 10. Lions 94.1K posts

- 11. rUSD N/A

- 12. fnaf 2 28.3K posts

- 13. Paramount 22.3K posts

- 14. Shang Tsung 36.9K posts

- 15. Gibbs 21.3K posts

- 16. #powerforce N/A

- 17. Davido 102K posts

- 18. The Gong Show N/A

- 19. scott hunter 7,088 posts

- 20. Cary 48.7K posts

You might like

-

Zip CPU

Zip CPU

@zipcpu -

OLIMEX Ltd

OLIMEX Ltd

@Olimex -

BeagleBoard.org

BeagleBoard.org

@beagleboardorg -

Elektor

Elektor

@Elektor -

Sigasi

Sigasi

@Sigasi -

Future Electronics

Future Electronics

@FutureElec -

ian @ Dangerous Prototypes

ian @ Dangerous Prototypes

@dangerousproto -

Pololu

Pololu

@Pololu -

Digi XBee

Digi XBee

@XBeeWireless -

element14 Electronics

element14 Electronics

@element14_Avnet -

Tim 'mithro' Ansell

Tim 'mithro' Ansell

@mithro -

WaveDrom

WaveDrom

@wavedrom -

PULP Platform

PULP Platform

@pulp_platform -

Edmund Humenberger

Edmund Humenberger

@ico_TC -

Massimo Banzi

Massimo Banzi

@mbanzi

Something went wrong.

Something went wrong.