Zip CPU

@zipcpu

FPGA design engineer and blogger, placing particular emphasis on test and formal verification

You might like

Wow, lots of new twitter followers just joined. Welcome! Just to give you an opportunity to get to know me and the ZipCPU blog, here's a bit about me and what you can expect here: zipcpu.com/blog/2018/10/0… Again, welcome!

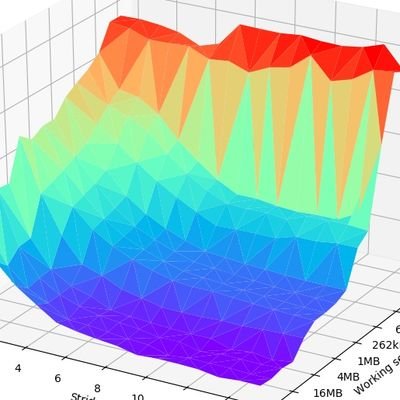

How bad can clock muxing get? This is just two of six mux trees. Notice the wide clock muxes as well. Those are actually mux trees. Ugly? Wait 'till it needs to meet timing.

ASIC designers need to worry about clock gates, yes. The ASIC design I'm currently working with is having struggles with clock muxes--don't forget those as well. A second design on my desk has ... way too many muxed clocks for a simple IO controller. I like things simpler.

ASIC designers need to worry about clock gating while FPGA designers just hit compile crazy world out there

get into FPGAs. they’re not as hyped as AI or robotics, but they’re the hidden backbone of both. you want speed? determinism? ultra-low latency? hardware-level parallelism? that’s FPGA territory. every serious system; autonomous vehicles, defense tech, high-frequency trading,…

United States Trends

- 1. Raindotgg 2,244 posts

- 2. Sam Houston 1,189 posts

- 3. Lubin 5,330 posts

- 4. Louisville 14.3K posts

- 5. Oregon State 4,668 posts

- 6. #GoAvsGo 1,493 posts

- 7. Batum N/A

- 8. Nuss 5,661 posts

- 9. Emmett Johnson 2,306 posts

- 10. UCLA 7,740 posts

- 11. Miller Moss 1,200 posts

- 12. #Huskers 1,074 posts

- 13. #FlyTogether 1,868 posts

- 14. #MASHLE 1,320 posts

- 15. Oilers 4,679 posts

- 16. #Toonami 1,934 posts

- 17. Bama 13.7K posts

- 18. Lateef 2,275 posts

- 19. Nikki Glaser N/A

- 20. Brohm 1,145 posts

You might like

-

Enjoy Digital

Enjoy Digital

@enjoy_digital -

Charles Eric LaForest, PhD

Charles Eric LaForest, PhD

@elaforest -

Edmund Humenberger

Edmund Humenberger

@ico_TC -

OpenHW Foundation

OpenHW Foundation

@OpenHWFdn -

RISC-V International

RISC-V International

@risc_v -

YosysHQ

YosysHQ

@YosysHQ -

Antmicro

Antmicro

@antmicro -

CHIPSAlliance

CHIPSAlliance

@CHIPSAlliance -

Flux

Flux

@WillFlux -

Sipeed

Sipeed

@SipeedIO -

Tim 'mithro' Ansell

Tim 'mithro' Ansell

@mithro -

Matthew Venn

Matthew Venn

@matthewvenn -

logic destroyer

logic destroyer

@splinedrive -

SiFive

SiFive

@SiFive -

Luke Wren @[email protected]

Luke Wren @[email protected]

@wren6991

Something went wrong.

Something went wrong.