내가 좋아할 만한 콘텐츠

Trying to decide whether to use my final 2x STM32L4s for my first prototype or instead use some of my STM32F0s knowing that I will probably need an M4 down the line and I can buy neither chip in the foreseeable future either way. It's like the trolley problem for chips.

I think I caught the ISS on Friday night with some long exposures over Clear Lake, California

I thought I'd finally found reason to put a chip at 45˚, but no, it's still an inferior orientation

Waiting on parts so why not do some mechanical design

Chose an STM32 model for a new design last weekend based on DigiKey having 1000+ in stock - finished the design today and they're all sold out🤦♂️Should've pulled the trigger last week

Even using @oshpark's 6 layer service, I find myself most limited by no blind/buried vias and no via in pad when having to miniaturise a design. There just isn't space between components. Still need to optimise the placement before serious routing can begin.

Spent hours debugging an oscillating opamp - turned out to be the LDO was unstable😩

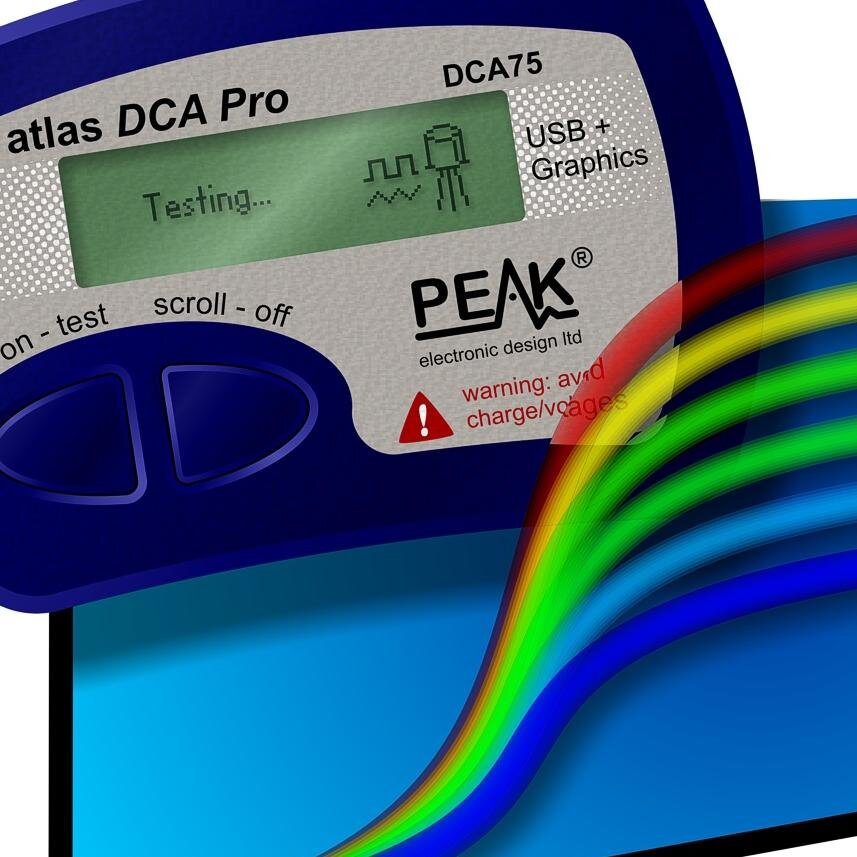

Enjoy a video of the magnetic field when two attracting magnets meet - simulated using FEMM

Got 2kg of 3mm black PLA filament by accident (wanted 1.75mm). If anyone in San Francisco wants it, let me know. Don't want to throw it away.

United States 트렌드

- 1. Raiders 82.7K posts

- 2. #WWERaw 174K posts

- 3. Cowboys 52K posts

- 4. Pickens 21.4K posts

- 5. Gunther 22.2K posts

- 6. #WickedForGood 8,571 posts

- 7. Geno 15.9K posts

- 8. #Dragula N/A

- 9. Chip Kelly 2,409 posts

- 10. Jeanty 7,091 posts

- 11. #GMMTV2026 254K posts

- 12. Pete Carroll 3,548 posts

- 13. Jlexis 8,552 posts

- 14. Grok 4.1 32.1K posts

- 15. Roman 76.2K posts

- 16. Sigourney N/A

- 17. Mark Davis 1,537 posts

- 18. Becky 56.8K posts

- 19. Brock 21.8K posts

- 20. Ceedee 11.2K posts

Something went wrong.

Something went wrong.