#foveros search results

Great interview with @RamuneTunes of @intel, discussing packaging technologies, the future research of tech like #Foveros, Intel's chiplet strategy, enabling a chiplet ecosystem, and the direct importance of DTCO in an optimised product portfolio. Transcription soon. #IEDM2019

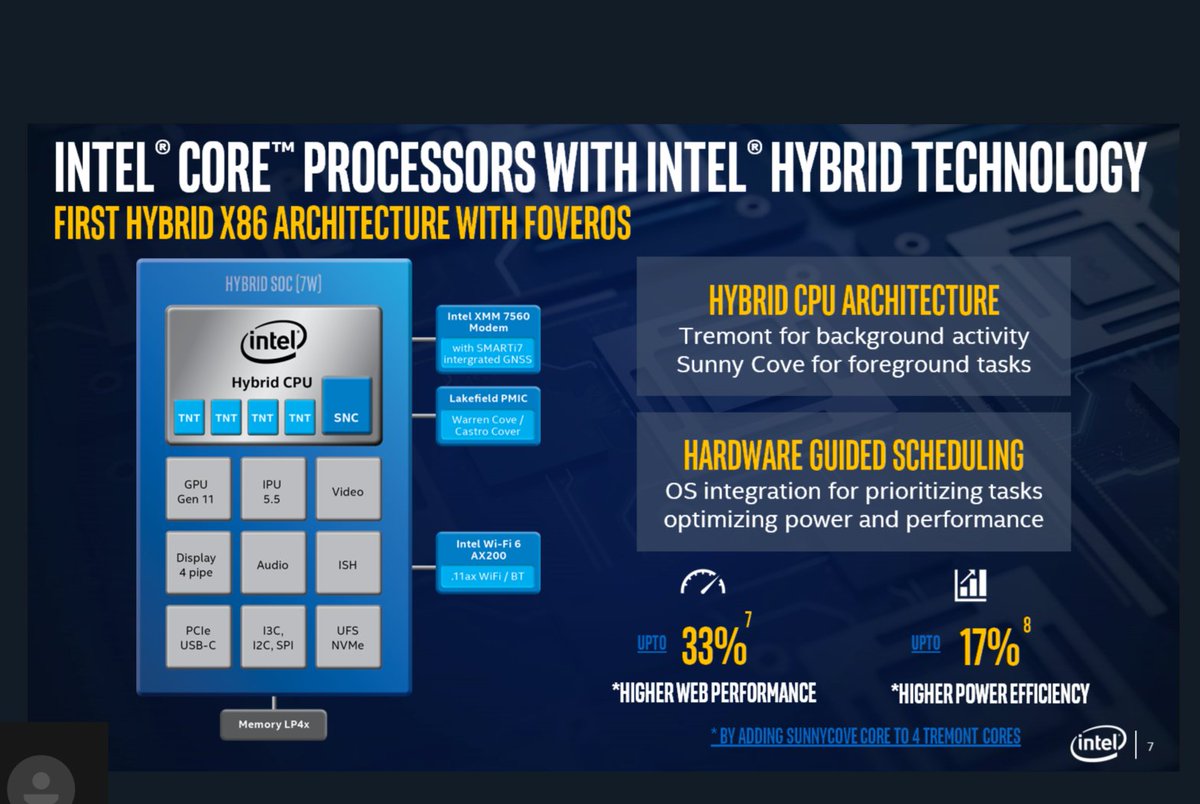

Nice article by @david_schor with some more details on #Lakefield – the base and compute die, the #Foveros Die Interface (FDI). Interesting move by Intel not supporting HT on the Sunny Cove core and disabling AVX (in any way?) to maintain full ISA compatibility across all cores.

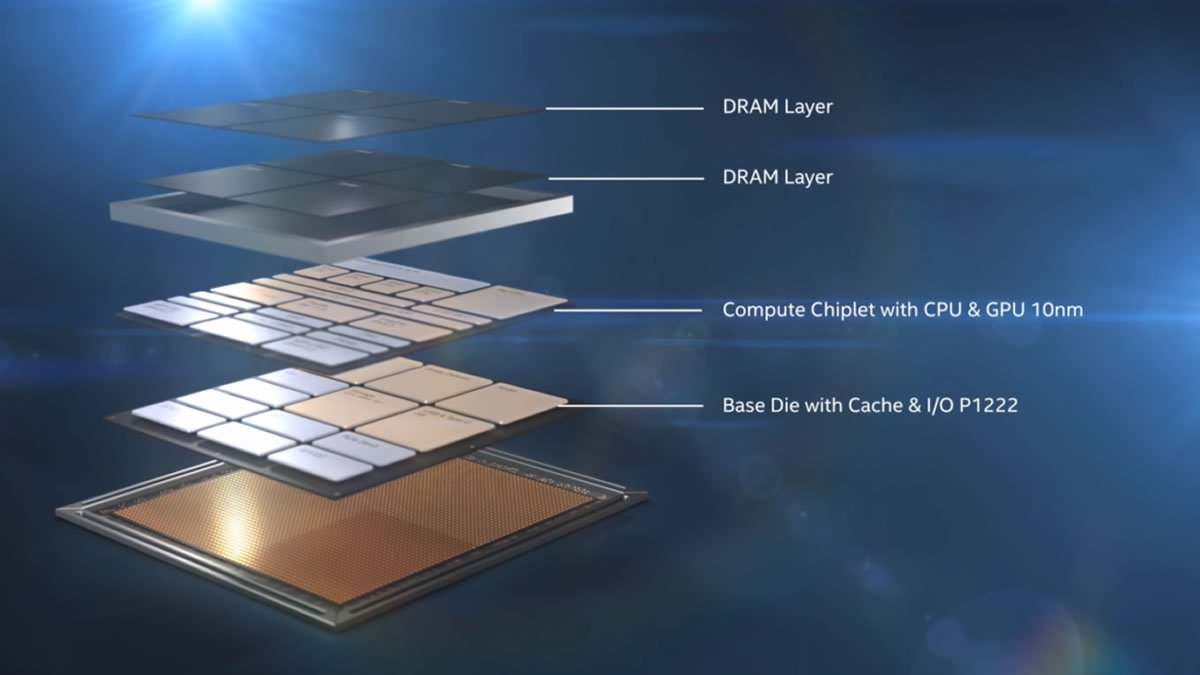

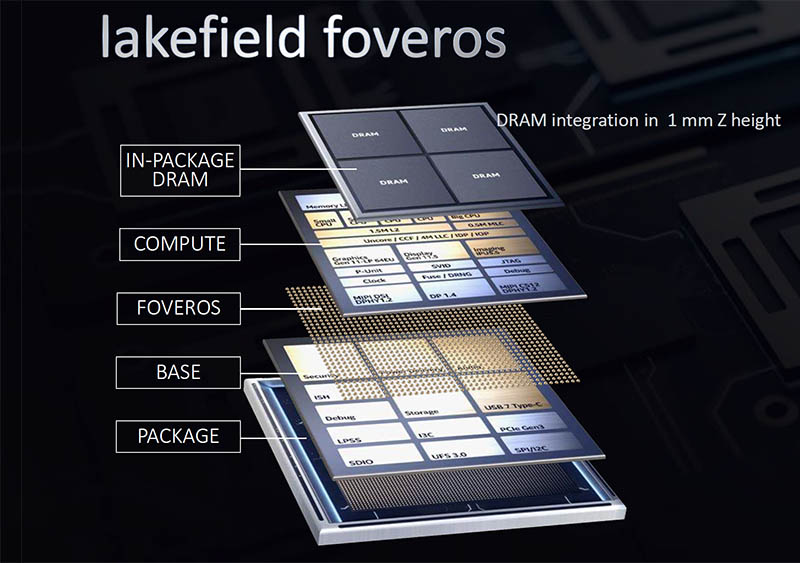

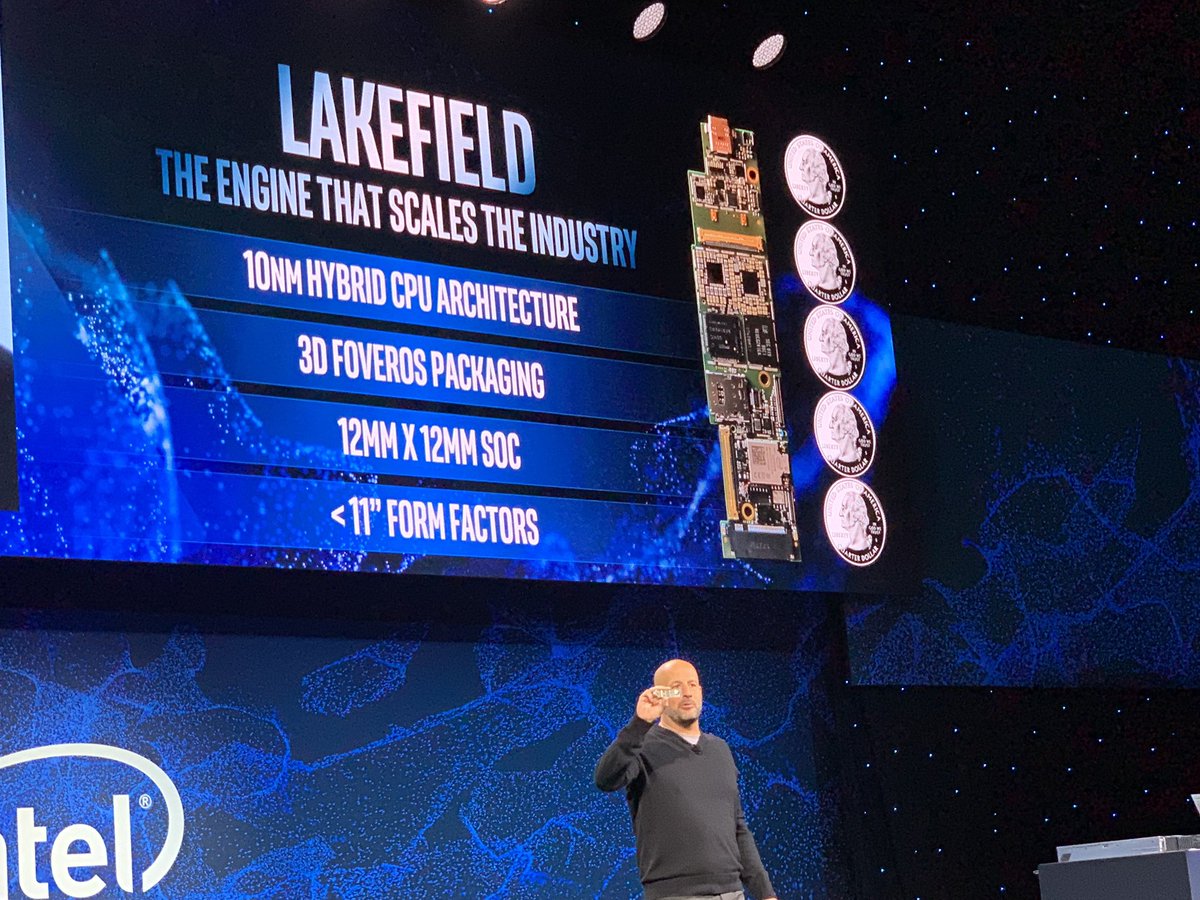

A look at Lakefield: Intel's new mobile-class heterogeneous penta-core SoC. Built using two dies 3D-stacked using Intel's Foveros packaging technology and integrating close to 5 billion transistors, here are the full details: #10nm #22nm #3DIC #x86 fuse.wikichip.org/news/3417/a-lo…

Intel Lakefield Hybrid SoC detailed. 10nm 3D Foveros with compute, an I/O die, and in-package DRAM. This even brings large Sunny Cove and small Tremont cores to a single SoC. Chiplets are the future. servethehome.com/intel-lakefiel… @IntelBusiness #Foveros

With Foveros and Sunny Cove, Intel sets out to build a new generation of 3-D chips siliconangle.com/2018/12/12/fov… via @SiliconANGLE #Intel #Foveros #SunnyCove

The silicon marvel of packaging: Intel #Lakefield. In some ways, the processor was ahead of its time, but the technology was also simply wrongly positioned as a product. I talked with some of the #Foveros Engineers last year, they were full of pride for what they have achieved.

Intel's announcement of #Foveros helps the company to navigate the competitive landscape more effectively and gives them an opportunity to innovate in different places at different speeds. Im excited to see this productized and how it'll stack up to the competition (pun intended)

When combined with our world-class process technologies, new packaging capabilities will unlock customer innovations and deliver the computing systems of tomorrow. #Foveros intel.ly/2JpolwY

By stacking high-performance logic chips for the first time, Intel #Foveros technology opens a world of possibilities for smaller, more efficient, more powerful devices. intel.ly/2FNgR6E

Will we get some more detailed informations on the Core i5-L16G7 / Core processor with Intel Hybrid Technology? From my point of view there is still a white spot when it comes to some detailed product information and Intel Ark does not yet list the processor. #Lakefield #Foveros

The launch of the Galaxy Book S powered by our new @Intel Core processor with Intel Hybrid Technology is an example of our united vision to deliver new computing experiences of the future. #IamIntel #Samsung news.samsung.com/global/experie…

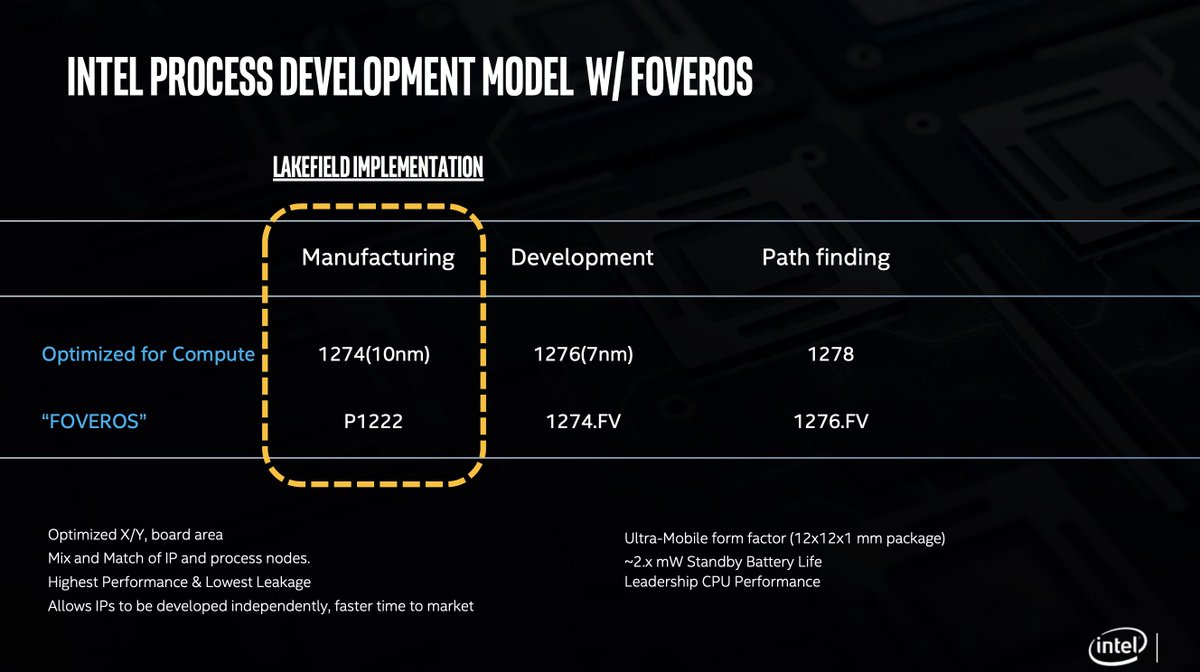

On future Lakefield generations: For the next generation, Intel wants to manufacture the base die in 10 nm #Foveros (P1274.FV). The compute die is supposed to change to 7 nm (P1276). The generation after next is 7 nm (P1276.FV) for the base and 5 nm (P1278) for the compute die.

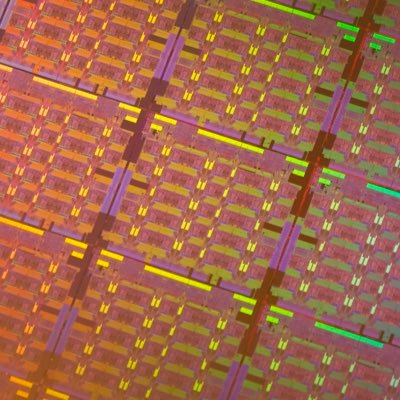

A test package of #MeteorLake with #Foveros wafer level assembly. It’s a test package, because it would probably not be economically feasible that way.

#TodaysTips🗒️ 🏇Wexford➡️1st race➡️12.50pm 🏇Galway➡️1st race➡️1.05pm Jumps action at both @WexfordRacecour and @Galway_Races this afternoon. Don't get caught out by the earlier start times! Our preview of both meetings is here👇#Foveros bit.ly/2JxUTpW

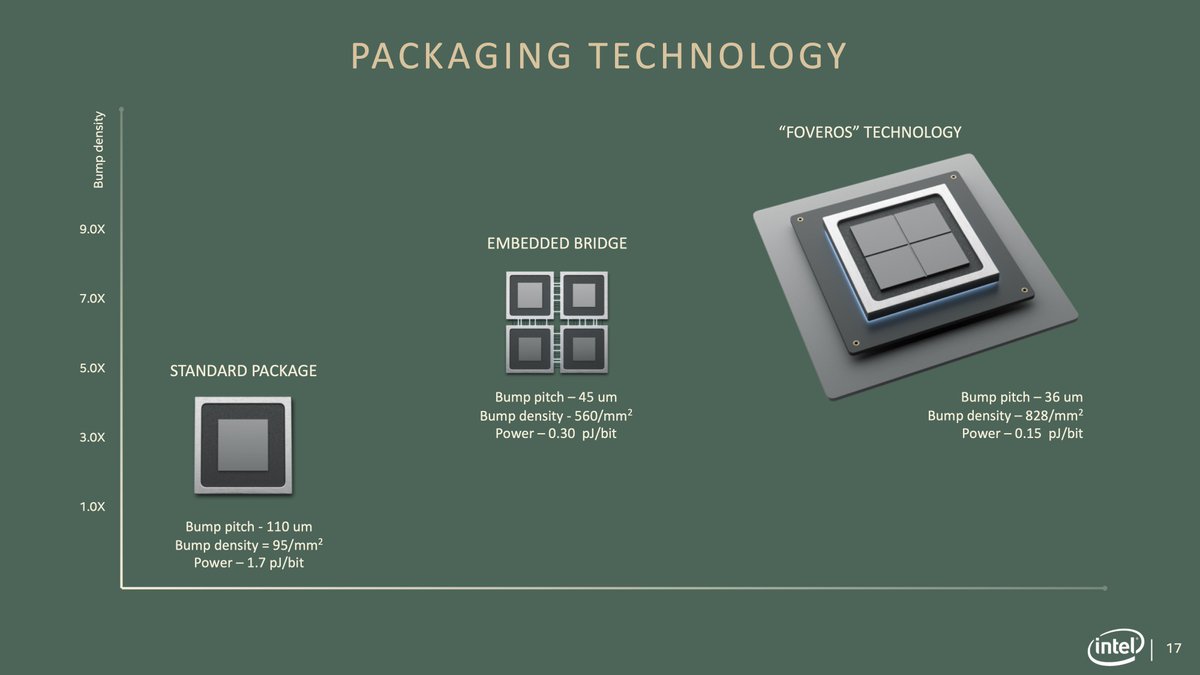

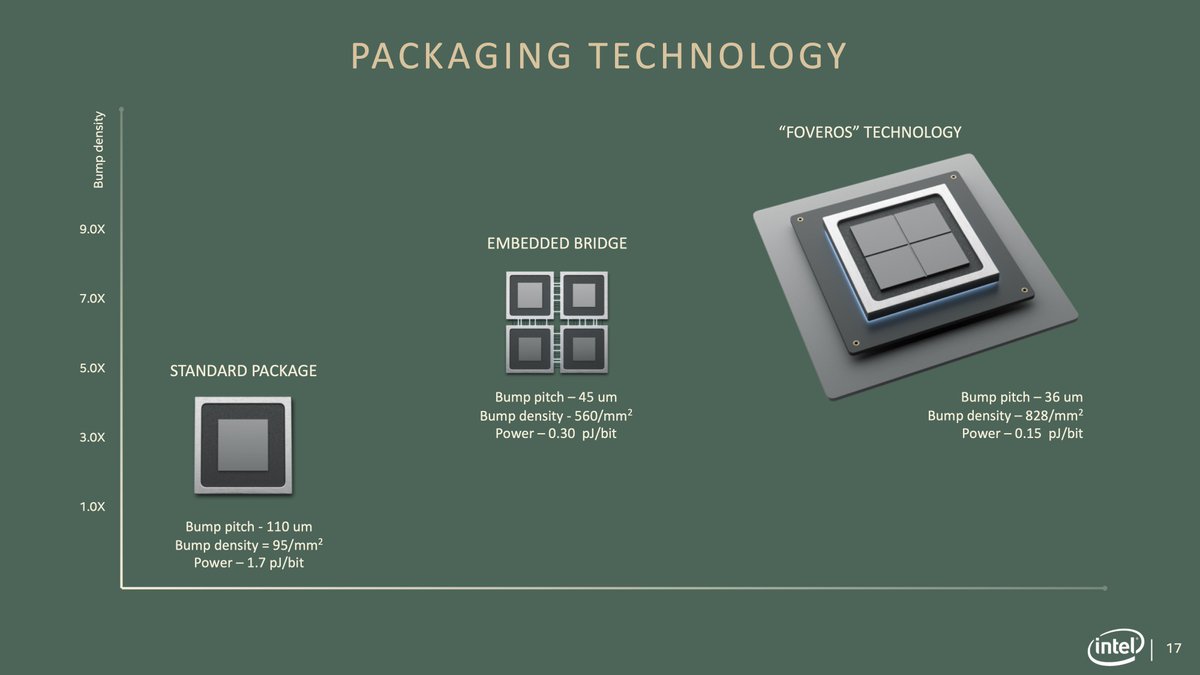

Interesting numbers by @Intel for bumb pitch, bumb density and power with #FOVEROS and #EMIB. For EMIB I had higher values for bumb pitch and power in my head. But it could be that these were simply numbers of the first implementations and Intel could improve here.

“Lakefield spotlights a source of power for Intel:packaging.” A chip that’s getting closer to the size of those in smartphones. #Foveros #IamIntel cnet.com/news/intel-fig…

When people talk about leading edge semiconductors it’s often about clock speeds, cache sizes, etc. But the packaging of those chips to make them useful is incredibly important. @Intel’s #Foveros advanced new packaging is an industry breakthrough in chip stacking. #IAmIntel

We’ve taken the traditional CPU design and radically re-architected it. Intel Foveros, an advanced new packaging technology, allows us to stack chiplets in three dimensions – an industry first – and enables performance and efficiency in a package smaller than a dime.

🔧 Intel EMIB y Foveros ganan interés en la industria ⚙️ Apple y Qualcomm buscan ingenieros con estas tecnologías 🚀 Alternativa al saturado CoWoS de TSMC 📌 Oportunidad para Intel Foundry Services #Intel #EMIB #Foveros #TSMC #FanáticosDelHardware fanaticosdelhardware.com/intel-atrae-in…

②新しい冷却素材と構造 注目「熱を逃がす構造」 ✅ ダイヤモンド薄膜:熱伝導率は銅の5倍 ✅ 液冷プレート:冷媒を直接チップ裏に流す ✅ マイクロチャネル:3D-ICの層間を冷却 これらは単なる冷却装置ではなく “回路設計の一部”として最適化される時代へ #CoWoS #Foveros #ダイヤモンド #液冷 ↓

Nvidia invests $5 billion in Intel's advanced chip packaging tech, like Foveros, to boost AI chip performance and diversify its supply chain. #Nvidia #Intel #Foveros turtnws.biz.id/2025/09/how-in…

turtnws.biz.id

How Intel's Packaging Technology Became the Cornerstone of Nvidia's $5 Billion Bet

How Intel's Packaging Technology Became the Cornerstone of Nvidia's $5 Billion Bet

Major tech companies seeking alternatives are turning to Intel’s IFS. Since Intel’s #Foveros is said to be comparable to TSMC’s CoWoS-S, it has made Intel’s #advancedpackaging a viable option to ensure supply. $MSFT Confirmed Potential customers $NVDA $CSCO #semiconductor

The silicon marvel of packaging: Intel #Lakefield. In some ways, the processor was ahead of its time, but the technology was also simply wrongly positioned as a product. I talked with some of the #Foveros Engineers last year, they were full of pride for what they have achieved.

14:15 #Catterick #BaronDeMidleton or #Foveros Who's your pick? All prices available here: starspreads.com/events/daily-i…

IFS execs expect to provide Intel’s proprietary EMIB and #Foveros, an advanced 3D face-to-face die-stacking packaging tech, to a “new wave” of customer. eetimes.com/ifs-head-sees-…

Intel Clearwater Forest Xeon CPUs With Up To 288 E-Cores To Utilize Foveros Direct 3D Stacking Technology #Wccftech #Intel #Foveros wccftech.com/intel-clearwat…

wccftech.com

Intel Clearwater Forest Xeon CPUs With Up To 288 E-Cores To Utilize Foveros Direct 3D Stacking...

Intel Clearwater Forest Xeon CPUs will be making use of Foveros Direct technology to 3D Stack up to 288 cores on top of the base tile.

FOVEROS is in the process of being trademarked by Intel Corporation uspto.report/TM/97001411 #FOVEROS $INTC

.@Intel Meteor Lake is based on 7nm and will be taped in Q2 2021 using #Foveros packaging technology! He also showed off Ponte Vecchio! #Intel

Not only is @intel’s #Lakefield system architecture design small, but the #Foveros 3D stacking technology points to a new future for SOC designs as well as new product form factors.

Great interview with @RamuneTunes of @intel, discussing packaging technologies, the future research of tech like #Foveros, Intel's chiplet strategy, enabling a chiplet ecosystem, and the direct importance of DTCO in an optimised product portfolio. Transcription soon. #IEDM2019

In einem Video erläutert @Intel_DE den Aufbau von #Foveros und des #Lakefield-SoC: hardwareluxx.de/index.php/news…

「 #FOVERÓS 1st Open Member 」 Classic squad for elegant boys and girls. 🗓️ : Friday, 17 April 2O2O 🏘 : @FOVEROSQ Timeline's 🕗 : NOW Let's come and join us ! ! !

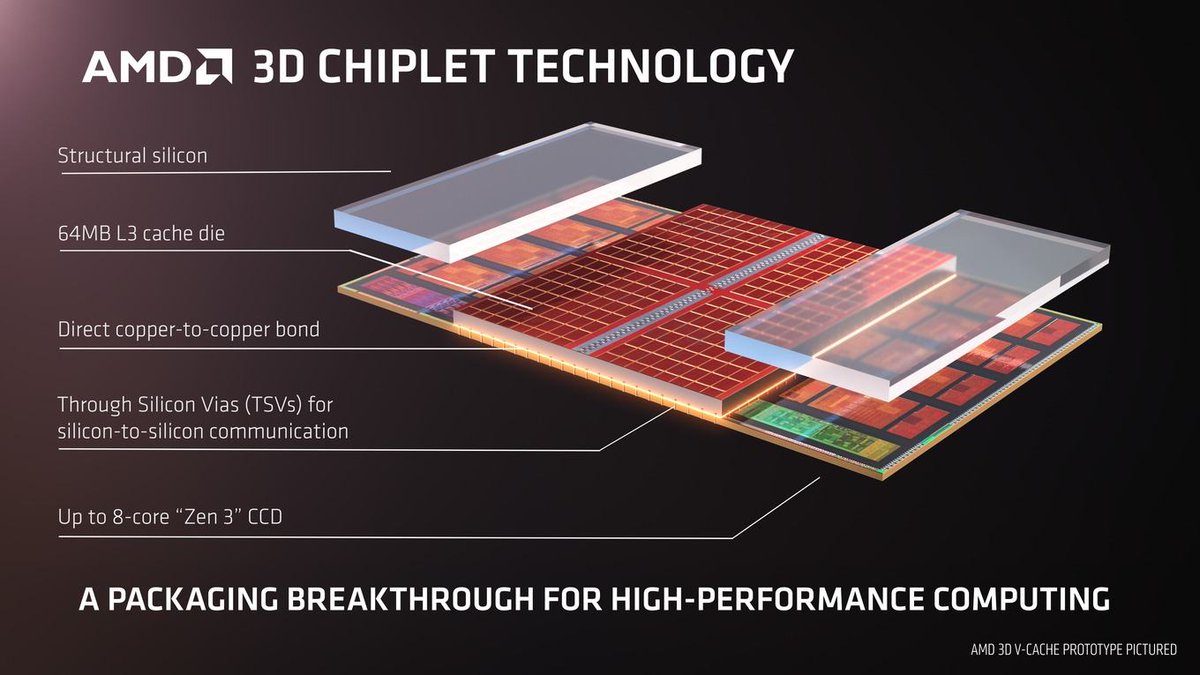

With #Foveros Direct Intel talks about stacking cache on top of a compute tile. Did they say AMD 3D V-Cache?

A test package of #MeteorLake with #Foveros wafer level assembly. It’s a test package, because it would probably not be economically feasible that way.

Intel Teases With Lakefield Picture Featuring Foveros 3D Tech #Intel #Foveros #Lakefield cdrinfo.com/d7/content/int…

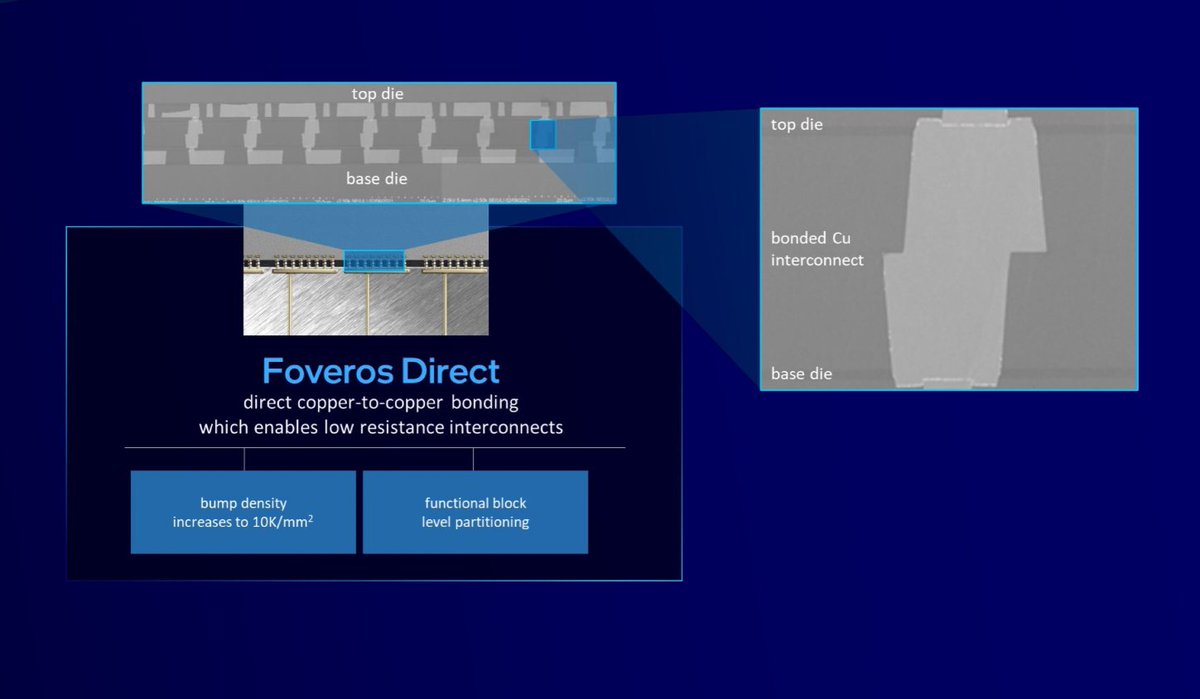

Intel already talked about #Foveros Direct HBI at the Accelerated event. The challenge here is the correct alignment of the dies, which are then connected to each other via the bonded Cu interconnect. It requires several test stages to be executed correctly.

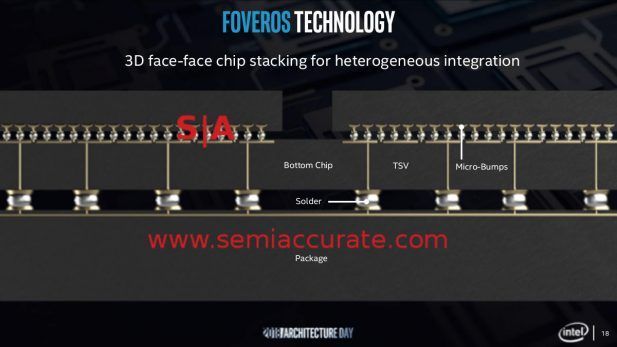

#Intel's #Foveros is pretty much what I described as a multi-core CPU back in the mid/late 90s as a teenager semiaccurate.com/2019/02/11/wha…

Here's the money slide on the architecture of @intel's long-awaited Lakefield chip, which combines their #Foveros chip stacking technology and a big-little hybrid CPU architecture. This type of design is clearly the future for heterogeneous computing.

HUNGRY?! Us too! Come to our Greek Give Back BBQ filled with fun, food, and all of your favorite fraternities and sororities. Perry Quad at 6! #Buffstate #greeklife #foverós

Interesting numbers by @Intel for bumb pitch, bumb density and power with #FOVEROS and #EMIB. For EMIB I had higher values for bumb pitch and power in my head. But it could be that these were simply numbers of the first implementations and Intel could improve here.

Intel ha annunciato i primi due processori ibridi 💡💡 🔗 ow.ly/v16E50A55eV #intel #lakefield #foveros #foveros3d #surfaceneo #thinkpadx1fold #galaxybooks #microsoft #lenovo #samsung #corei5l16g7 #corei3l13g4 #tech #geek #dev

#Intel introduced #3D packing technology, #Foveros, which allows for stacking of more #transistors and other components into #chips, helping industry to continue #MooresLaw. Consumer products using Foveros are expected to launch in #2019 bit.ly/2CkNFzI

Something went wrong.

Something went wrong.

United States Trends

- 1. Rand Paul N/A

- 2. Mullin N/A

- 3. Araujo N/A

- 4. Newcastle N/A

- 5. Cesar Chavez N/A

- 6. Dolores Huerta N/A

- 7. Lamine N/A

- 8. Bernal N/A

- 9. Elanga N/A

- 10. Barcelona N/A

- 11. WNBA N/A

- 12. FOMC N/A

- 13. Lewis Hall N/A

- 14. Incredibles 3 N/A

- 15. The Fed N/A

- 16. Powell N/A

- 17. Gustavo González López N/A

- 18. #FundDHSFreezeICE N/A

- 19. Jones Act N/A

- 20. Afroman N/A