#fpga search results

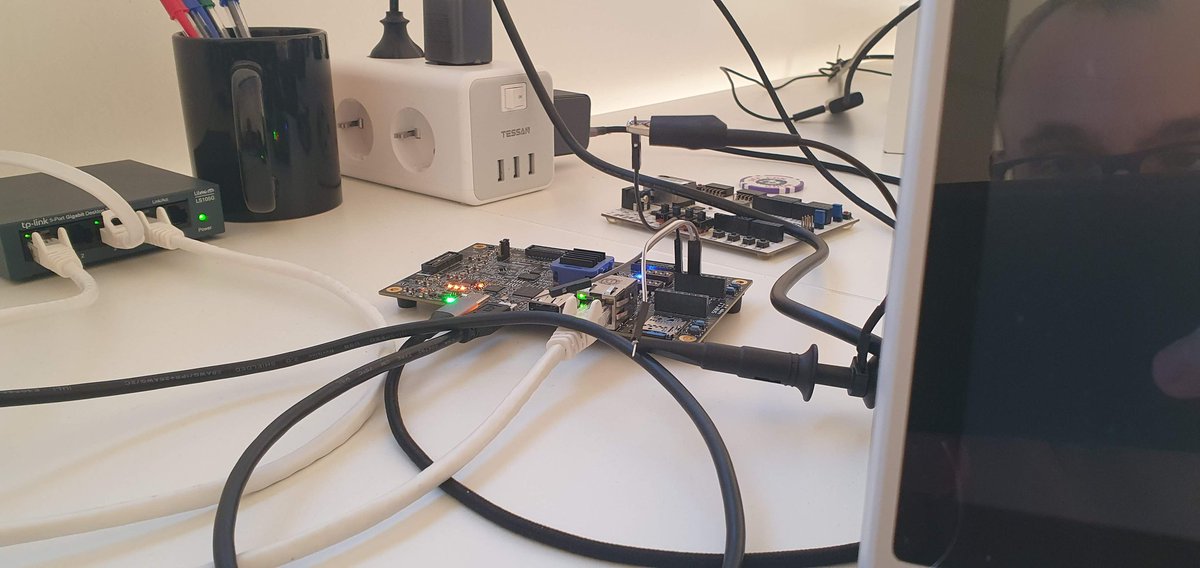

Usually we don't realize that having a #microprocessor running #Linux, with a direct interface to an #FPGA is probably the most important achievement in decades for #embedded systems. From my point of view.

New Video! - The Analogue 3D Review - Was this FPGA N64 console worth the wait? Watch Here : youtu.be/4rUF8vkL6_U #Analogue3D #N64 #FPGA

Accelerate next-generation medical imaging innovation with our PolarFire® FPGAs—combining certified functional safety, hardware-level security and real-time, low-power AI processing. Read the blog: mchp.us/3JhFmeu. #MedicalImaging #FPGA #FunctionalSafety

#FPGA Showdown Here's mine! Also just a part of them, maybe one third. Digilent boards are the prettiest in my collection.

yes! ADC - #apicula -syle 🤣 The blue LEDs are service signals (readiness, counters, etc.), while the top two bars represent ADC measurement data, with the least significant bits at the top. #fpga#gowin#sipeed

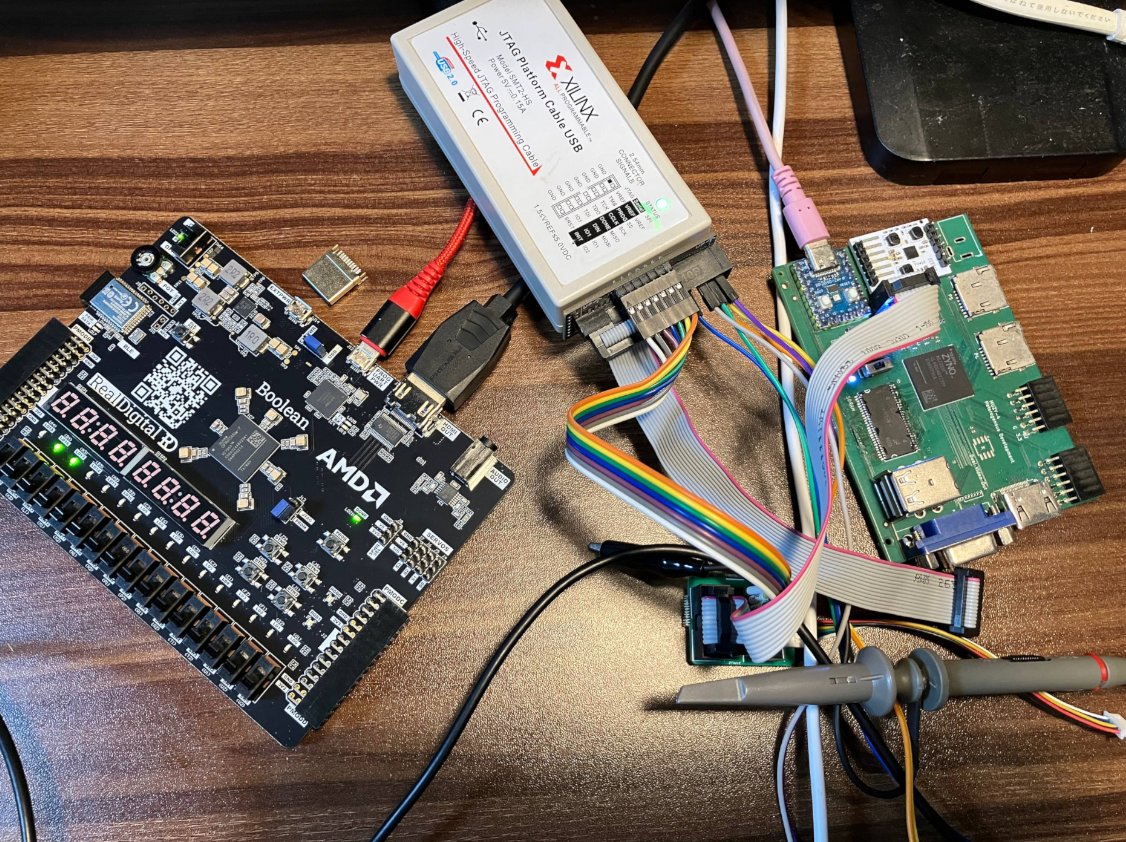

Do you remember your first serious PCB design? Mine is this #Zynq 7010 4-layer board without DDR. The moment of #FPGA JTAG detection will be forever remembered, together with the rusty table, still air, and glorious, responsibility-free days.

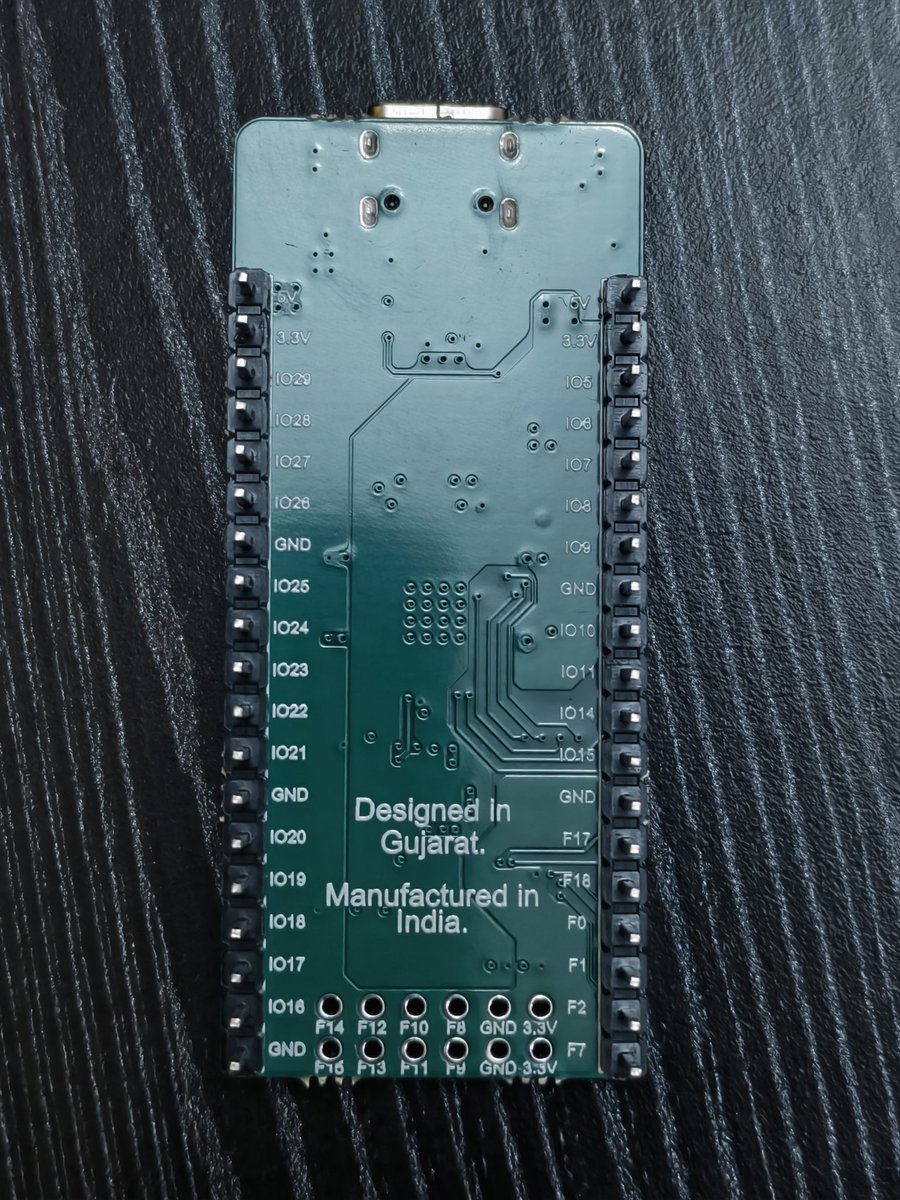

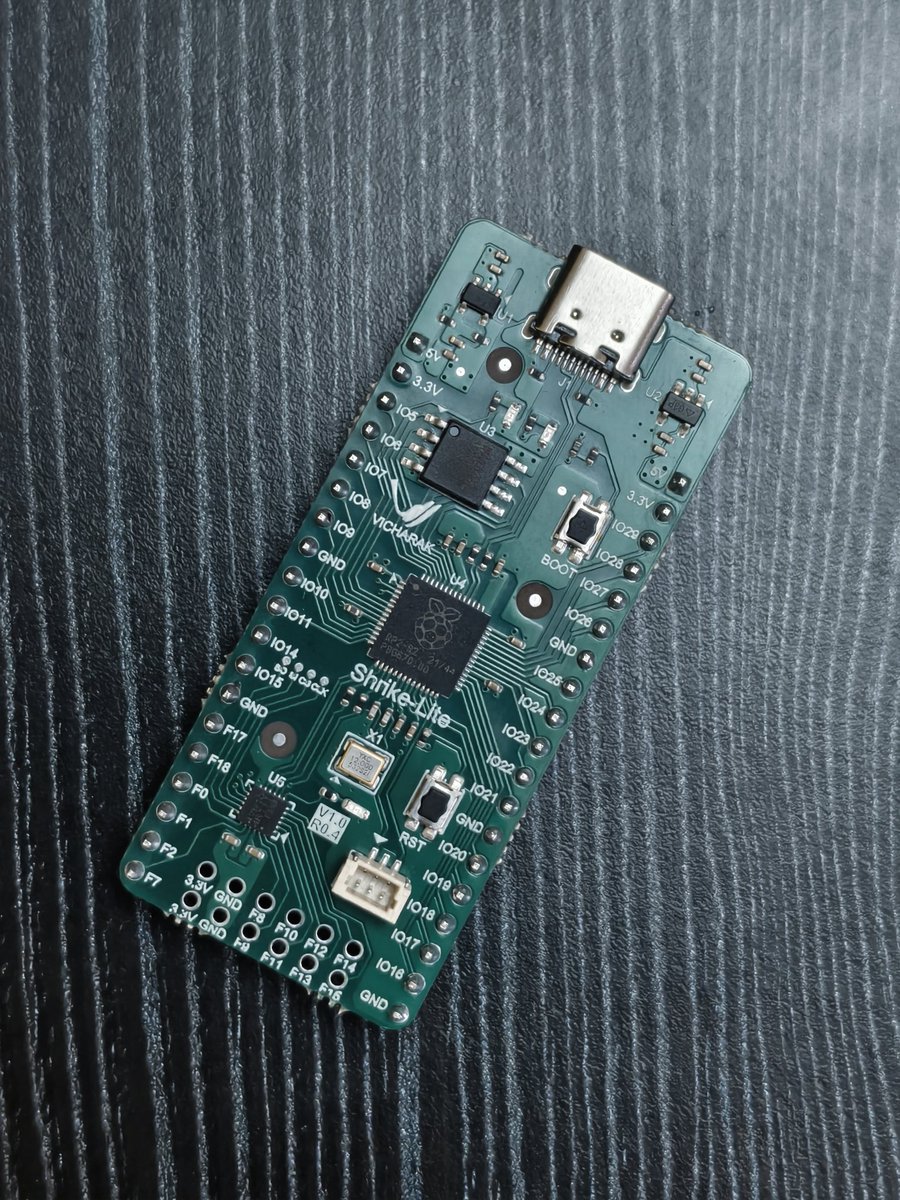

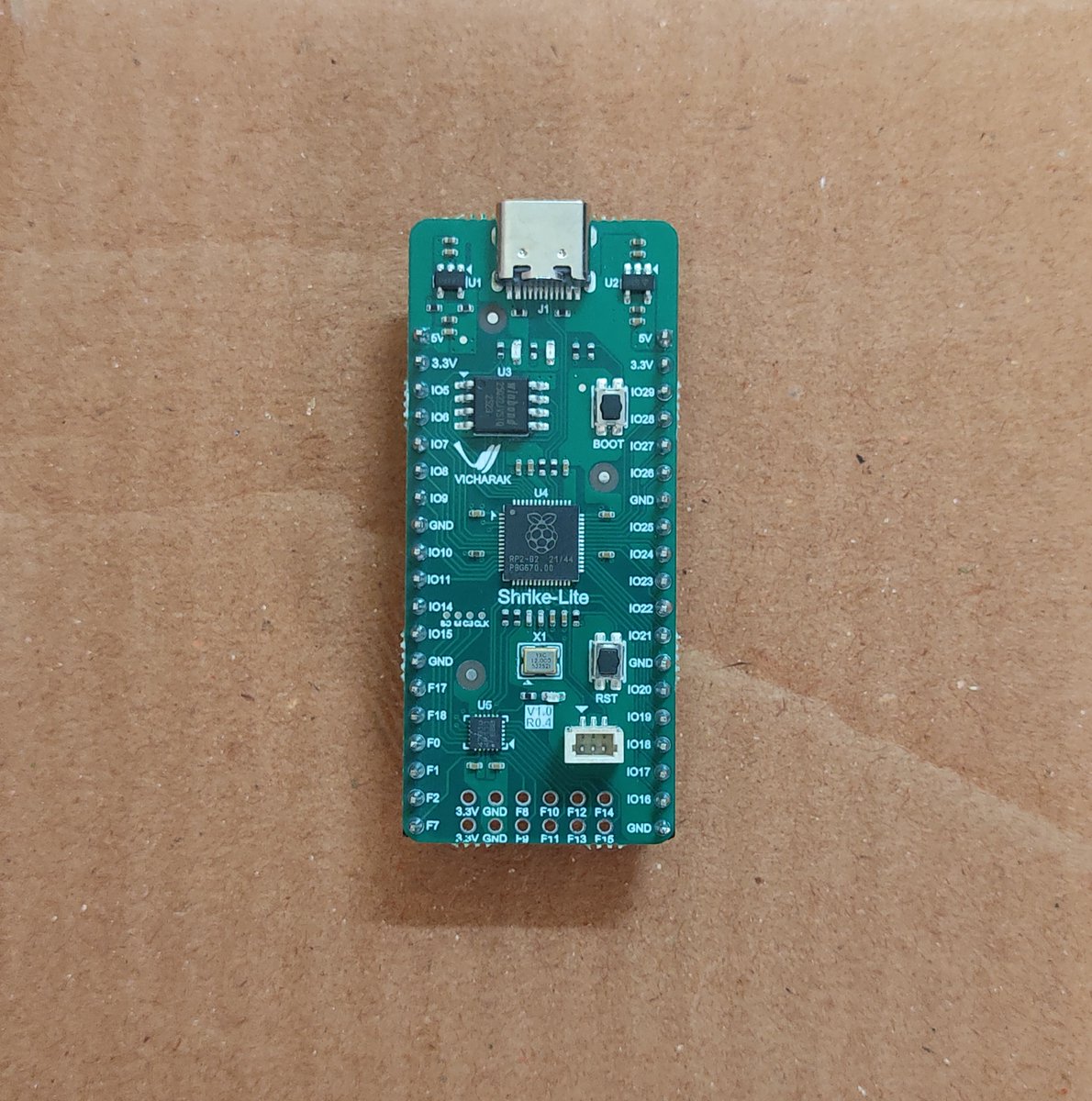

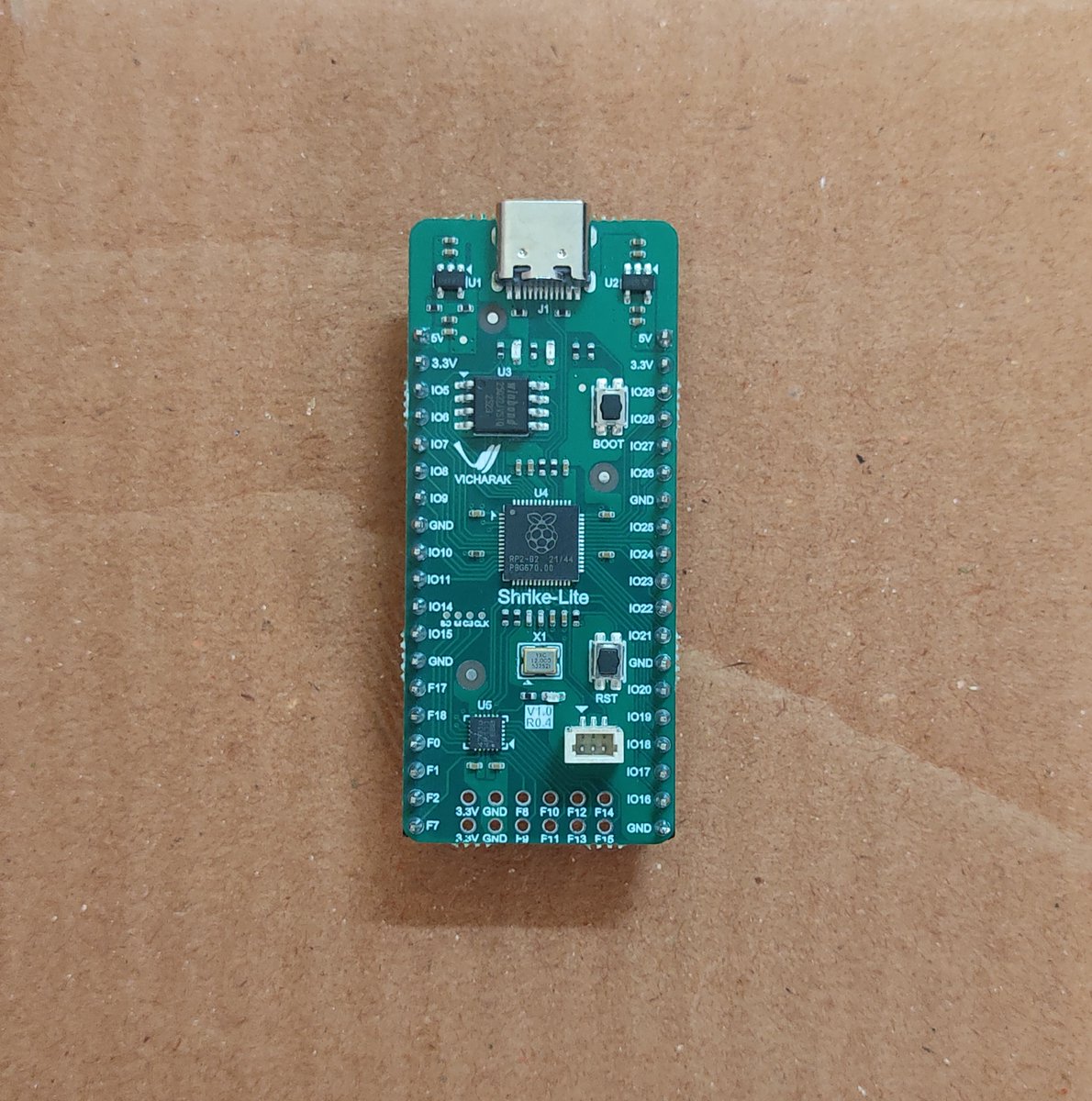

Just got @Vicharak_In 's Shrike-lite. Designed in "ગરવી" Gujarat and Manufactured in India! Will tinker with it in coming months! It's my first FPGA board and will definitely need some steep learning! #FPGA #india #engineering #embedded #mcu

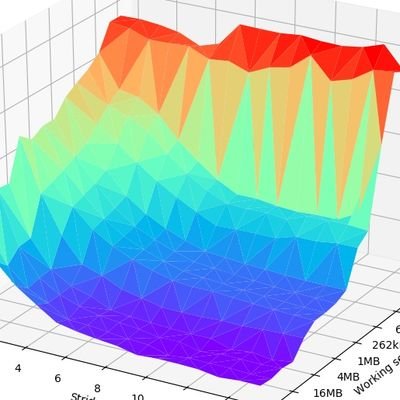

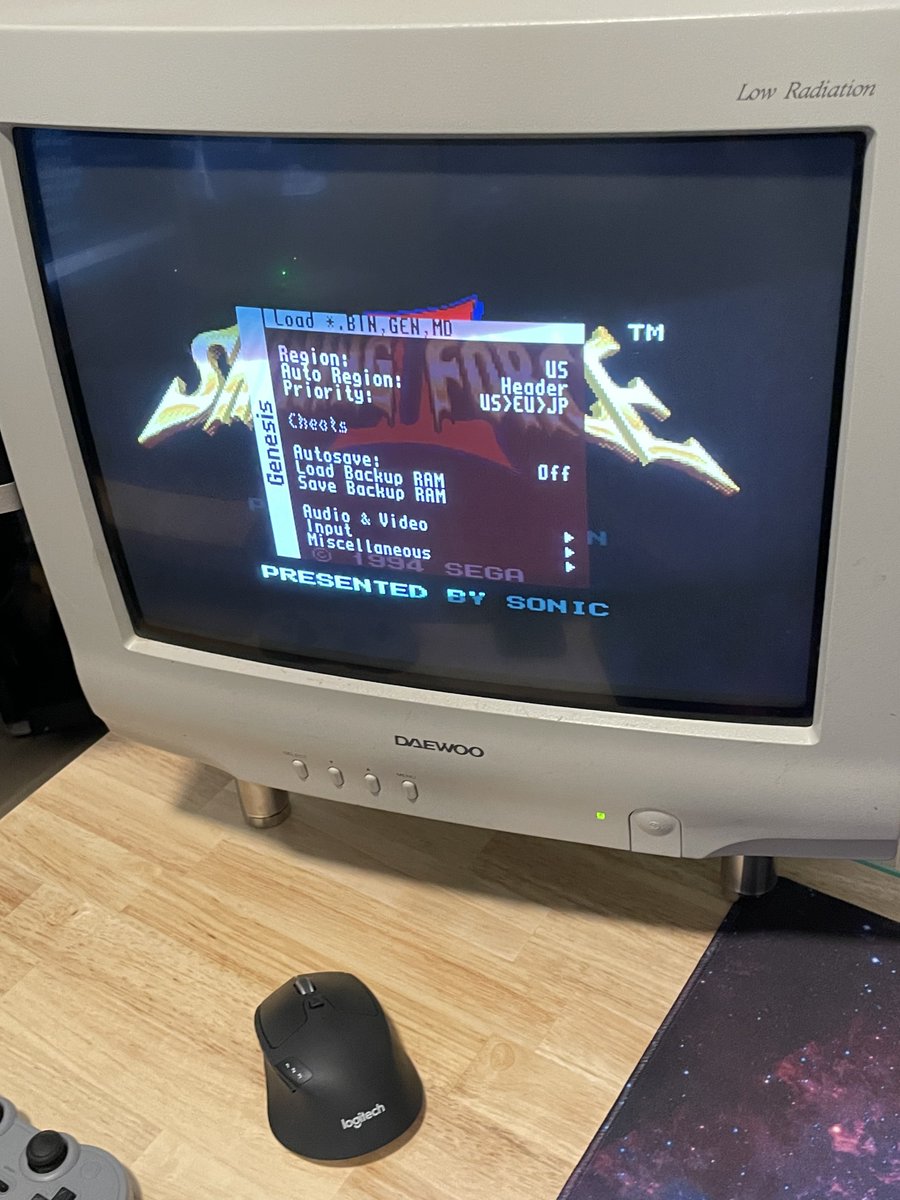

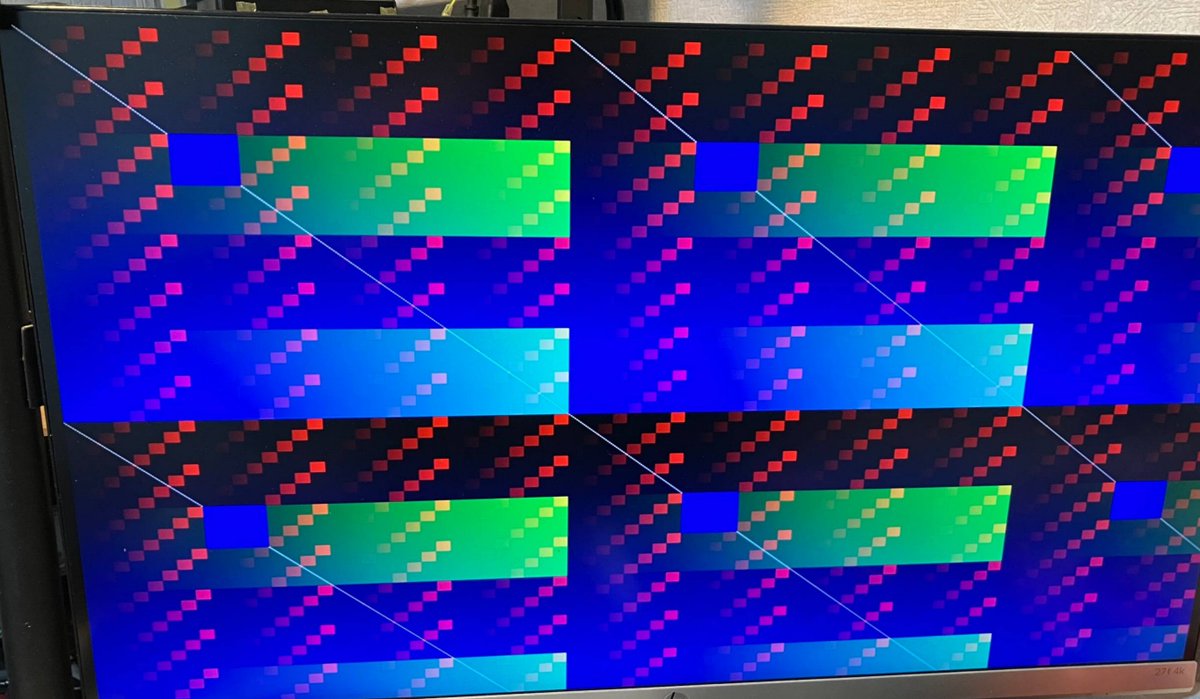

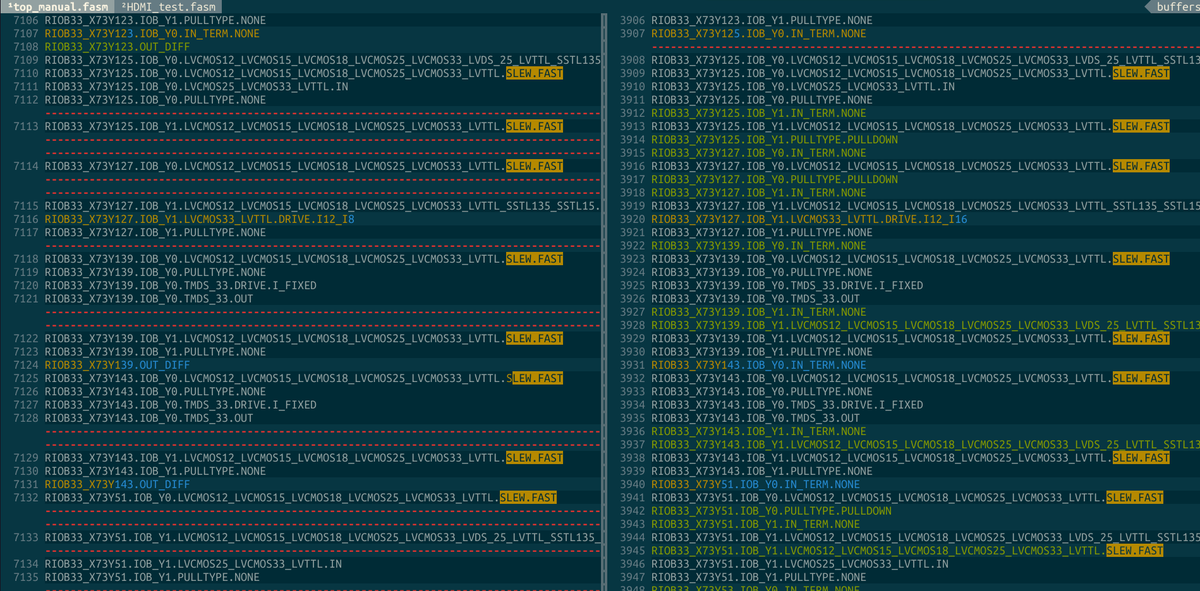

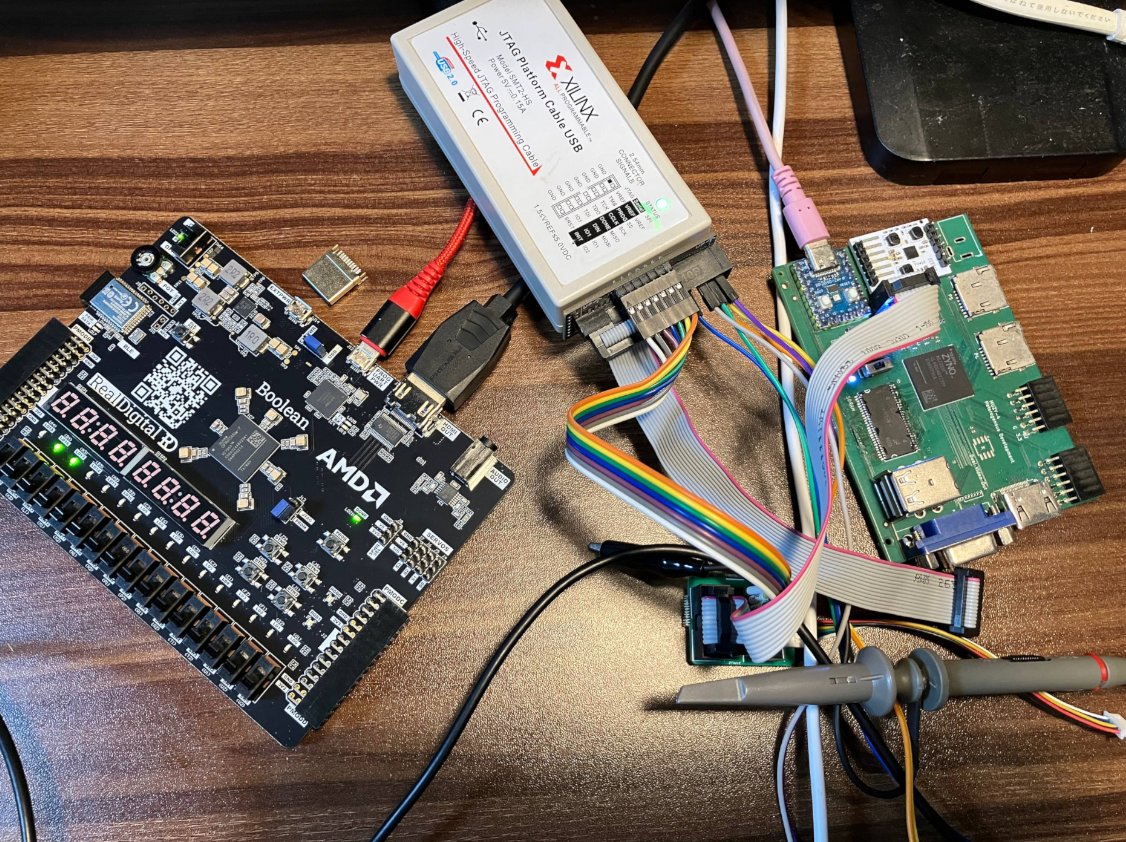

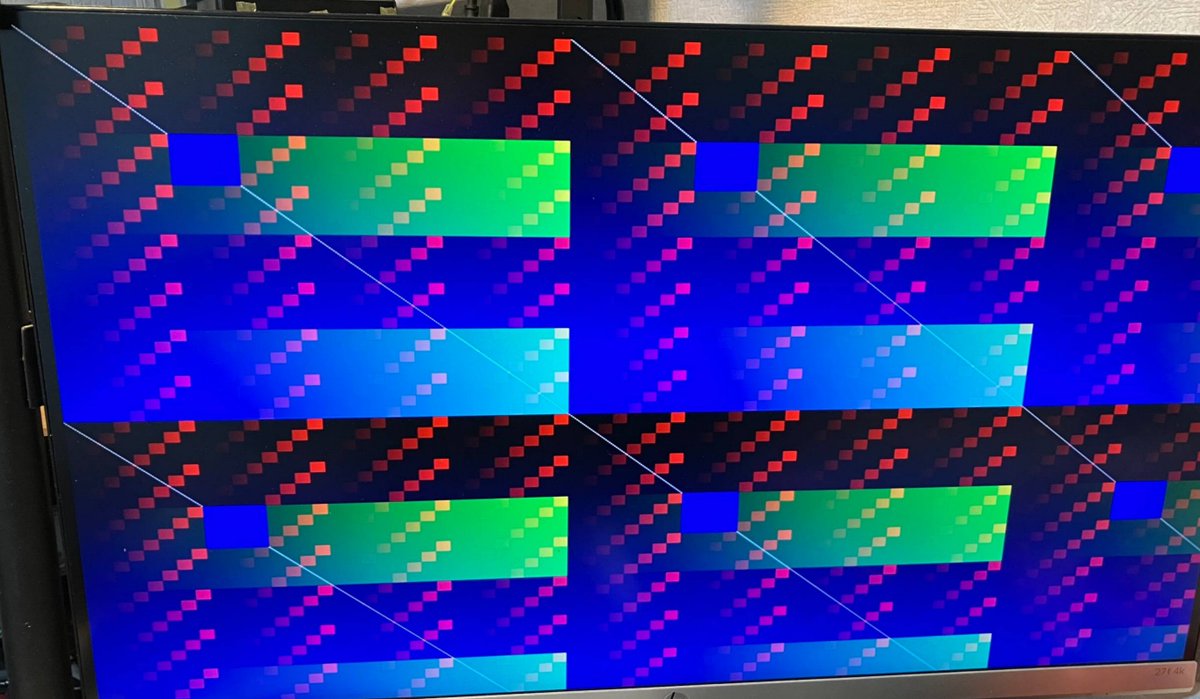

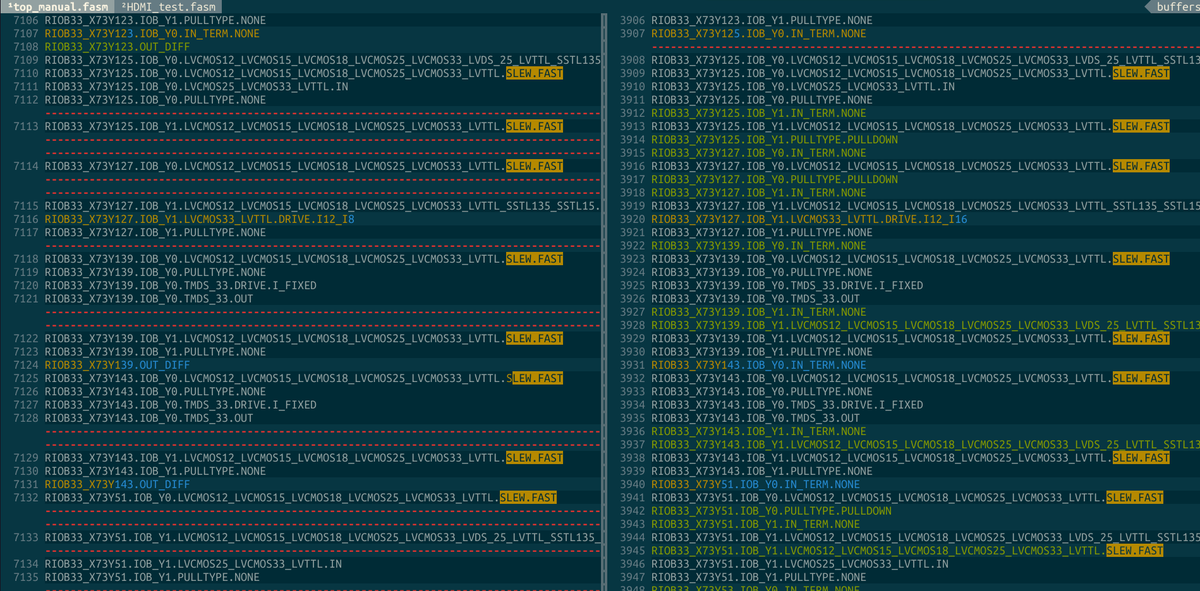

#FPGA developer with open-source toolchains! -> The table -> The screen -> The code (fasm, assembly for FPGA) The lesson is good HDMI output requires SKEW to be FAST, and some more insidious settings that are automatically set by Vivado.

As #FPGA developer, last week I worked almost every day with the #Linux Device Tree. This must be what they call Full Stack developer...

First of all, a huge thanks to @Vicharak_In and @AksharVastarpar for bringing this beauty into our hands! Just received my Shrike-Lite and I’m super excited to push the limits of my imagination with it! In the coming days, I’ll be posting my experiments... #ShrikeLite #FPGA

Seeking ideas for a new #Tang #FPGA board! What would you use a $49 FPGA board with 35K LUTs and 512Mbit DDR4 and MIPI DSI/CSI for? Let us know your project ideas!

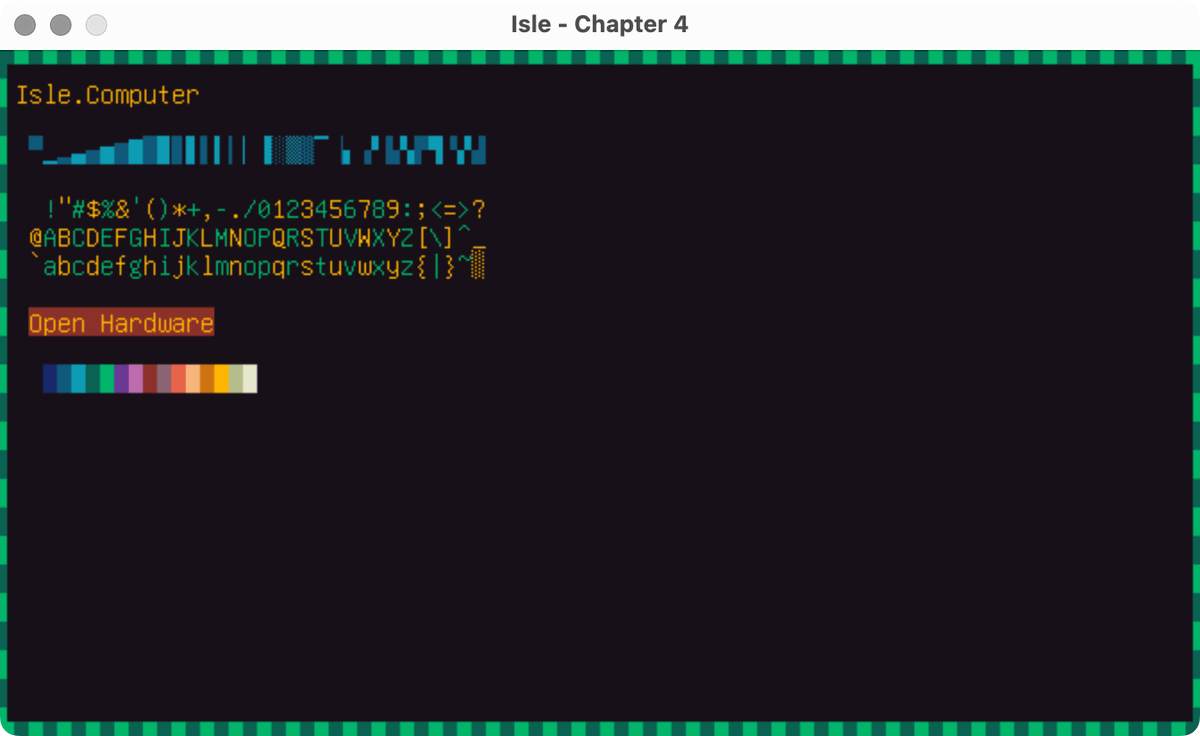

First light! 🔥 ao486 boots DOS on the #TangConsole 138K. HDD, VGA, BIOS, and VGA BIOS are all up and running — watching it hit the DOS prompt on real hardware is surreal. #FPGA #RetroComputing 🎥👇

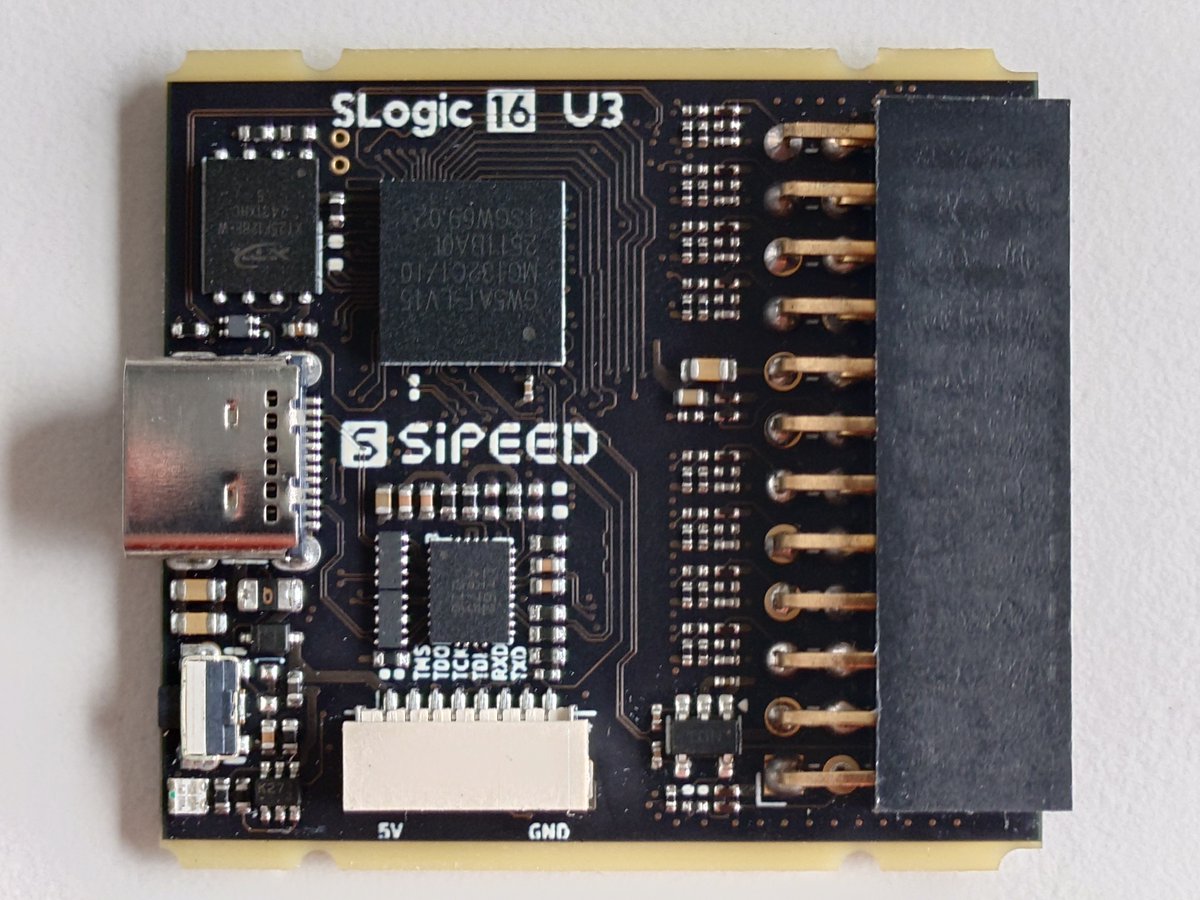

Amazing example of what GOWIN’s GW5AT FPGA can do — single-chip USB3 implementation keeping performance high and cost low 🔥 #FPGA #Engineering

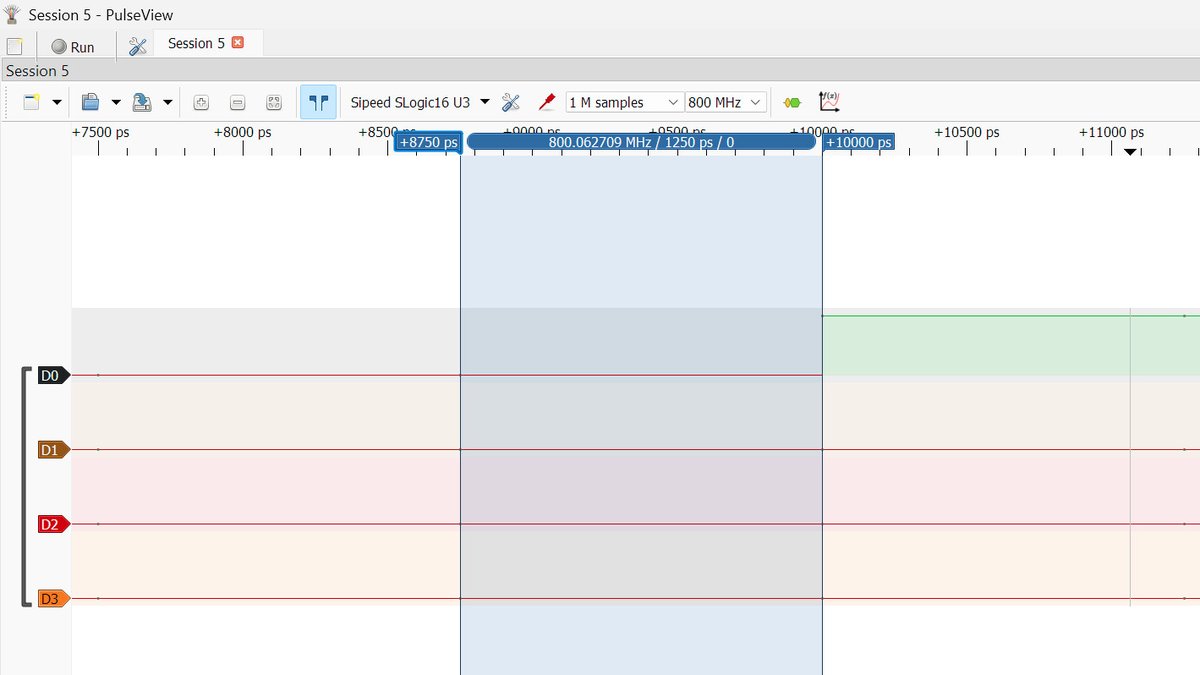

So, @SipeedIO sent me their new SLogic16U3 USB3 logic analyzer to review(free, no obligation). Inside is just a tiny Gowin GW5AT-LV15 FPGA doing softcore USB3(!!!), which is how they made it so cheap. 800MHz@4ch is quite impressive. My verdict? Definitely going in the tool box.

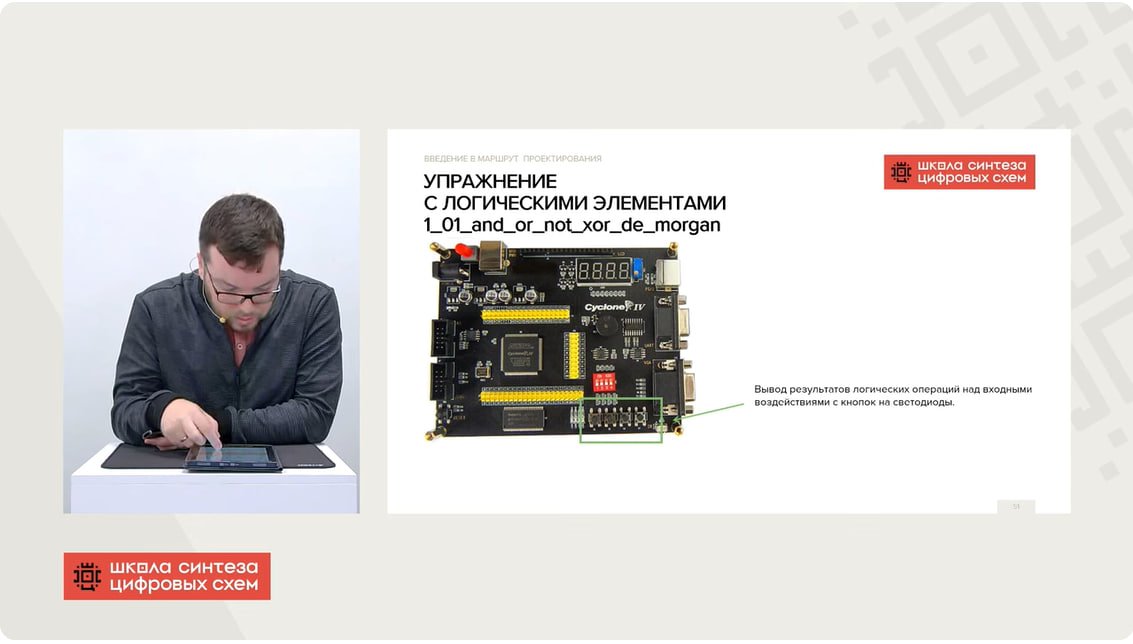

Новое видео на канале Школа синтеза цифровых схем: Занятие 1 (2025-26): Введение в маршрут проектирования и упражнения с комбинационной логикой. youtu.be/WxSy26MfwK8 #xilinx #vivado #fpga #плис

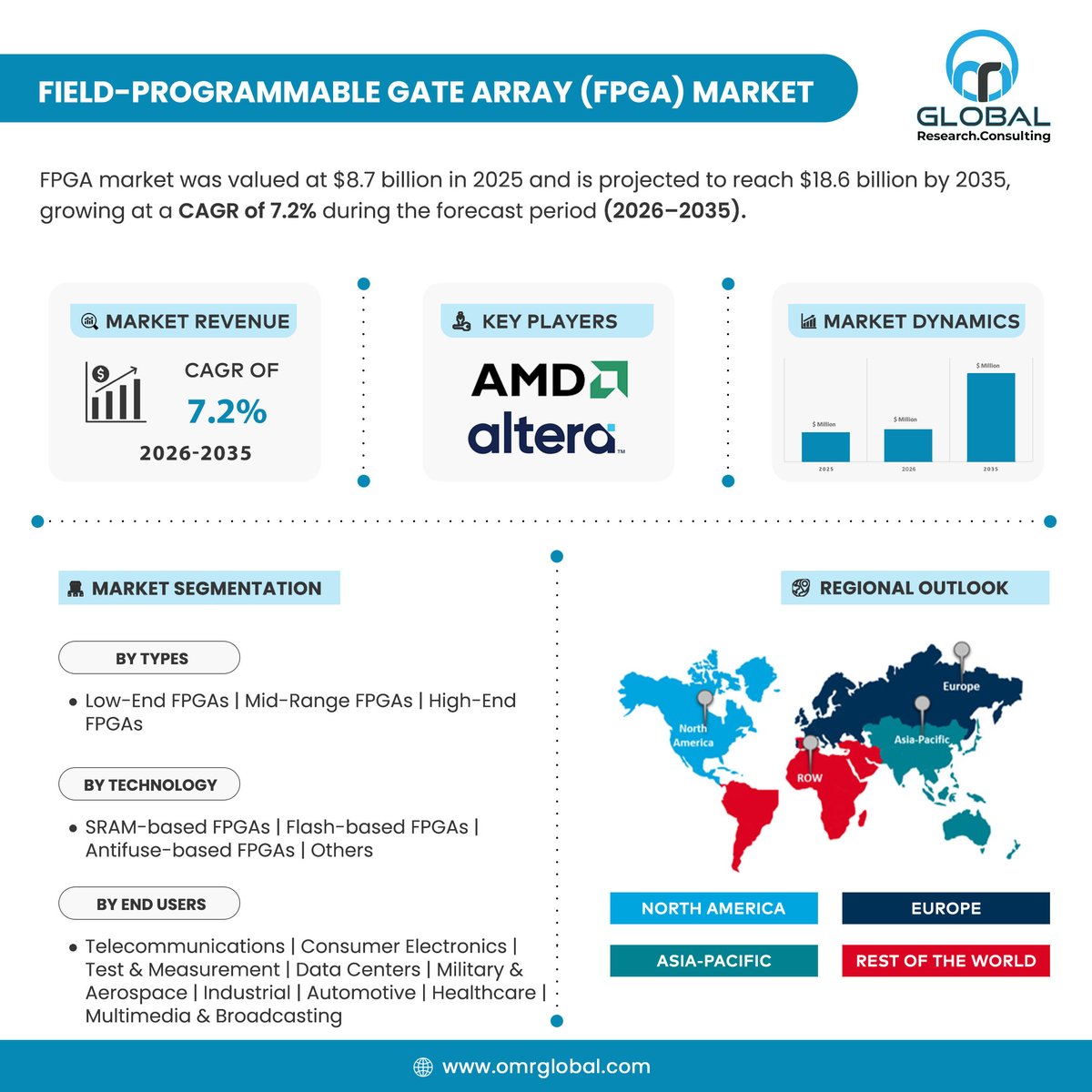

🚀 The FPGA Market is set to soar from $8.7B in 2025 to $18.6B by 2035 at a 7.2% CAGR! Rising demand for AI, edge computing, 5G, automotive & healthcare solutions is driving growth. 🌐 For more visit:shorturl.at/f3BD2 #FPGA #Semiconductors #AIHardware #EdgeComputing #5G

AumRaj is seeking experienced VLSI engineers to join our team and work on industry driven semiconductor design challenges. No salary bar for the right candidates. Apply Now 📧 [email protected] 📞 +91-7043303488 #aumraj #rtl #fpga #vlsi #iot #asic #design #verification

An #FPGA, when incorporated into an #SDR, is incredibly powerful—these systems can provide the needed input/output bandwidth and #processing capabilities for implementing #multi-gigasample rates and #giaghertz-range bandwidths. bit.ly/3vvyjYu

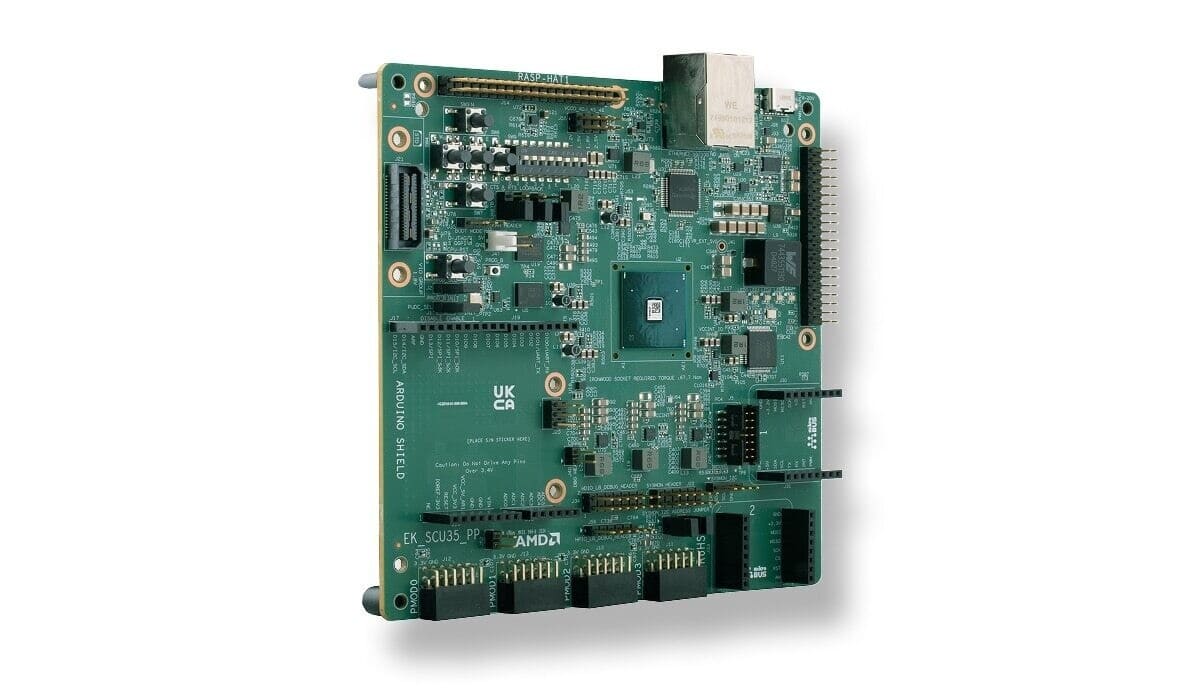

Infineon Technologies has confirmed that AMD successfully tested its 64 Mb HYPERRAM memory and HYPERRAM controller IP with the AMD Spartan UltraScale+ FPGA SCU35 Evaluation Kit. newelectronics.co.uk/content/news/a… #FPGA #MemoryTech #Infineon

マイコン FPGA CPLD 一覧 store.shopping.yahoo.co.jp/eletech/a5dea5… #マイコン #FPGA #CPLD #電子部品通販

When to Sell vs. Hold: Decision Framework for Excess Inventory Management icdrex.com/when-to-sell-v… #lattice #fpga #avant #semiconductor #chip #drex #drexelectronic

Did you know #AWS has #FPGA instances? You do now riscv.org/blog/7-things-…

riscv.org

7 Things I Learned at RISC-V Summit North America 2025

As the dust settles on RISC-V Summit North America 2025, Tom Gall looks back on his first RISC-V Summit since joining as VP of Technology.

🔧 AMD Spartan UltraScale+ SCU35 Kit ya disponible ⚙️ Incluye FPGA SU35P, bajo consumo y alta E/S 🧠 Compatible con Vivado y Vitis 💰 Desde 229$ (~198€), disponible globalmente #FanáticosDelHardware #AMD #FPGA #Hardware fanaticosdelhardware.com/amd-lanza-el-k…

Five Proven Ways to Recover Value from Surplus Inventory icdrex.com/five-proven-wa… #lattice #fpga #avant #semiconductor #chip #drex #drexelectronic

Someday it will be interesting to look at the minimum requirements for the RISCV version of #NetBSD — maybe it will fit into Tangnano20k #fpga?🤪

AGLN250V2-VQG100I #Microchip IC FPGA 68 I/O 100VQFP Find electronic components? Visit our website to get the best quote • 100% Original & New • No MOQ • 365 Days Warranty Email: [email protected] #FPGA #embedded_ic #hardfindelec

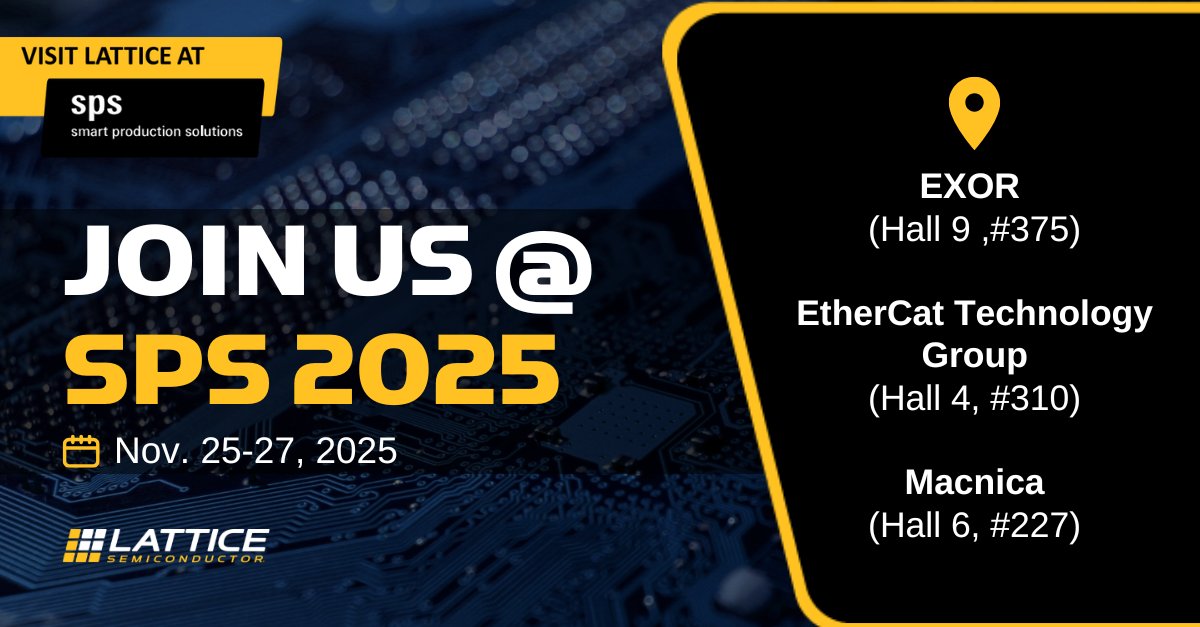

🚨 #SPS25 starts tomorrow! See Lattice’s advanced #FPGA hardware and software solutions for #Industrial and #edgeAI applications at the @EtherCAT_Group, #EXOR, and #Macnica booths.

#FPGA Showdown Here's mine! Also just a part of them, maybe one third. Digilent boards are the prettiest in my collection.

#fpga are great, but it's snowed and I need to clear all the paths and the driveway.🙂 (I'm not going to clear my local fir tree, it looks so beautiful in the snow.)

Accelerate next-generation medical imaging innovation with our PolarFire® FPGAs—combining certified functional safety, hardware-level security and real-time, low-power AI processing. Read the blog: mchp.us/3JhFmeu. #MedicalImaging #FPGA #FunctionalSafety

First of all, a huge thanks to @Vicharak_In and @AksharVastarpar for bringing this beauty into our hands! Just received my Shrike-Lite and I’m super excited to push the limits of my imagination with it! In the coming days, I’ll be posting my experiments... #ShrikeLite #FPGA

Do you remember your first serious PCB design? Mine is this #Zynq 7010 4-layer board without DDR. The moment of #FPGA JTAG detection will be forever remembered, together with the rusty table, still air, and glorious, responsibility-free days.

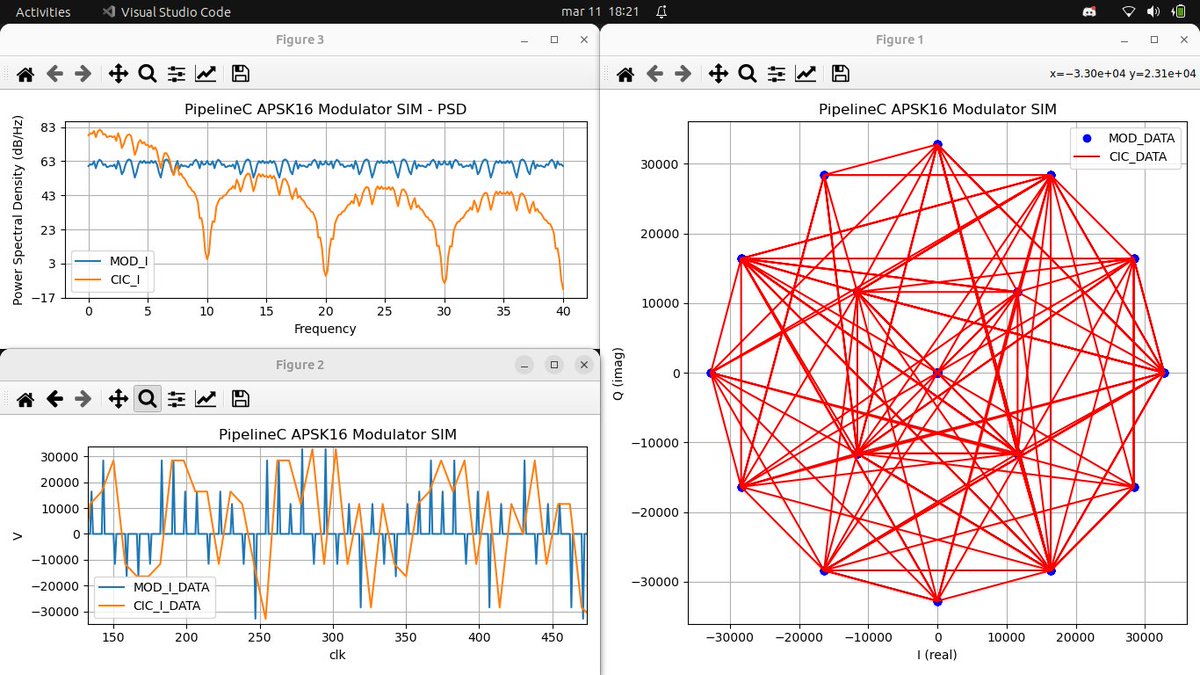

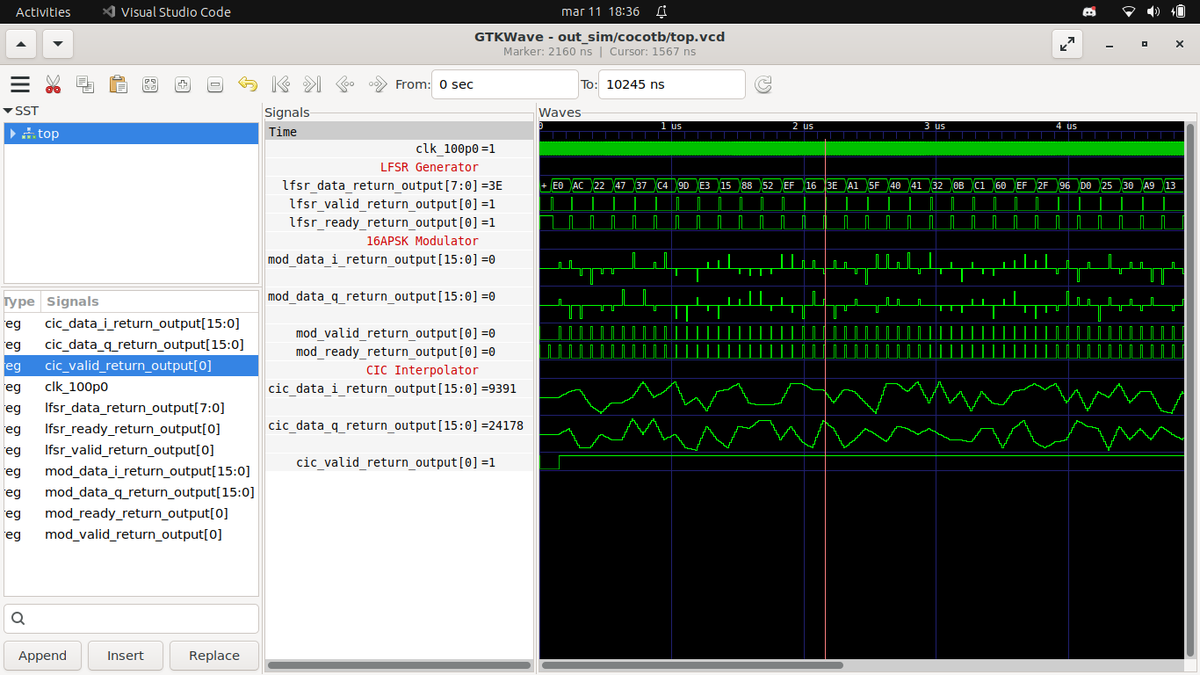

Developing one #16APSK Modulator on #FPGA using #PipelineCHDL ! Testbench Datapath: #LFSR -> APSK16 Map -> #CIC Filter -> out Simulation done with #ghdl + #cocotb, data plotted using #numpy and #matplotlib ! #dsp #sdr #HDL #ccsds #rf #psk #apsk #modem

Day 77: ✅ Focused on timing closure and resource balance in TPG pipelines to keep II = 1 at 250 MHz ✅ Obtained partial simulation results for my new paper 📊 ✅ 45 minutes workout 🏋🏻♀️ #MachineLearning #AI #FPGA #100DaysofCode

🎃 No tricks, just treats! 🍬 Discover how Lattice provides innovative, low power #FPGA solutions for datacenters, automation/robotics, AI, security, and more: bit.ly/3VO8ldI

#FPGA developer with open-source toolchains! -> The table -> The screen -> The code (fasm, assembly for FPGA) The lesson is good HDMI output requires SKEW to be FAST, and some more insidious settings that are automatically set by Vivado.

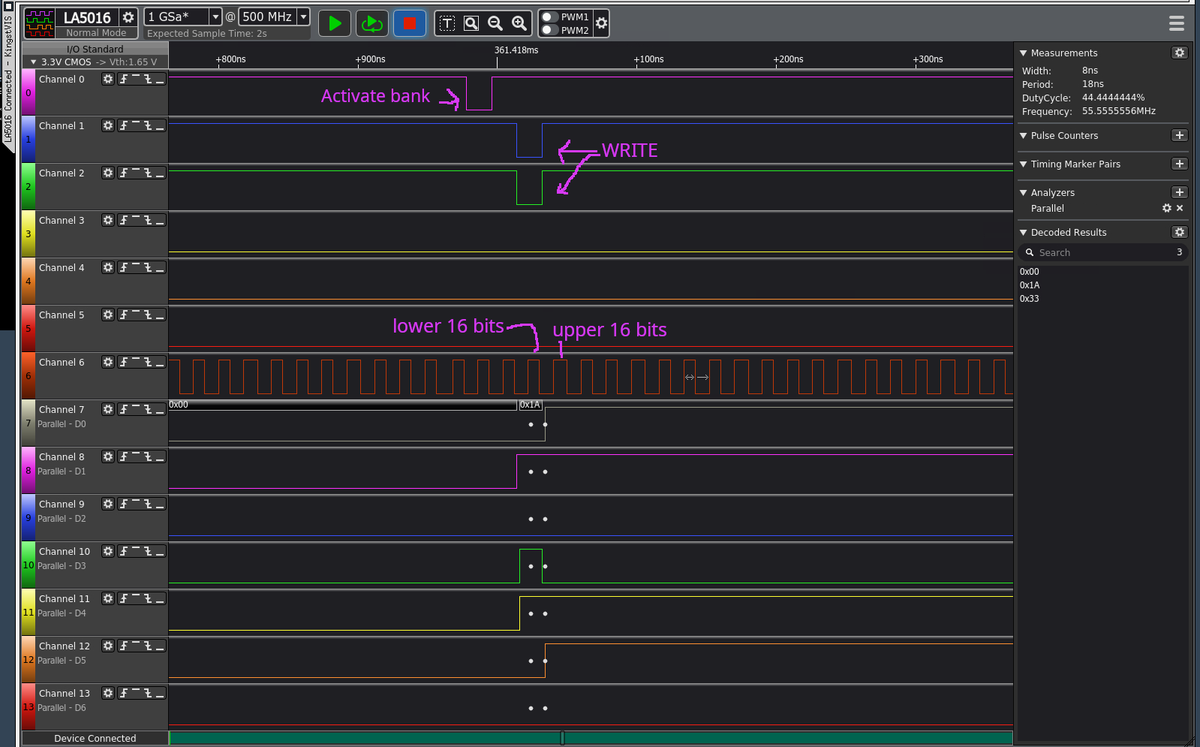

And now I regret not getting a 32-bit logic analyser.🤣 Remember – 8 inputs are laughable if you're seriously interested in #fpga, get something more powerful right away. SDRAM signal graphs, if anything.😜

Seeking ideas for a new #Tang #FPGA board! What would you use a $49 FPGA board with 35K LUTs and 512Mbit DDR4 and MIPI DSI/CSI for? Let us know your project ideas!

After a whole day talking about #FPGA, it's time for a relaxing evening playing with this new tiny FPGA board based on an @efinixinc Trion FPGA.

M64 vs #MiSTer – Could ModRetro’s #FPGA #N64 Become the True Successor? Thanks to @timeextension64 for pointing this out. Read it here: metalgamesolid.com/fpga/other-fpg…

Something went wrong.

Something went wrong.

United States Trends

- 1. #StrangerThings5 140K posts

- 2. Thanksgiving 636K posts

- 3. Reed Sheppard 3,058 posts

- 4. Afghan 254K posts

- 5. Podz 2,966 posts

- 6. robin 69.3K posts

- 7. National Guard 625K posts

- 8. holly 51.2K posts

- 9. BYERS 26K posts

- 10. Gonzaga 8,098 posts

- 11. #AEWDynamite 21K posts

- 12. Dustin 86.4K posts

- 13. Michigan 77.6K posts

- 14. Amen Thompson 1,351 posts

- 15. Tini 8,001 posts

- 16. Erica 13.1K posts

- 17. Rahmanullah Lakanwal 95.8K posts

- 18. #Survivor49 3,028 posts

- 19. Will Richard 2,079 posts

- 20. Jardine 6,314 posts