Semiconductor Engineering

@SemiEngineering

Deep Insights For The Tech Industry #semiconductor #semiEDA #AI #embedded #verification #lowpower #test #DataAnalytics #automotive #chipdesign #ICmanufacturing

你可能会喜欢

Latest: China’s DDR5/LPDDR5X; government fundings climb; GF’s latest deal; Rapidus $; GPU vs. TPU; TSMC’s 2nm fabs; ASIC acquisition; diamond chip foundry; data sharing in IC manufacturing; how Americans use AI; open-source chiplets ... semiengineering.com/chip-industry-… #semiconductor

semiengineering.com

Chip Industry Week In Review

China's DDR5/LPDDR5X; global government fundings climb; GF's latest photonics deal; Rapidus' infusion; GPU versus TPU; TSMC's 2nm fabs; ASIC acquisition; diamond chip foundry; data sharing in IC...

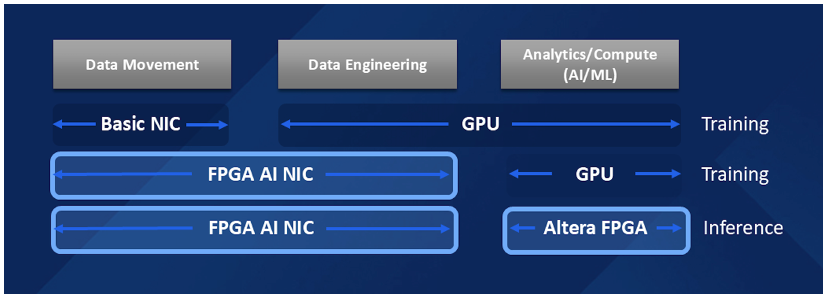

Growing use cases include life science AI, reducing memory and I/O bottlenecks, data prepping, wireless networking, and as insurance for evolving protocols. semiengineering.com/fpgas-find-new… #FPGA

The application of AI into design tools and flows will take several forms, each independent, but all potentially working together. semiengineering.com/ai-plays-multi… #semiEDA #AI #chipdesign #AgenticAI #semiconductor #verification

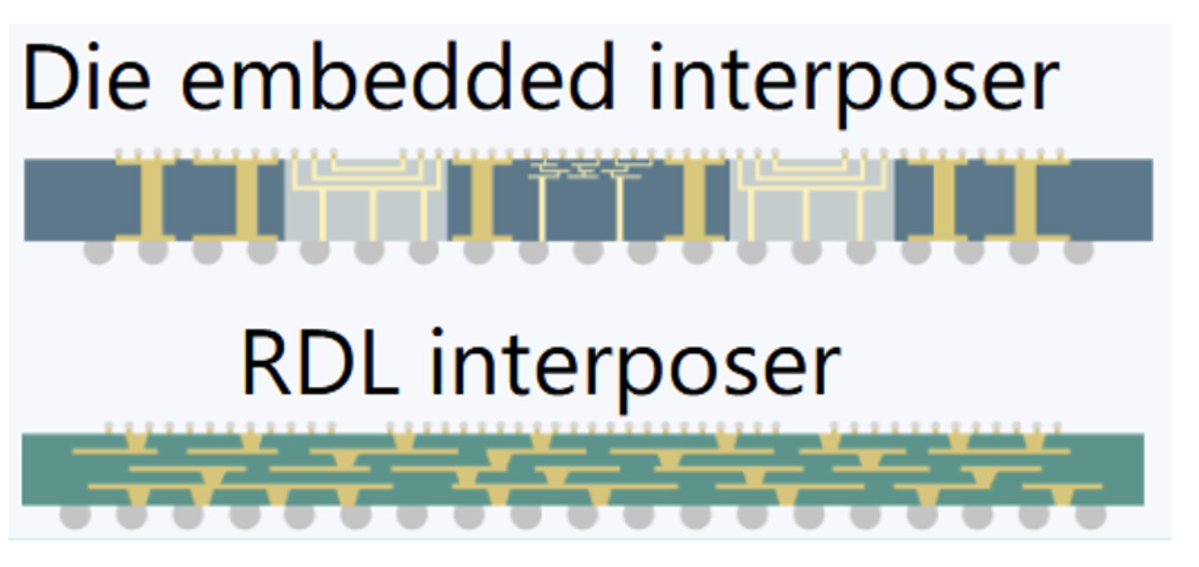

New Panel Production Efforts Target Interposer Costs: semiengineering.com/new-efforts-fo… A pilot line will attempt to dial in a volume process for large organic interposers. #semiconductor #advamcedpackaging #Joint3 @Resonac_Group @brewerscience #UMC @aseglobal @SEMIconex @iNEMIorg

Latest news: Deals, deals, deals; IC tariffs delay; chips for the Middle East; Deloitte’s IC predictions; EU Chips Act; memory prices; issues in ramping adv. packaging; CXL 4.0; new nano fab; AI legislation block ... semiengineering.com/chip-industry-… #semiconductor #EUV #technews #semiEDA

semiengineering.com

Chip Industry Week In Review

Chinese EUV alternative; deals, deals, deals; IC tariffs delay; chips for the Middle East; Deloitte's IC predictions; EU Chips Act; memory prices; issues in ramping advanced packaging; CXL 4.0 spec.;...

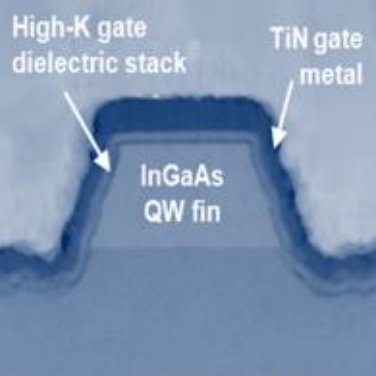

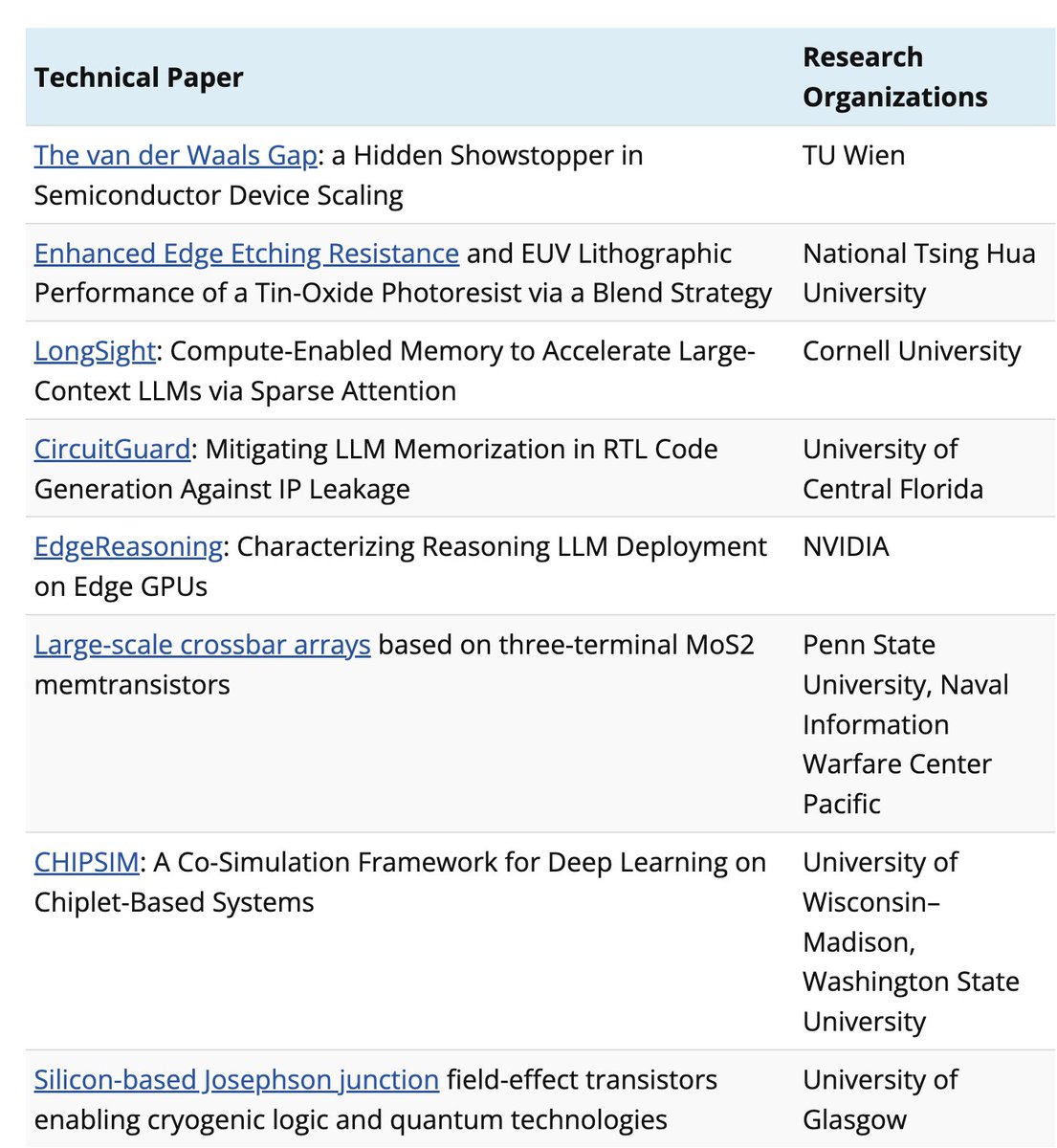

New technical papers recently added to Semiconductor Engineering’s library semiengineering.com/chip-industry-… #semiconductor #interconnects #DRAM #chiplets #accelerators #CFET #NSFET

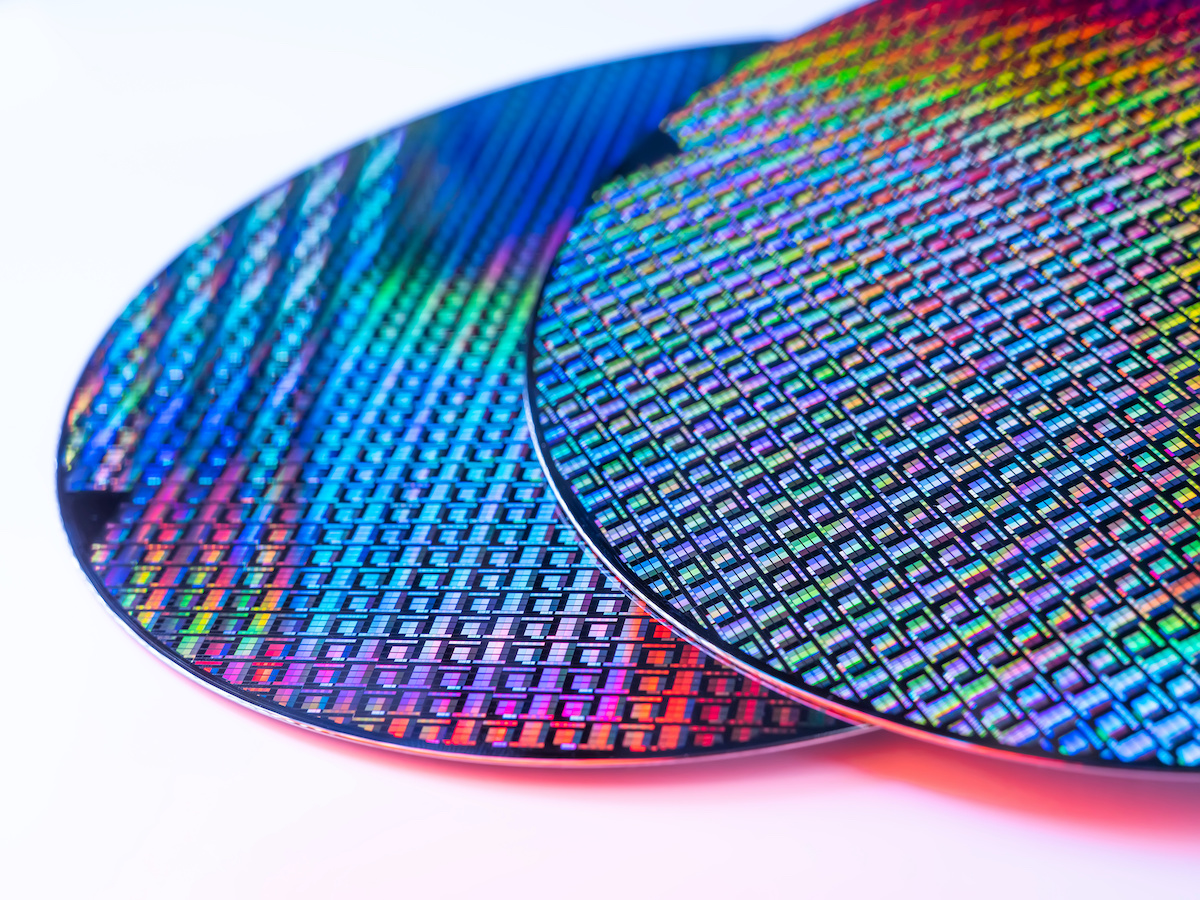

Special Report: Thin films, which are essential for isolating signals & insulating different components and metal layers, are becoming heat traps as physical dimensions continue to shrink in chips used inside AI data centers semiengineering.com/the-thermal-tr… #semiconductor #AI #heat

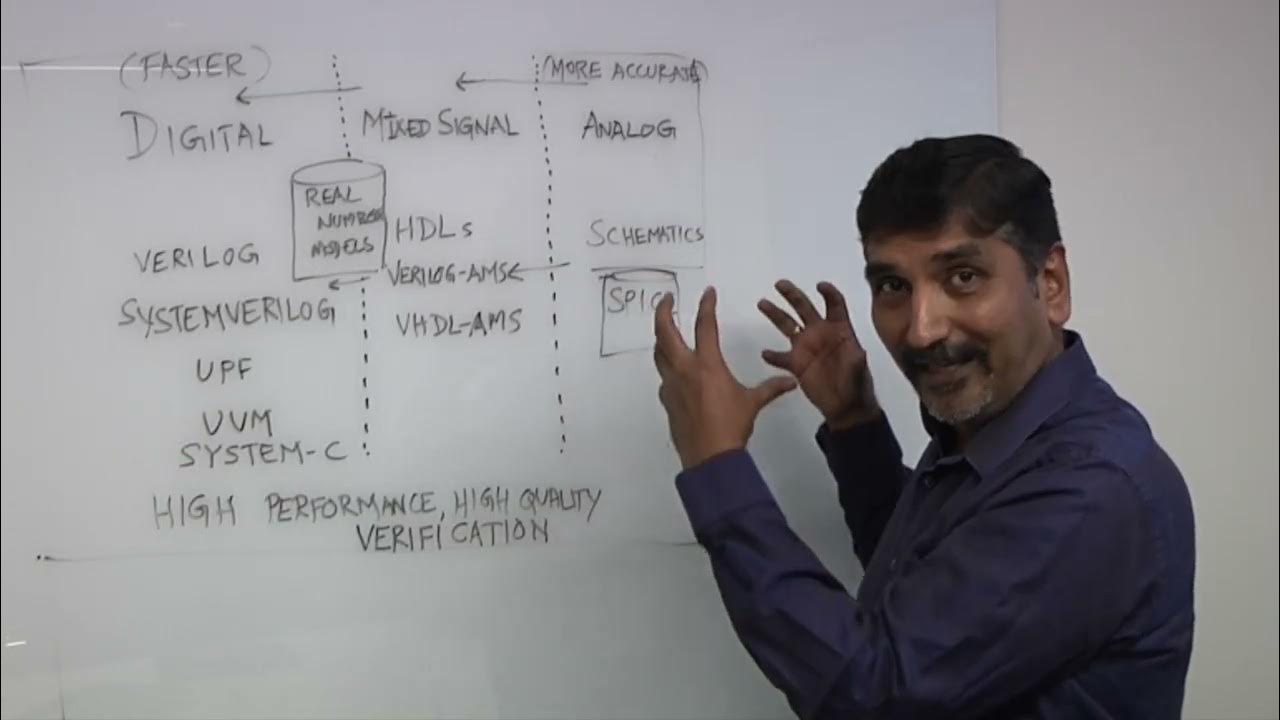

Changes In Mixed-Signal IC Verification: Why digital and analog engineers must now find common ground. youtu.be/D6OmGl9EFXg?si… #verification #MixedSignal @Cadence #semiEDA #analog #multidie #semiconductor

youtube.com

YouTube

Changes In Mixed-Signal IC Verification

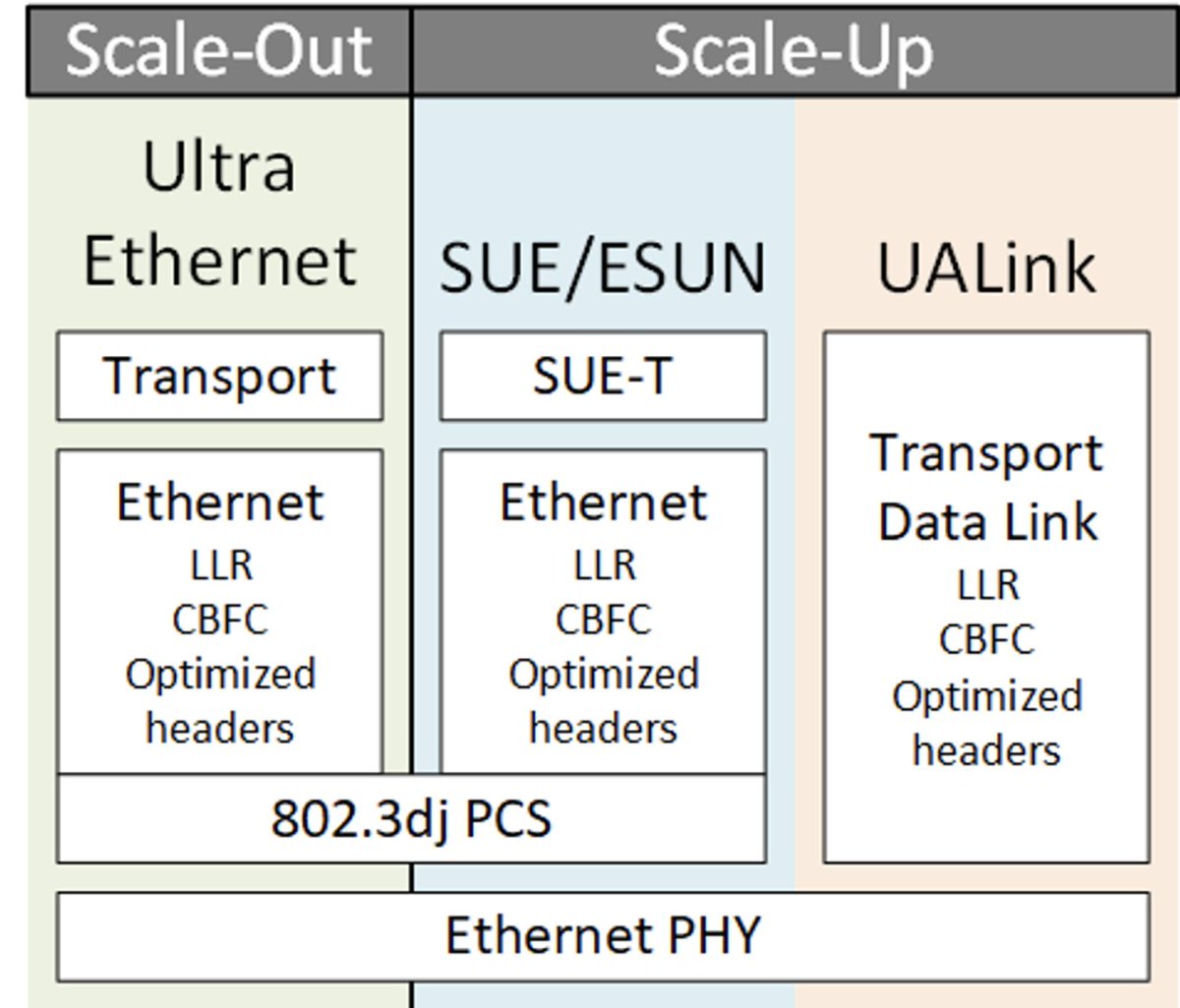

Multiple AI Scale-Up Options Emerge semiengineering.com/multiple-ai-sc… As data center infrastructures adapt to evolving workloads, parts of Ethernet can be found in scale-up approaches. #AIworkloads #datacenters #ScaleUp @OpenComputePrj #UALink #Ethernet #UltraEthernet #ESUN

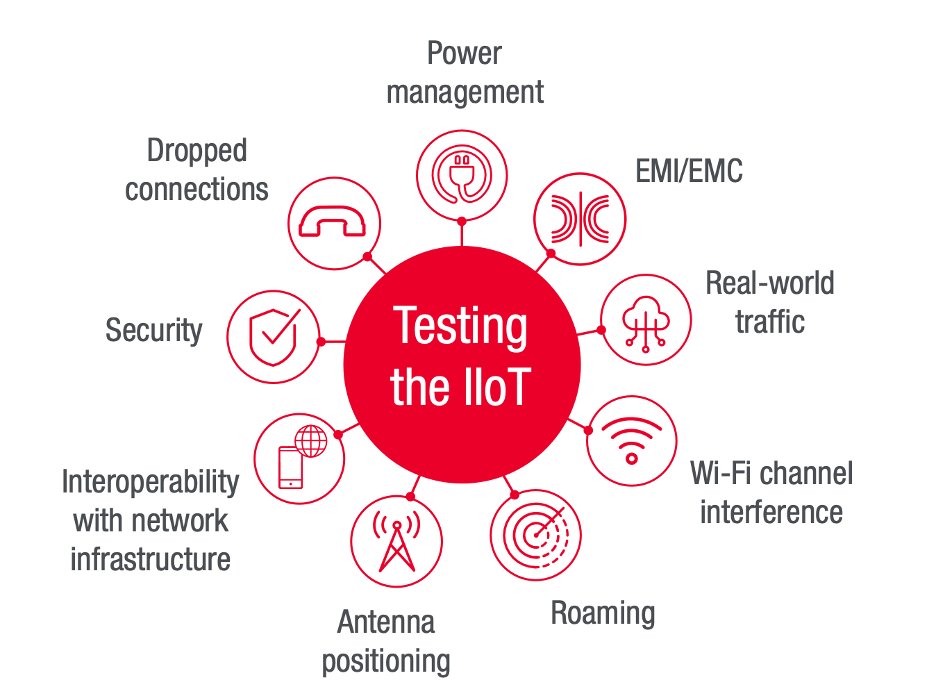

Multi-modal sensors generate data that edge AI can turn into actionable insights, provided new devices can be integrated with legacy equipment. semiengineering.com/edge-ai-is-sta… #IIoT #EdgeAI #sensors #semiconductor #AI #edgecomputing #LLMs

Special Report: Noise has always been important to communications experts, but it’s quickly becoming an issue that every semiconductor designer has to contend with. Some chips already have been compromised. semiengineering.com/noise-a-chip-k… #semiconductor #noise #EM

Latest: Memory chip shortages prompt price increases; Israeli chip foundry; 2 acquisitions; Baidu’s AI chips; IBM’s new quantum processor; GF’s GaN push; 3D NAND scaling boosters; SiPho and SiGe capacity; EV deal; agentic AI attack & more semiengineering.com/chip-industry-… #semiconductor

New technical papers recently added to Semiconductor Engineering’s library semiengineering.com/chip-industry-… #semiconductor

Improving IC System Quality And Performance: How production analytics can improve performance and reliability of chips over time. youtu.be/uMzlMWEesFU?si… #semiconductor #semiconductortest @ProteanTecs #DataAnalytics #defects

youtube.com

YouTube

Improving IC System Quality And Performance

HBM stands at the forefront of multiple technology developments as a critical enabler of AI, but it is one of the most difficult modules to manufacture. semiengineering.com/hbm-leads-the-… #HBM #HBM3 #HBM4 #microbumps #semiconductor #inspection #AI

United States 趋势

- 1. Michigan 103K posts

- 2. Buckeyes 7,008 posts

- 3. Bo Jackson N/A

- 4. #GoBlue 6,993 posts

- 5. Ryan Day 3,809 posts

- 6. #TheGame 3,025 posts

- 7. Barham 1,059 posts

- 8. Florida 105K posts

- 9. Texas 185K posts

- 10. #SmallBusinessSaturday 2,831 posts

- 11. Kentucky 17.1K posts

- 12. Julian Sayin 1,182 posts

- 13. Go Bucks 2,764 posts

- 14. Gus Johnson N/A

- 15. Donaldson 1,215 posts

- 16. Leeds 32.5K posts

- 17. Foden 20.7K posts

- 18. Grade 3 3,198 posts

- 19. Big House 8,947 posts

- 20. Ann Arbor 3,345 posts

你可能会喜欢

-

SemiWiki

SemiWiki

@DanielNenni -

Semiconductor Digest

Semiconductor Digest

@Semi_Dig -

ChipEstimate

ChipEstimate

@chipestimate -

Semiconductor Today

Semiconductor Today

@Semiconductor_T -

Global Semiconductor Alliance (GSA)

Global Semiconductor Alliance (GSA)

@GlobalSemi -

DAC, The Chips to Systems Conference

DAC, The Chips to Systems Conference

@DACconference -

Altera

Altera

@AlteraFPGA_ -

SEMI

SEMI

@SEMIconex -

IEEE Symposium on VLSI Technology and Circuits

IEEE Symposium on VLSI Technology and Circuits

@VLSI_2026 -

EDN: Voice of the Engineer

EDN: Voice of the Engineer

@EDNcom -

Synopsys

Synopsys

@Synopsys -

CHIPSAlliance

CHIPSAlliance

@CHIPSAlliance -

Ed Sperling

Ed Sperling

@Chip_Insider -

EE Times | Electronic Engineering Times

EE Times | Electronic Engineering Times

@eetimes -

Electronic Design

Electronic Design

@ElectronicDesgn

Something went wrong.

Something went wrong.