Adam Taylor

@ATaylorFPGA

FPGA and Embedded Systems expert, Experienced #System, #Hardware, #FPGA designer. Views My Own

You might like

How about a FPGA community? This could be interesting to share knowledge / learning and help each other. I just created one, link below!

Just caught up on the budget, so when is the emergency budget Q1 or Q2 next year?

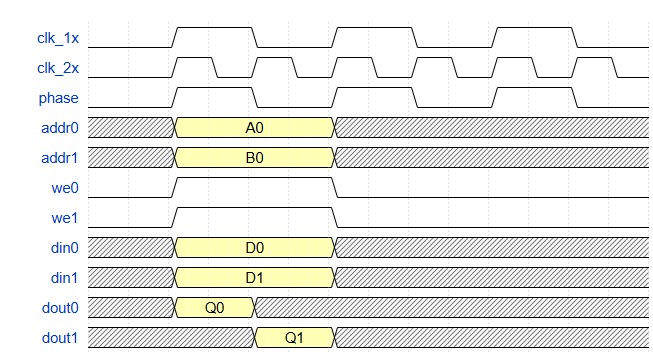

There are several techniques we can use to leverage the underlaying performance of the FPGA fabric to achieve excellent performance while still optimising for resource usage. RAM Double Pumping is one, those techniques which I explore in this weeks blog. adiuvoengineering.com/post/microzed-…

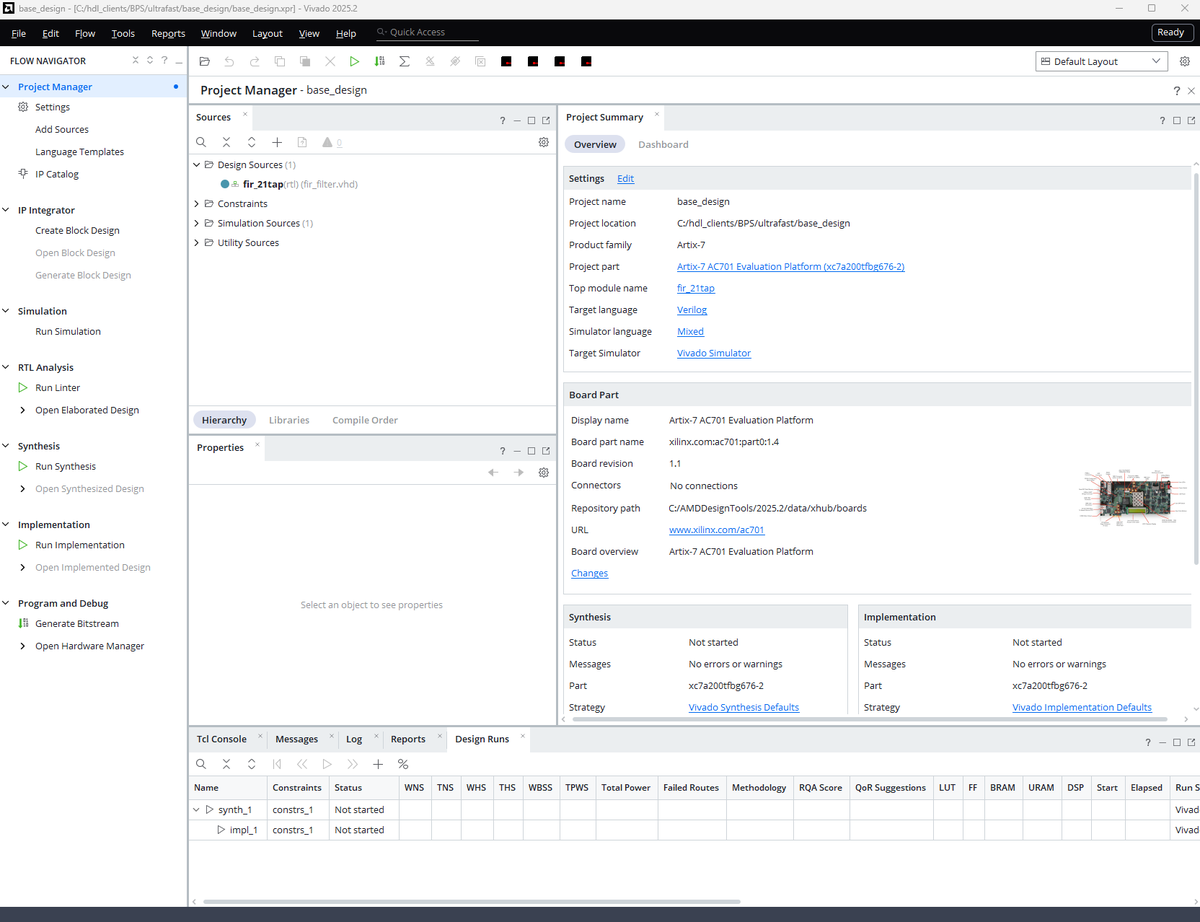

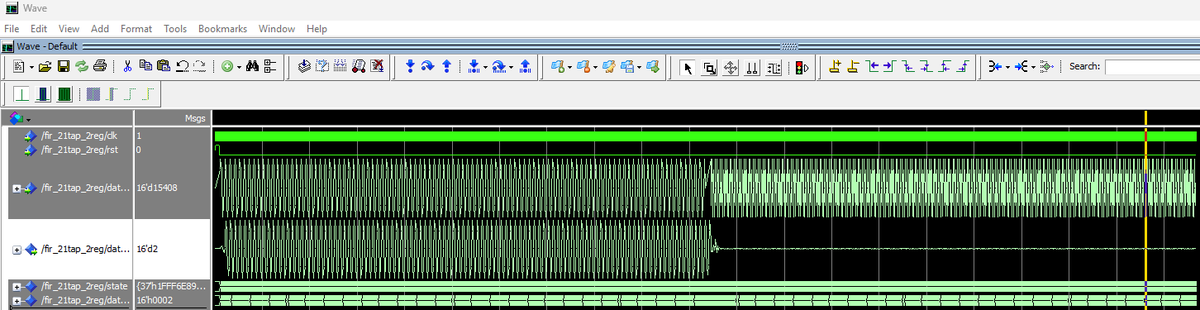

Little late night fun with FIR Filters . Upper waveform is input and lower waveform is output.

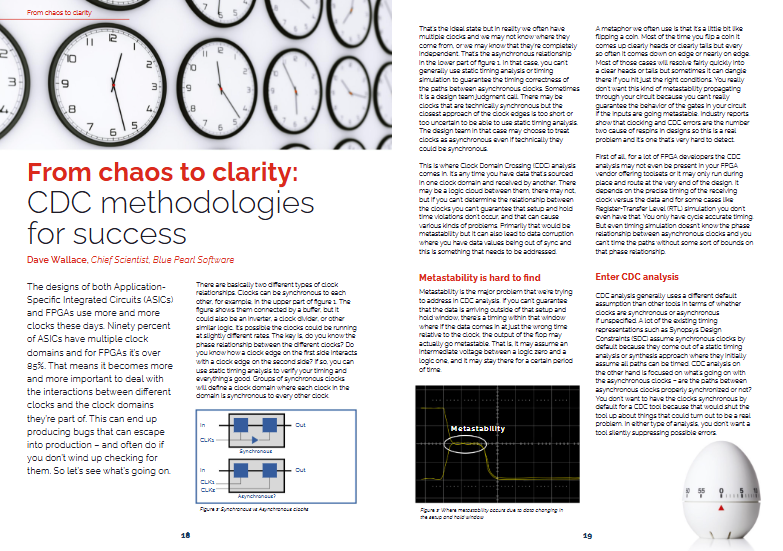

Clock Domain Cross can be a challenge in many designs, especially in modern designs with lots of AXI. Dave Wallace, the Chief Scientist at Blue Pearl Software wrote an excellent article about address this challenge in the FPGA Horizons Journal. Check it out…

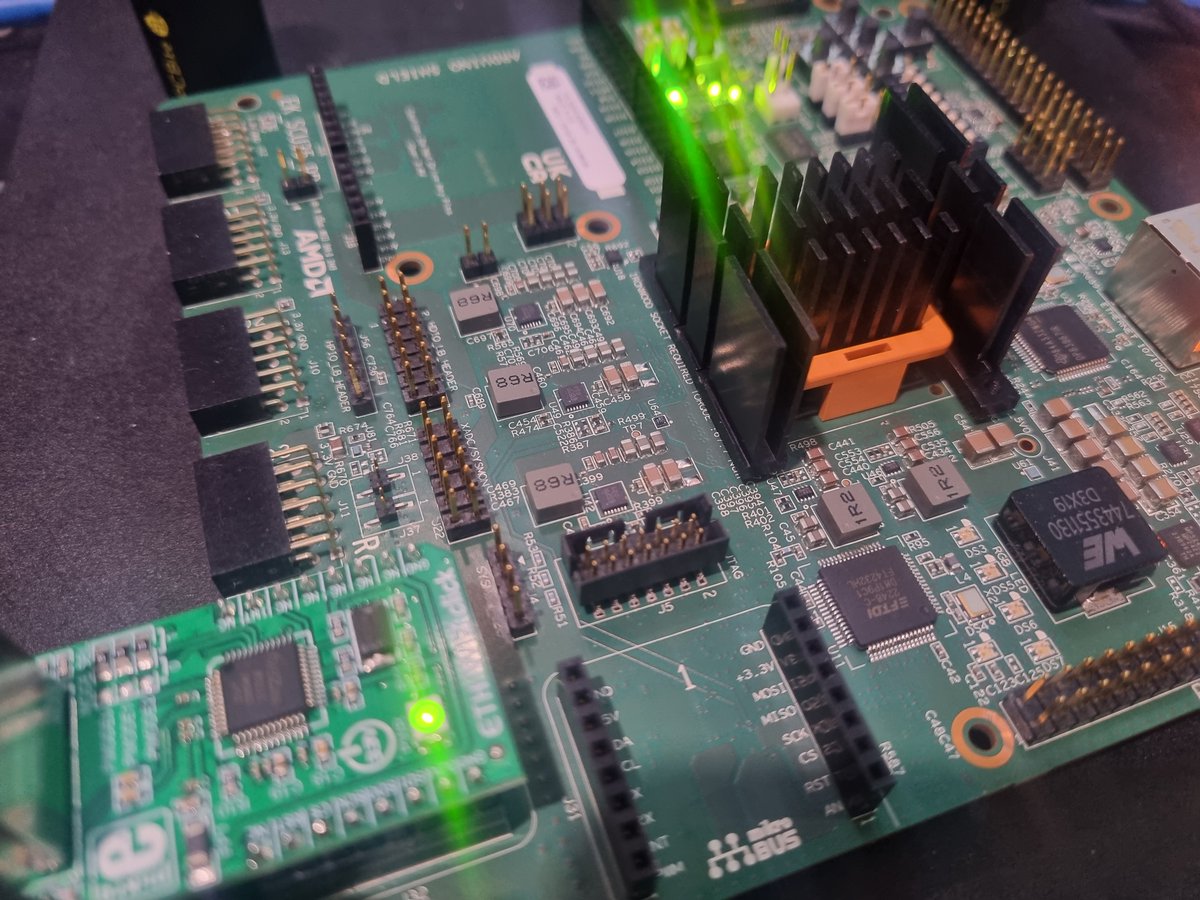

I needed a Alinx board for a clients project, I am always impressed with the boxes the boards come in.

I am very excited about the FPGA Horizons conferences in the US and UK next year. It really feels like we are growing a great technical FPGA event. If you missed the recently UK event, here is a short section of the Key Note from Kirk Saban at AMD talking about 40 Years of FPGA.…

Like many I have been looking at AI and how we can use in the development flow. In co-operation with Japeto, we have been developing a solution to use AI to verify requirements have been correctly implemented in our RTL. This provides a spotlight which can be used for debugging…

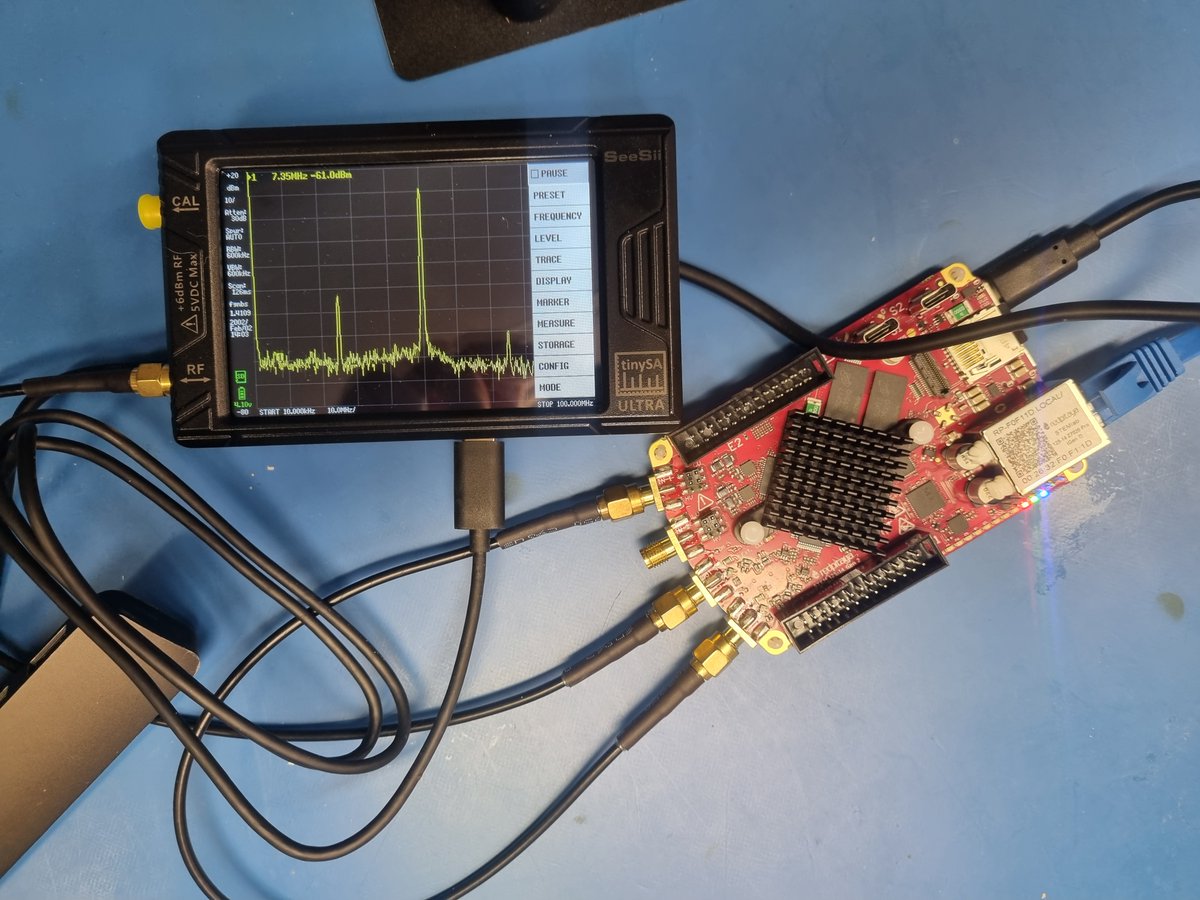

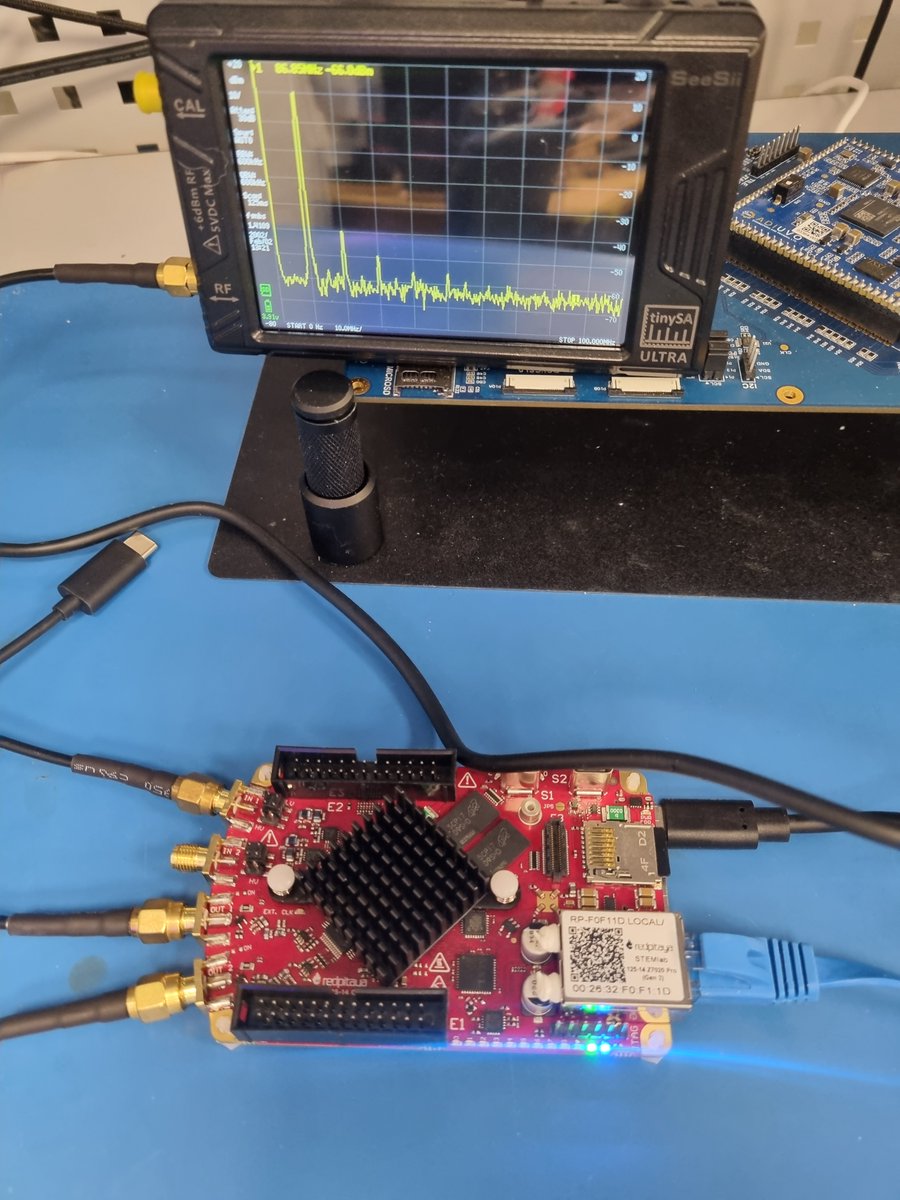

Fun with the Red Pitaya Gen2 and Tiny Spectrum Analyser Ultra.

I am off to buy a boat!

If this engineering lark fails I think I would make a good sea captain

Just arrived at a large defence company to talk to them about AI in FPGAs. Feels very odd as 9 years ago I was an executive here and walked out to do my own thing.

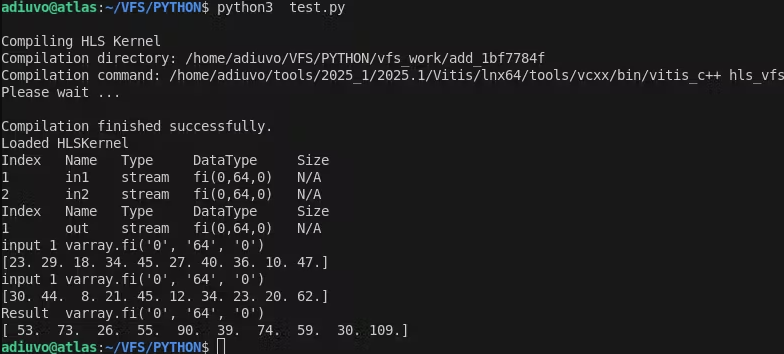

Did you know you can simulate your Vitis HLS and AIE Kernels using Python and Matlab? My latest Hackster project demonstrates how we can use Python for functional simulation of HLS Kernels. Check it out, it is incredibly simple to implement and work with and saves a lot of time.…

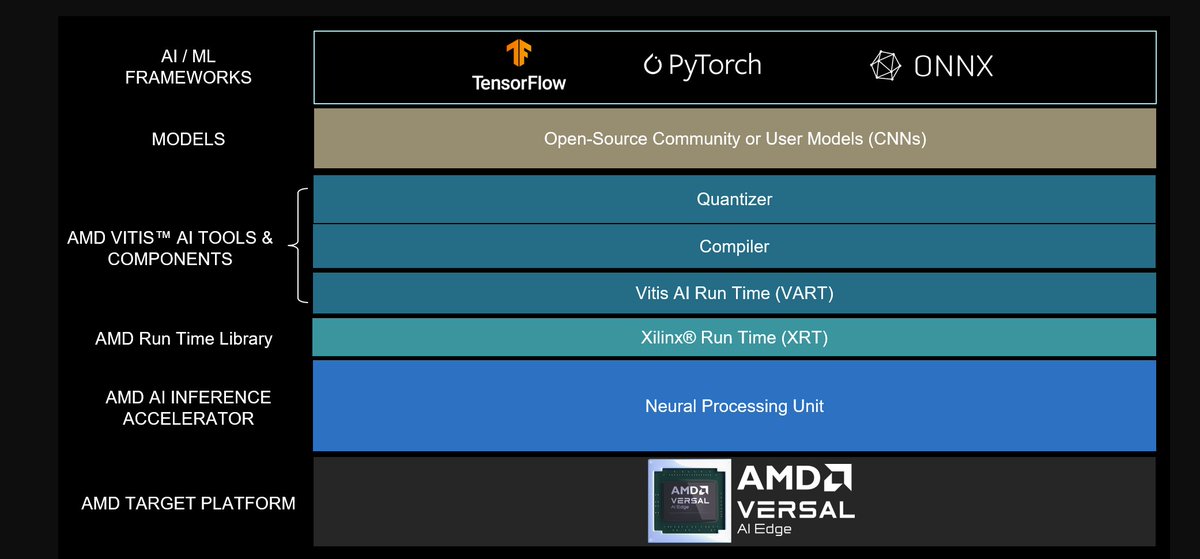

Vitis AI 5.1 was recently released as a public Beta. Vitis AI 5.1 is very interesting as it introduces the Neural Processing Unit which combines PL and AIE to accelerate Inference. Initially targeting Versal AI Edge devices, I thought I would take a look at it on the VEK280.…

Want to know about FPGA and HFT? we recorded all the talks at FPGA Horizons London 25 and they are available fpgahorizons.com/london-25/lond… Here is a short teaser.

I have spent the afternoon looking at Spartan UltraScale+ fabric performance, it is impressive. I am still working on fine tuning but, you can take an existing design and get it working much faster easily. This gets interesting as a higher clock rate means we can create more…

Unboxing videos are boring right? I do not think I have ever watched one.

Versal AI Edge Twins - The VEK280 with the Versal AI Edge VE2802 and the Alinx VD100 with the VE2302. Exploring the Versal AIE-ML tiles.

Just had to change the 9V battery in my multimeter. I bought this literally last century when I was doing my degree. The tipex and my name written on was in case it went wondering in the uni lab.

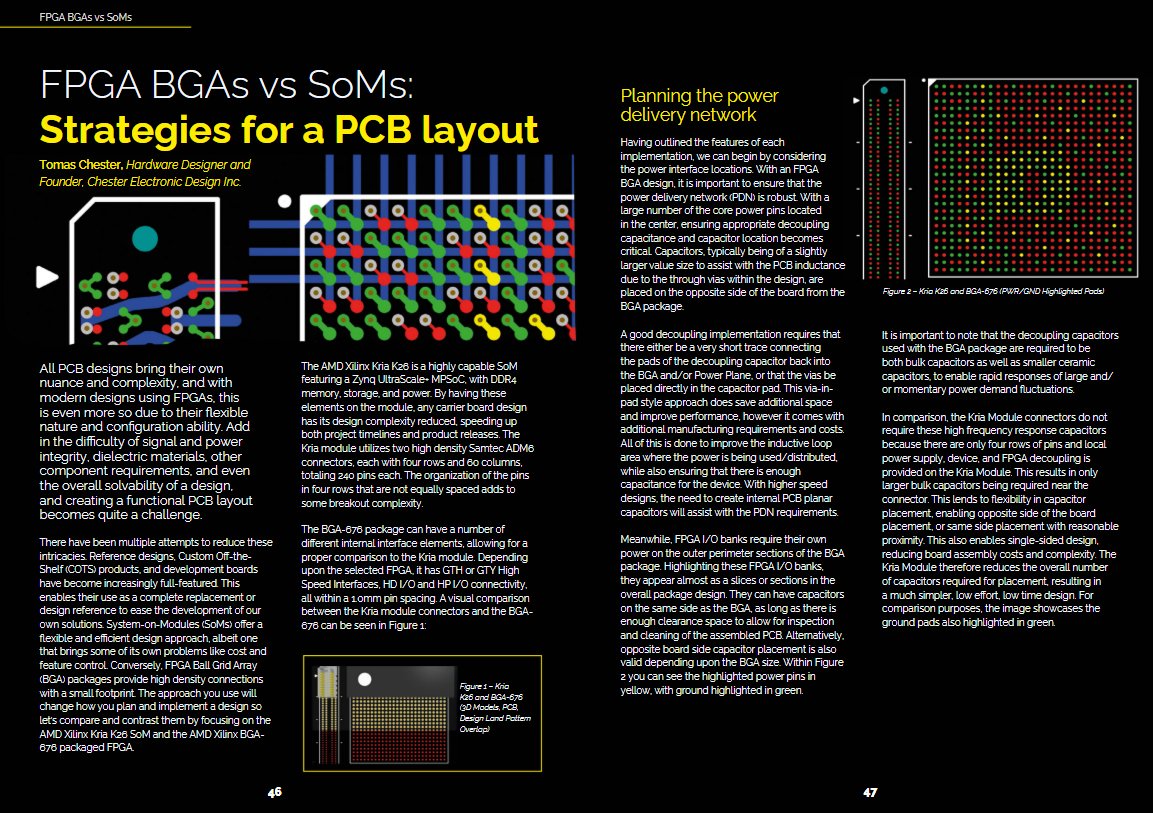

Chip down design or SOM for your next FPGA development? IT can be an interesting discussion. Tomas Chester's looks at the different strategies which can be used for chip down and SoM based approaches in his FPGA Horizons article. issuu.com/fpga-horizons/…

United States Trends

- 1. Thanksgiving 377K posts

- 2. Golesh 1,860 posts

- 3. Fani Willis 10.4K posts

- 4. Trumplican 2,642 posts

- 5. Hong Kong 76.5K posts

- 6. Stranger Things 158K posts

- 7. #TejRan 4,152 posts

- 8. Riker N/A

- 9. Khabib 6,045 posts

- 10. Ruth 14K posts

- 11. Elijah Moore N/A

- 12. Tom Hardy 1,044 posts

- 13. Pete Skandalakis N/A

- 14. NextNRG Inc N/A

- 15. #Wednesdayvibe 3,519 posts

- 16. #sstvi 47.1K posts

- 17. Nuns 10.4K posts

- 18. #wednesdaymotivation 6,584 posts

- 19. Ribs 11.7K posts

- 20. #WednesdayWisdom 1,192 posts

You might like

-

Pablo Trujillo

Pablo Trujillo

@controlpaths -

Sipeed

Sipeed

@SipeedIO -

Machdyne UG

Machdyne UG

@machdyne -

Mirosław Folejewski (Mirkotronics)

Mirosław Folejewski (Mirkotronics)

@Mirko_DIY -

logic destroyer

logic destroyer

@splinedrive -

Antmicro

Antmicro

@antmicro -

Zip CPU

Zip CPU

@zipcpu -

Marcelo Samsoniuk

Marcelo Samsoniuk

@samsoniuk -

Lukas Henkel

Lukas Henkel

@QVHenkel -

Hans Baier @[email protected]

Hans Baier @[email protected]

@hansfbaier -

Charles Eric LaForest, PhD

Charles Eric LaForest, PhD

@elaforest -

Weston Braun

Weston Braun

@WestonBraun -

CPU Duke

CPU Duke

@duke_cpu -

OpenEmbed

OpenEmbed

@Open_Embed -

CHIPSAlliance

CHIPSAlliance

@CHIPSAlliance

Something went wrong.

Something went wrong.