ultraembedded

@ultraembedded

CPU designs, digital HW IP, emulation and embedded system projects

你可能会喜欢

I think I've built myself an HD (720p50) video player out of an #FPGA, #RISCV, #MJPEG and 27,000 lines of Verilog! Going from 800x600 -> 1280x720 just worked with 10 more MHz! I actually plan to sit down and watch a movie on this one evening! github.com/ultraembedded/…

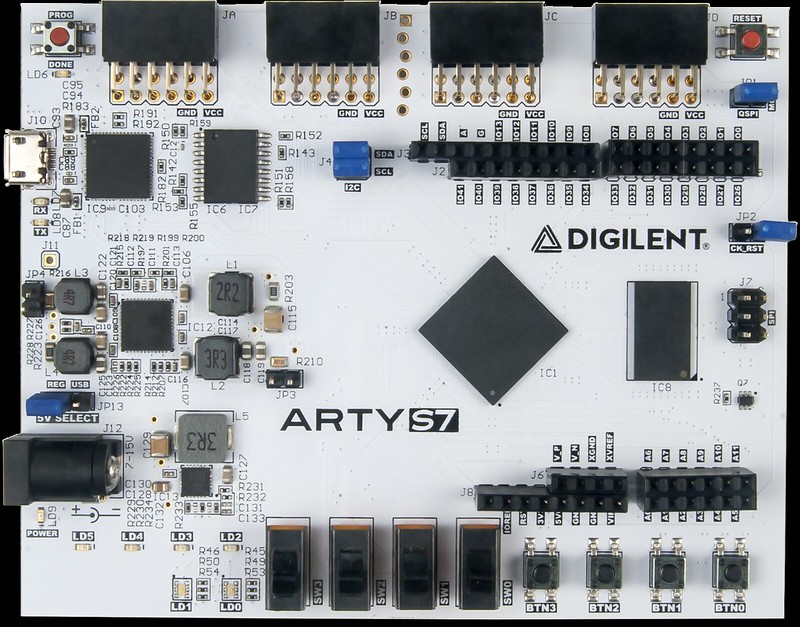

I couldn’t resist - just ordered a zynq 7020 and another ArtyA7 😀

Tuesday's #CyberWeek2021 deal is a doozie - we're giving 50% (yes, half off) of ANY Arty board featuring @XilinxInc tech. We call it "The Arty of the Deal". fal.cn/3kf0W

How to create your own FPU at home, new #femtorv32 tutorial on how 'petitbateau' floats ! github.com/BrunoLevy/lear…

Great news! The Ph.D. thesis of our Ariane guru Florian @be4web is now online! You can find it in the Research Collection of ETH Zurich under the title "Energy-Efficient High-Performance Computing" research-collection.ethz.ch/bitstream/hand…

The FPGA Minecraft clone is now open source! github.com/nickmqb/fpga_c…

#femtorv32-petitbateau Major refactoring, now FPU is a separate Verilog module (to ease reuse in other projects)

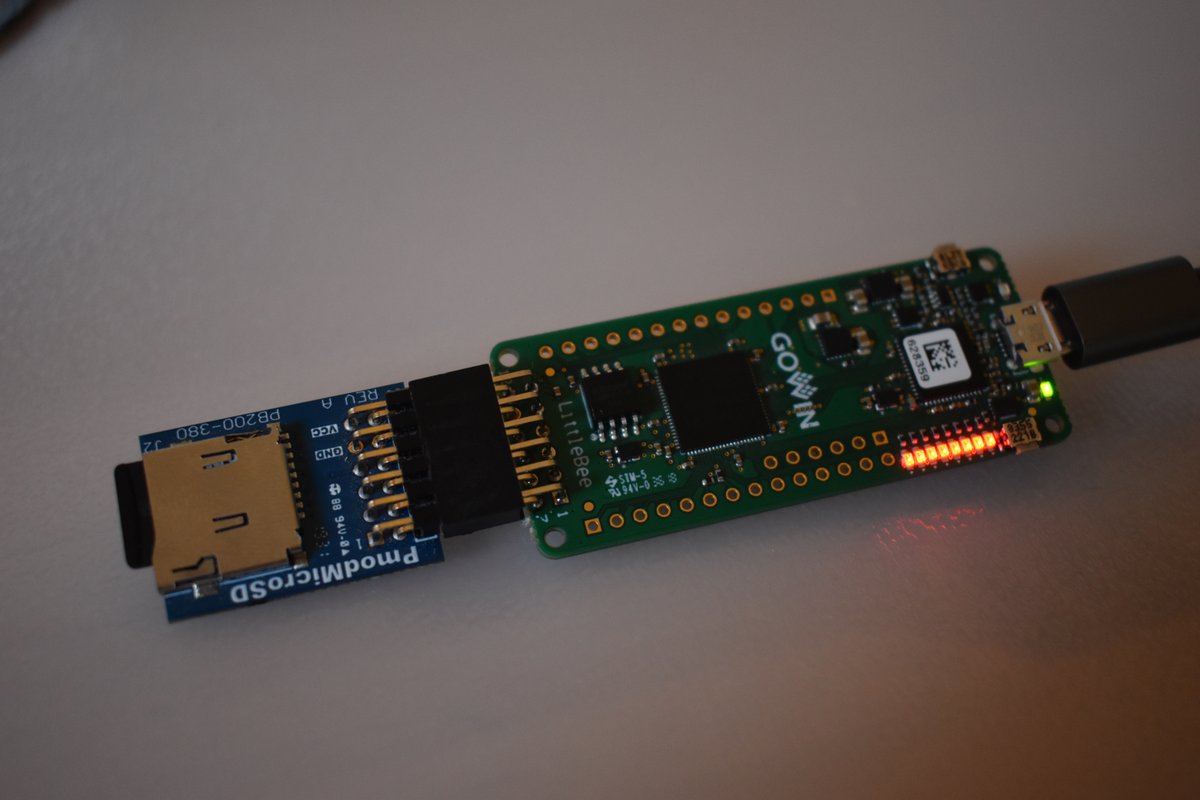

The minimal LiteX port of MicroPython is now available at github.com/litex-hub/micr… and can run on almost all boards supported by LiteX-Boards, want to try it? Here running on a @GOWIN_SEMI GW1NR9 with VexRiscv RV32IM + LiteDRAM (8MB embedded SDRAM) + boot from SPI SDCard.

Just adding an RTL project to opencores.org (not sure why really). How has that website languished in such a dire state for nearly 22 years?! Whoever owns it can't be making any money from it, so why not turn it over to the open-source community so it can fixed?

First attempt at using Yosys+nextpnr-xilinx today (for Artix7). Same design, but not really a fair bitstream build time comparison as Yosys was running on an Apple M1 (i.e. ARM64) vs Vivado on an i5-8500B. Xilinx doesn't do a Vivado ARM64 version, so 😀

Released another RISC-V core: github.com/ultraembedded/… It doesn't win any performance awards, but it is small, multi-cycle, RV32I+M, configurable, simple, and hopefully well verified. Not as small as @BrunoLevy01 #femtorv32, but 12x fewer LUTs than my dual-issue biRISC-V core!

OpenFPGALoader (by @GwenhaelG) loads bitstreams onto my ArtyA7 in half the time of that bloated whale Vivado... github.com/trabucayre/ope…

#Tensorflow lite model accelerated on the FPGA using dedicated CNN cores around our #lambdasoc and our #minerva RISC-V CPU. The demo uses our ECPIX5 board. blog.lambdaconcept.com/post/2021-06/f…

Silice #verilator framework update! All graphical #Silice demos (Doom-chip, Terrain, ...) simulate with on-screen display. Don't own an #FPGA yet? Simply `make verilator` and get started! 1/5 github.com/sylefeb/Silice… (special thanks to @WillFlux, see next)

United States 趋势

- 1. Texas 155K posts

- 2. 3-8 Florida 2,045 posts

- 3. #HookEm 10.5K posts

- 4. Austin Reaves 12K posts

- 5. Sark 5,038 posts

- 6. Arch 25.1K posts

- 7. Aggies 9,271 posts

- 8. Jeff Sims 1,657 posts

- 9. #JimmySeaFanconD1 227K posts

- 10. Georgia 48.9K posts

- 11. #DonCheadleDay 1,158 posts

- 12. Arizona 32.3K posts

- 13. Marcel Reed 4,439 posts

- 14. #LakeShow 3,504 posts

- 15. Elko 2,994 posts

- 16. SEC Championship 5,235 posts

- 17. Banana Fish 9,102 posts

- 18. Ole Miss 25.8K posts

- 19. Sylus 91K posts

- 20. Devin Vassell 2,395 posts

你可能会喜欢

-

YosysHQ

YosysHQ

@YosysHQ -

Flux

Flux

@WillFlux -

Enjoy Digital

Enjoy Digital

@enjoy_digital -

Matthew Venn

Matthew Venn

@matthewvenn -

Charles Eric LaForest, PhD

Charles Eric LaForest, PhD

@elaforest -

Zip CPU

Zip CPU

@zipcpu -

logic destroyer

logic destroyer

@splinedrive -

Luke Wren @[email protected]

Luke Wren @[email protected]

@wren6991 -

Tim 'mithro' Ansell

Tim 'mithro' Ansell

@mithro -

OpenHW Foundation

OpenHW Foundation

@OpenHWFdn -

Tom Verbeure

Tom Verbeure

@tom_verbeure -

CHIPSAlliance

CHIPSAlliance

@CHIPSAlliance -

Konrad Beckmann

Konrad Beckmann

@kbeckmann -

Marcelo Samsoniuk

Marcelo Samsoniuk

@samsoniuk -

YRabbit

YRabbit

@YLRabbit

Something went wrong.

Something went wrong.