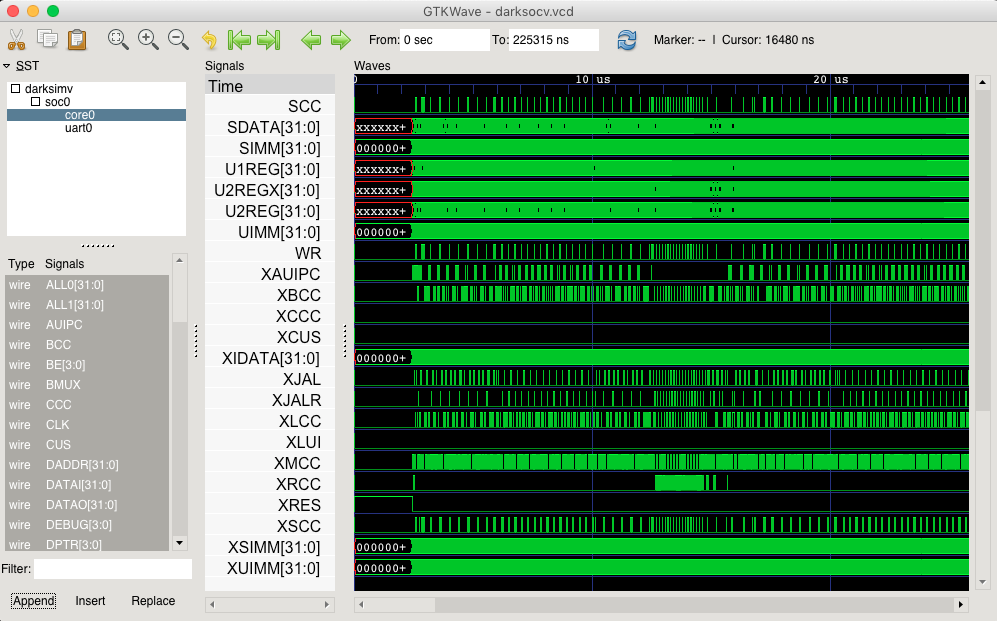

#gtkwave 搜尋結果

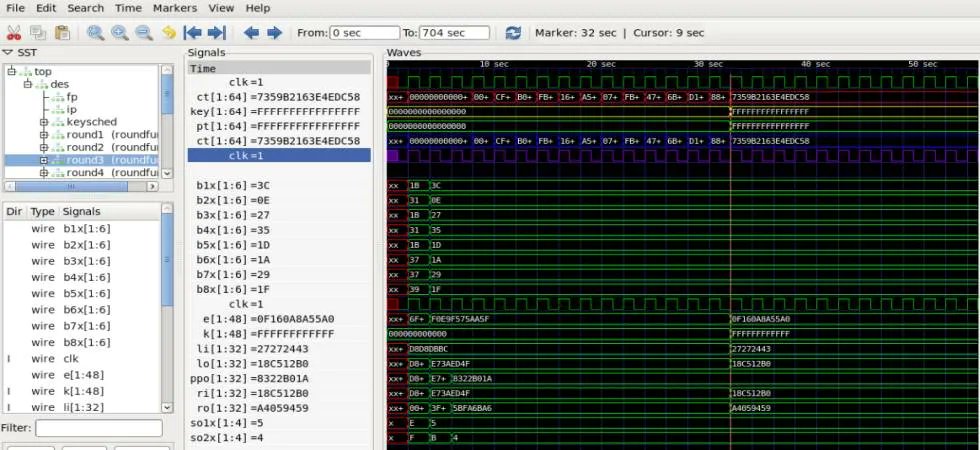

Today I have my first (ever!) #gtkwave FPGA simulation for the Verilog code driving the A/D & D/A board plugged into my @RadionaOrg ULX3S. 😎

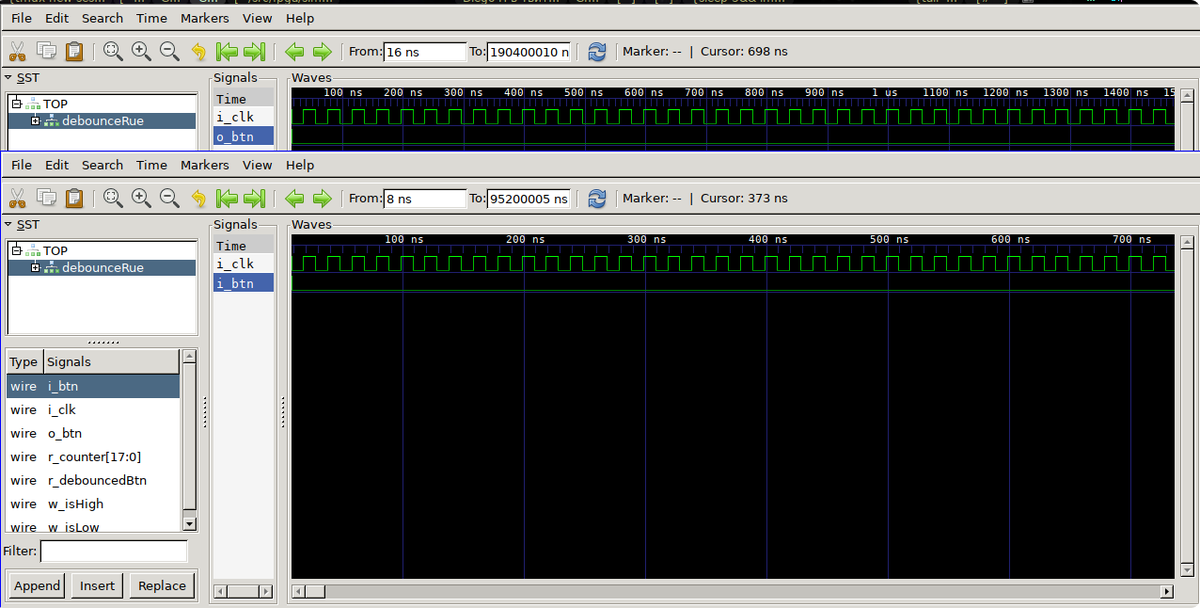

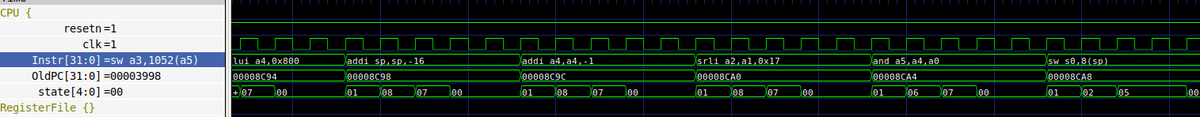

I was not so lucky with this utility: although it compresses well, but when I needed accurate tracking of time intervals, a surprise awaited me: the timeline when displaying the VCD and FST files in #gtkwave did not match. $ timescale 2ns $ VCD-upper window FST-lower window

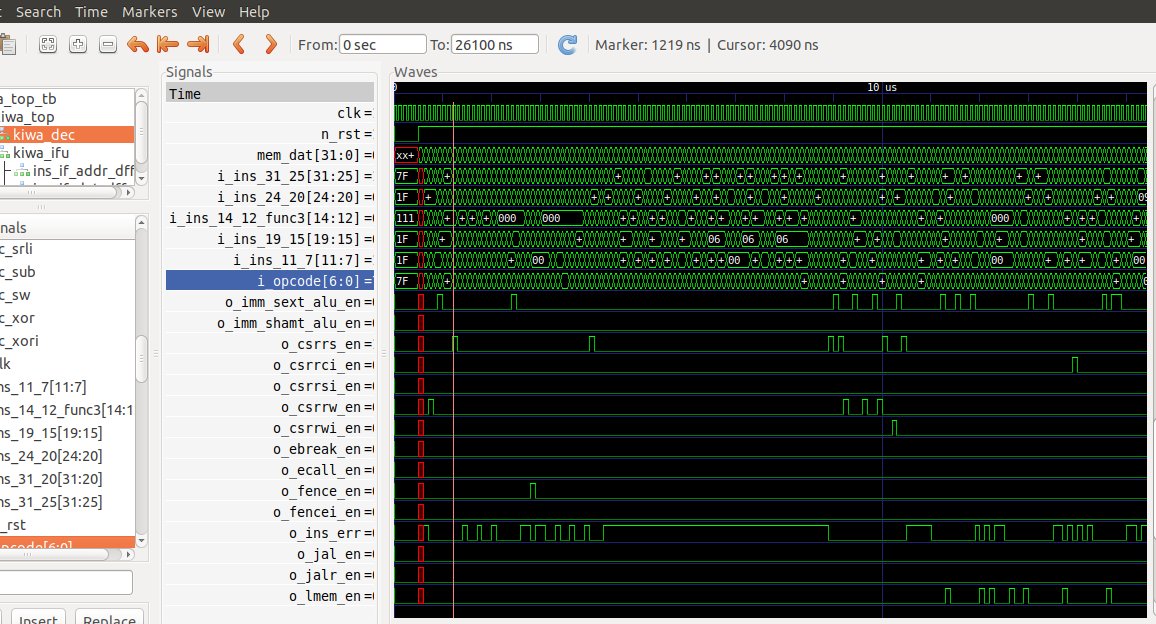

@matthewvenn Thanx for your riscv instruction filter for #gtkwave #verilog #vcd it helps me a lot today github.com/mattvenn/gtkwa…

Verilog garbage input does not result in garbage output stackoverflow.com/questions/6449… #verilog #fpga #gtkwave #vivado

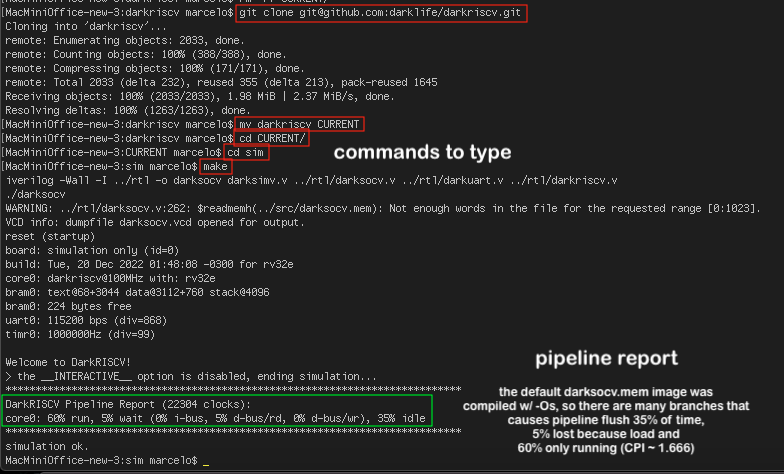

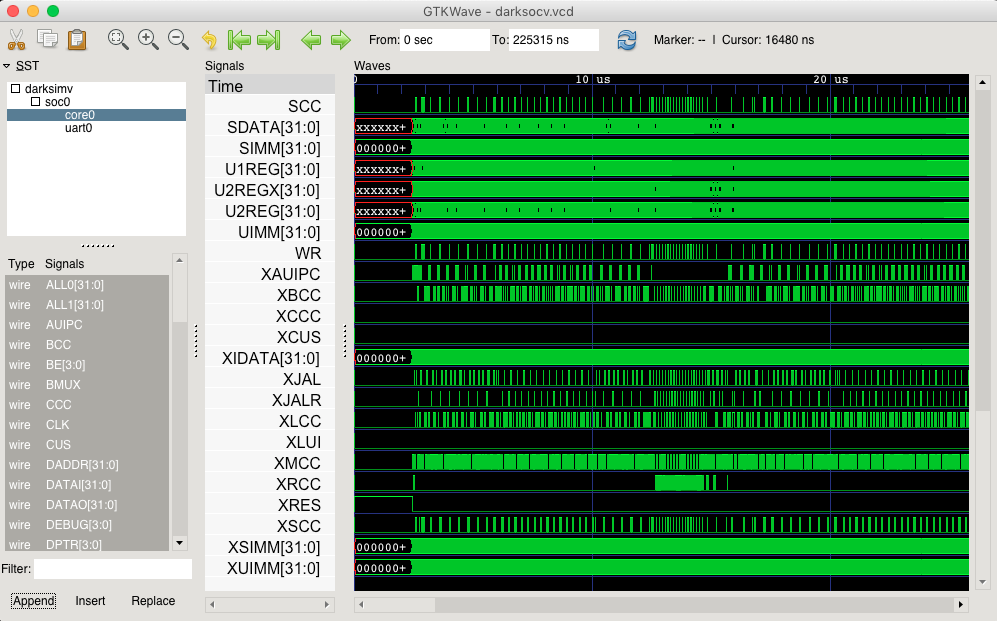

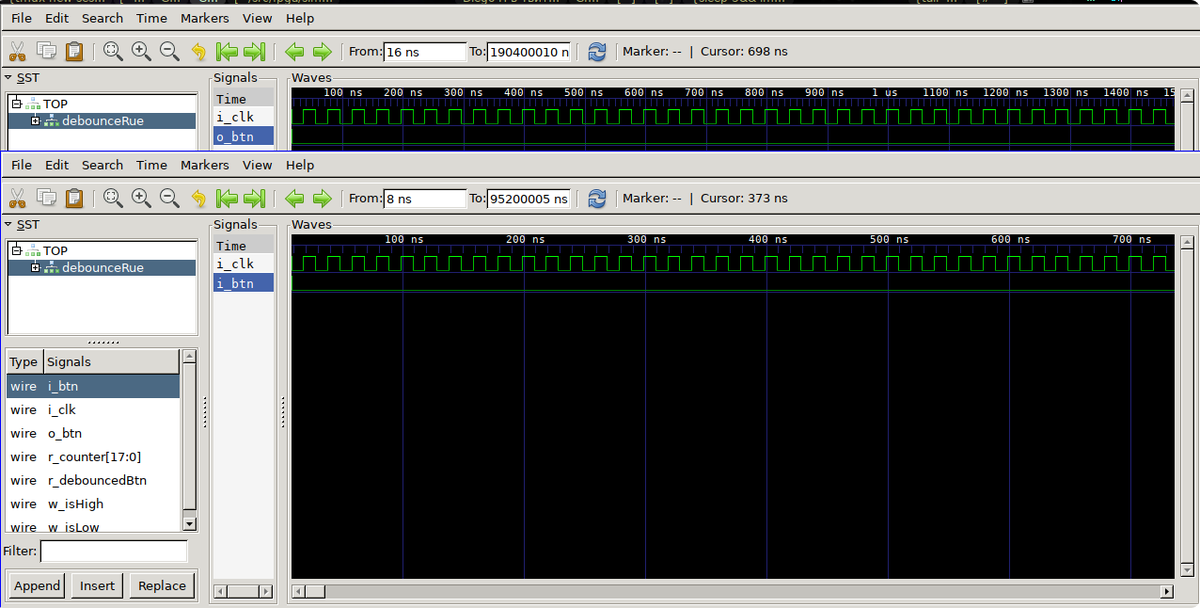

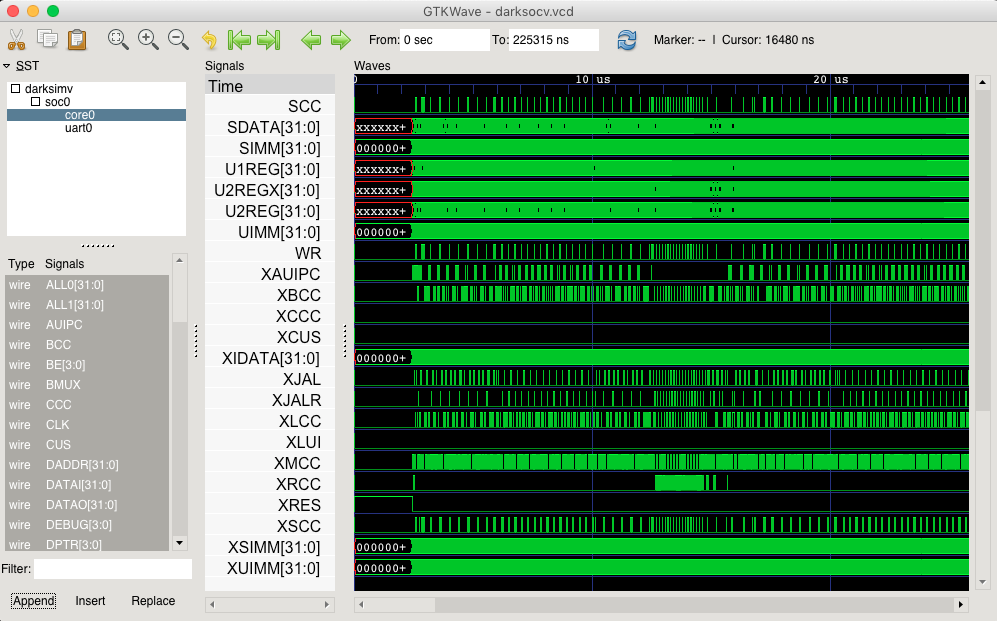

#DarkRISCV easy way: just git it from github.com/darklife/darkr…, enter in the sim directory and run make! you need #iverilog in the path and, case you have #gtkwave, you can use the VCD file and see the 3-stage pipeline working! ❤️

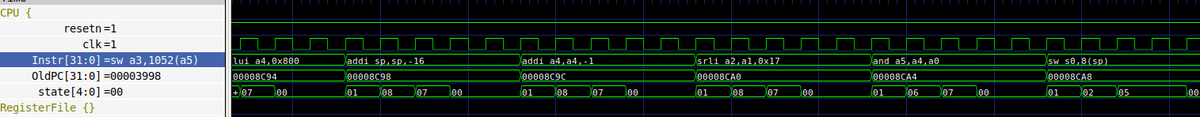

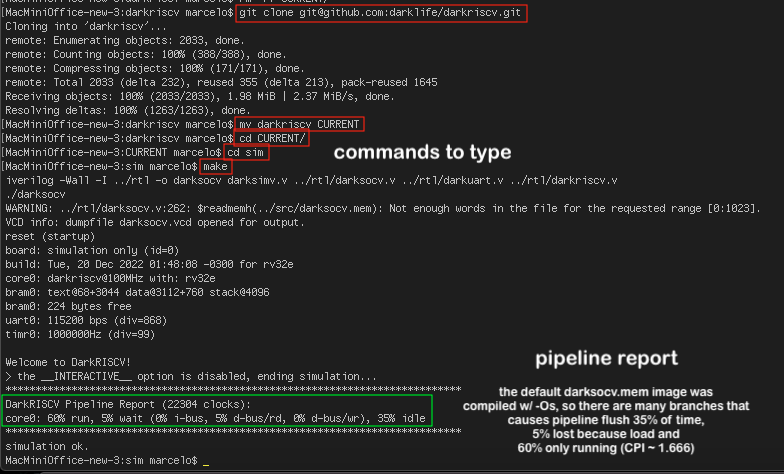

Feels good when the CPU you built from scratch is running instructions! #verilog #verilator #gtkwave #v30mz

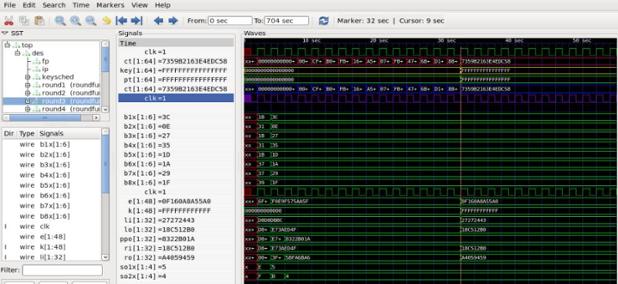

Simulation of SPI Master sending last 256 byte from ice40 BRAM to SPI/USB bridge. #Yosys, #iverilog and #GTKWave on #Linux - free and open source, made by awesome people. My friends were sceptical but I like the toolchain a lot (haven't really tried icecube and modelsim, no need)

A special thanks and shout-out to the #GTKWave maintainers for fixing this issue! If you struggle with this, you might wish to build GTKWave from github. github.com/gtkwave/gtkwave

[Rev:50ab2b38] formula added: gtkwave 3.3.18 http://bit.ly/gewL6h #machomebrew #gtkwave

[Rev:cc56f44c] formula updated: gtkwave 3.3.31 bit.ly/gewL6h #machomebrew #gtkwave

[A-409] #GTKWave 3.3.6 on Elettrolinux.com --> http://tinyurl.com/29dbaw3

Fun tip: If you are debugging a *LONG* trace, including a CPU running in a tight loop, you can display the program counter as an analog trace in #gtkwave--so you can quickly see when it leaves the loop even when expanded to thousands of cycles.

[A-1500] #GTKWave 3.3.17, #Flashrom 0.9.3, #USBPicProg 0.4.1 --> http://tinyurl.com/2vf76f7

Vigilance.fr #Vulnerability of #GTKWave: multiple vulnerabilities. #CyberSecurity vigilance.fr/vulnerability/…

vigilance.fr

Vulnerability about GTKWave: multiple vulnerabilities | Vigilance.fr

An attacker can use several vulnerabilities of GTKWave, identified by CVE-2023-32650, CVE-2023-34087, CVE-2023-34436.

Vigilance.fr #Vulnérabilité de #GTKWave : multiples vulnérabilités. #CyberSécurité vigilance.fr/vulnerabilite/…

Vigilance.fr #Vulnerability of #GTKWave: multiple vulnerabilities. #CyberSecurity vigilance.fr/vulnerability/…

vigilance.fr

Vulnerability about GTKWave: multiple vulnerabilities | Vigilance.fr

An attacker can use several vulnerabilities of GTKWave, identified by CVE-2023-32650, CVE-2023-34087, CVE-2023-34436.

Vigilance.fr #Vulnérabilité de #GTKWave : multiples vulnérabilités. #CyberSécurité vigilance.fr/vulnerabilite/…

We recently disclosed multiple vulnerabilities in #ManageEngine, #AVideo and #GTKwave that could lead to arbitrary code execution. More in our first Vulnerability Roundup of the year cs.co/6014reQU6

#DarkRISCV easy way: just git it from github.com/darklife/darkr…, enter in the sim directory and run make! you need #iverilog in the path and, case you have #gtkwave, you can use the VCD file and see the 3-stage pipeline working! ❤️

Which verilog simulator is your choice? #vivado #iverilog #gtkwave #modelsim #verilator #verilog #logic #design #fpga #asic

A special thanks and shout-out to the #GTKWave maintainers for fixing this issue! If you struggle with this, you might wish to build GTKWave from github. github.com/gtkwave/gtkwave

Today I have my first (ever!) #gtkwave FPGA simulation for the Verilog code driving the A/D & D/A board plugged into my @RadionaOrg ULX3S. 😎

@matthewvenn Thanx for your riscv instruction filter for #gtkwave #verilog #vcd it helps me a lot today github.com/mattvenn/gtkwa…

I was not so lucky with this utility: although it compresses well, but when I needed accurate tracking of time intervals, a surprise awaited me: the timeline when displaying the VCD and FST files in #gtkwave did not match. $ timescale 2ns $ VCD-upper window FST-lower window

Verilog garbage input does not result in garbage output stackoverflow.com/questions/6449… #verilog #fpga #gtkwave #vivado

Feels good when the CPU you built from scratch is running instructions! #verilog #verilator #gtkwave #v30mz

#DarkRISCV easy way: just git it from github.com/darklife/darkr…, enter in the sim directory and run make! you need #iverilog in the path and, case you have #gtkwave, you can use the VCD file and see the 3-stage pipeline working! ❤️

Simulation of SPI Master sending last 256 byte from ice40 BRAM to SPI/USB bridge. #Yosys, #iverilog and #GTKWave on #Linux - free and open source, made by awesome people. My friends were sceptical but I like the toolchain a lot (haven't really tried icecube and modelsim, no need)

Something went wrong.

Something went wrong.

United States Trends

- 1. Brian Cole 3,025 posts

- 2. #Kodezi N/A

- 3. Walter Payton 5,844 posts

- 4. Chronos 1,020 posts

- 5. Price 270K posts

- 6. #25SilverPagesofSoobin 25.2K posts

- 7. Merry Christmas 69K posts

- 8. Good Thursday 37.5K posts

- 9. $META 12.2K posts

- 10. The FBI 109K posts

- 11. #thursdayvibes 2,666 posts

- 12. #WPMOYChallenge 7,870 posts

- 13. #NationalCookieDay N/A

- 14. yihe N/A

- 15. Metaverse 8,038 posts

- 16. Dealerships 1,652 posts

- 17. Somali 250K posts

- 18. Hilux 11.2K posts

- 19. The Blaze 5,523 posts

- 20. Happy Friday Eve 1,107 posts