#yosys search results

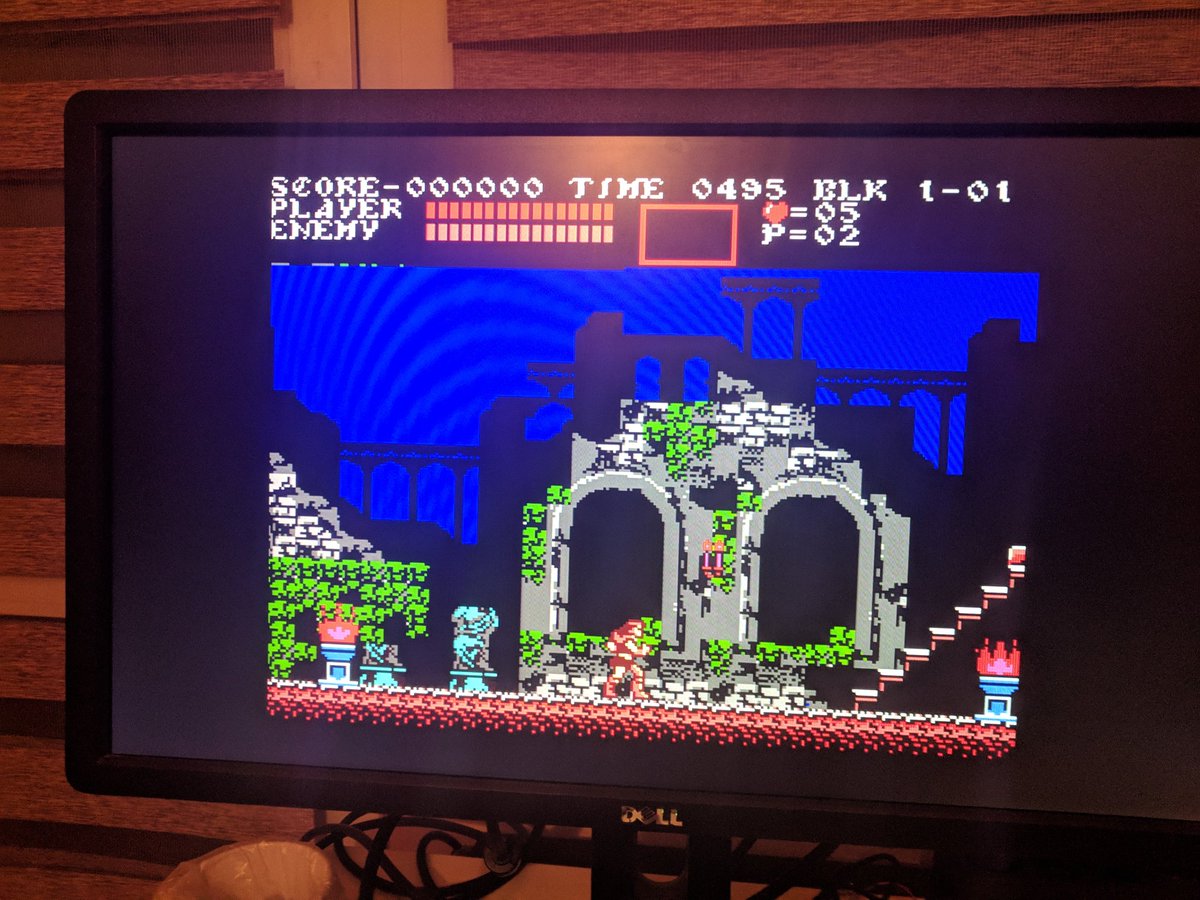

#femtorv32 running on the ULX3S, now at 60MHz. Using EHXPLLL. Can probably go faster. #yosys says "$glbnet$clk: 74.43 MHz max frequency". Anybody knows how to go faster ? (Started to read about clock distribution on the ECP5, but it seems complicated).

Introducing github.com/antonblanchard… - a generator of fast and efficient standard cell adders, multipliers and multiply-adders. Written in Amaranth HDL, formally verified with #Yosys. #Verilator verification too With @OpenROAD_EDA + ASAP7 7nm a 32bit 3 cycle multiplier hits 2.7GHz

An update on my #flamegraph FPGA resource usage experiment. I wrote a #yosys plugin to generate a flamegraph for each cell type used in the design and combine it all in a single HTML page

It blinks! Synthesis powered by #yosys #ghdl #vhdl on #pynq. Looking forward to #nextpnr #fpga #prjxray support 😊

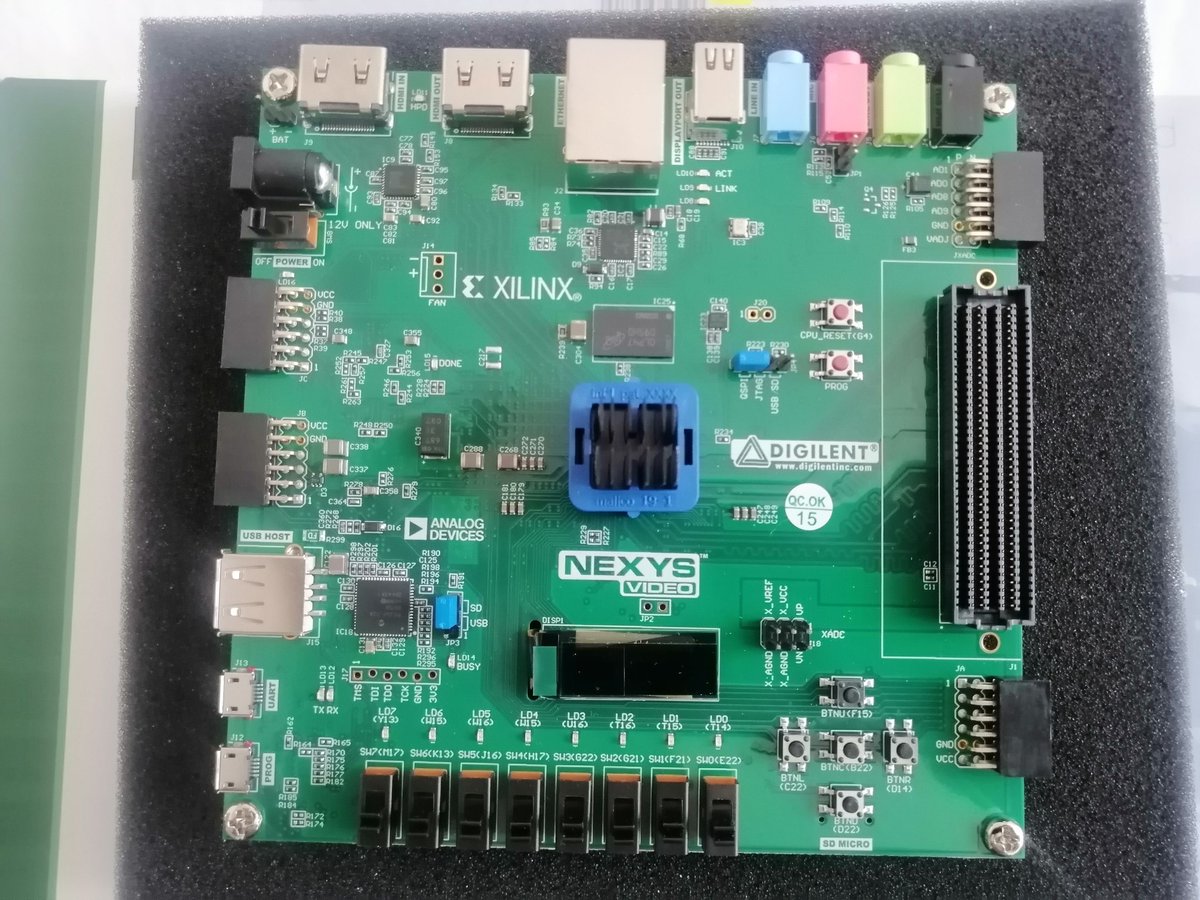

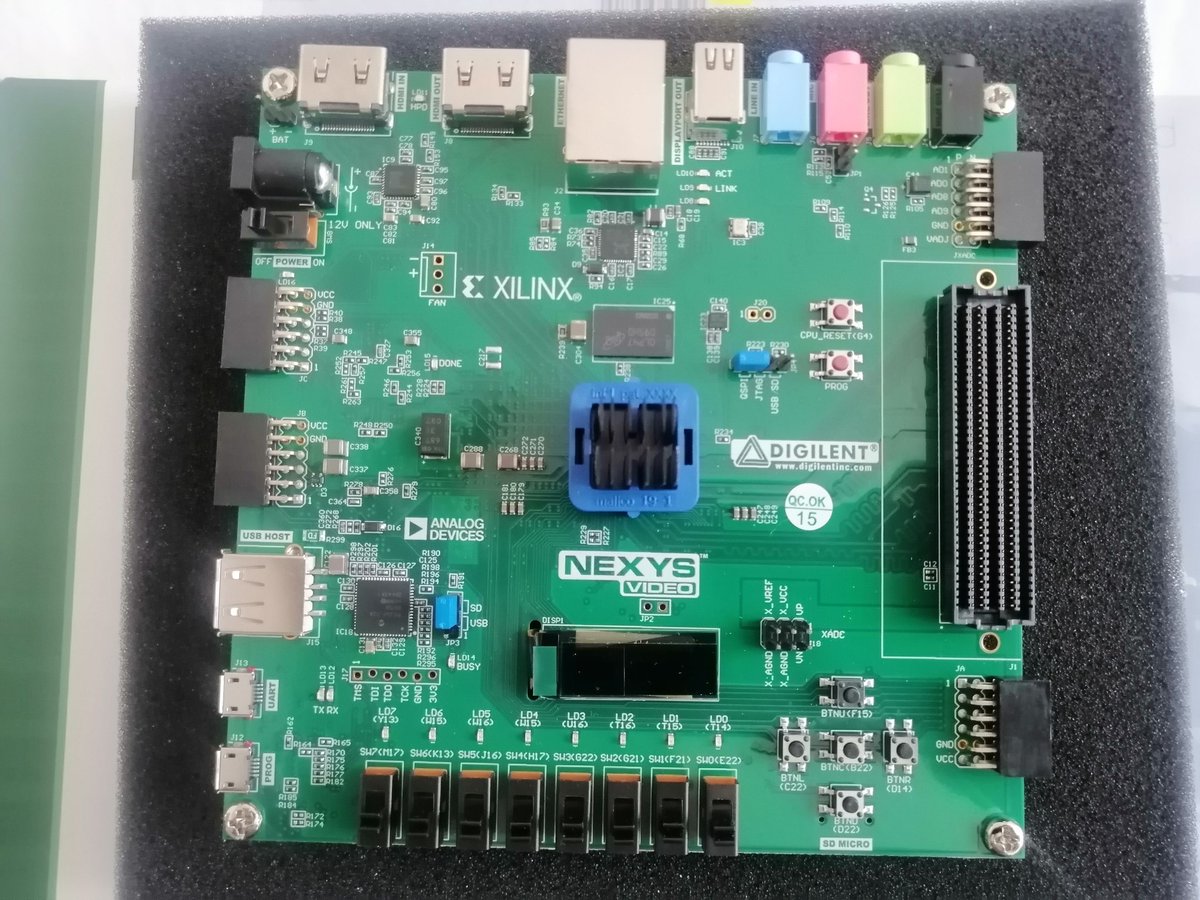

Finally, the Nexys Video board arrived for doing HW with Artix-7 fpga using Opensource EDA tools #Yosys #Symbiflow FuseSoC and learning languages such as #Chisel and #Amaranth hdl.

The new PnR architecture for gowin chips has flashing LEDs! The departure from the old Generic-based architecture was long overdue. Himbächel - a series of bigger arches github.com/YosysHQ/nextpn… #fpga #gowin #yosys

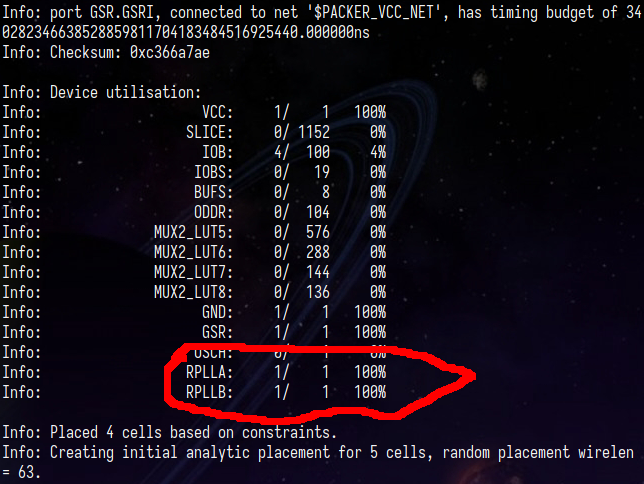

Running the PicoSoC in the Nexys Video using #Symbiflow. I'm astonished how automated is this toolchain. #FPGA #Yosys #Artix7

That's it, a full open source FPGA stack from @YosysHQ generating SERV, a @risc_v core by @OlofKindgren on a RISC-V host, the @SiFive Unmatched. Corescore was 100% built and programmed into @RadionaOrg ULX3S FPGA in RISC-V! Open source to the core! #RISCV #FPGA #Yosys #opensource

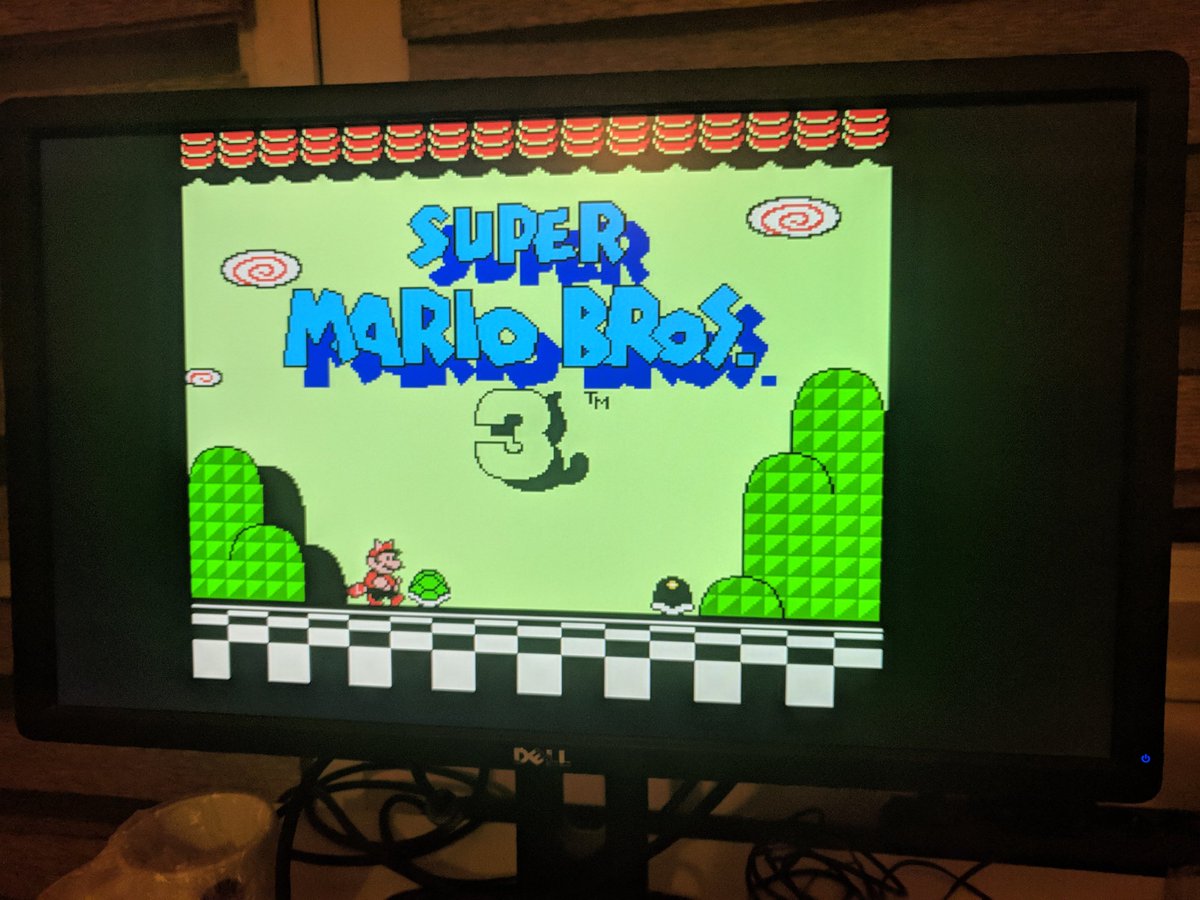

Switch back to #yosys and #ulx3s and run first time my new 5-staged pipelining #riscv cpu on ecp5 lattice fpga. CPU is written in SystemVerilog and I used sv2v transform it to verilog to have the possibility to synthesis it with yosys. Yosys works like hell in comparison to viva

How to define Verilog parameters at synthesis time (when using #yosys) buff.ly/2zqfKYh #FPGAwars #Verilog

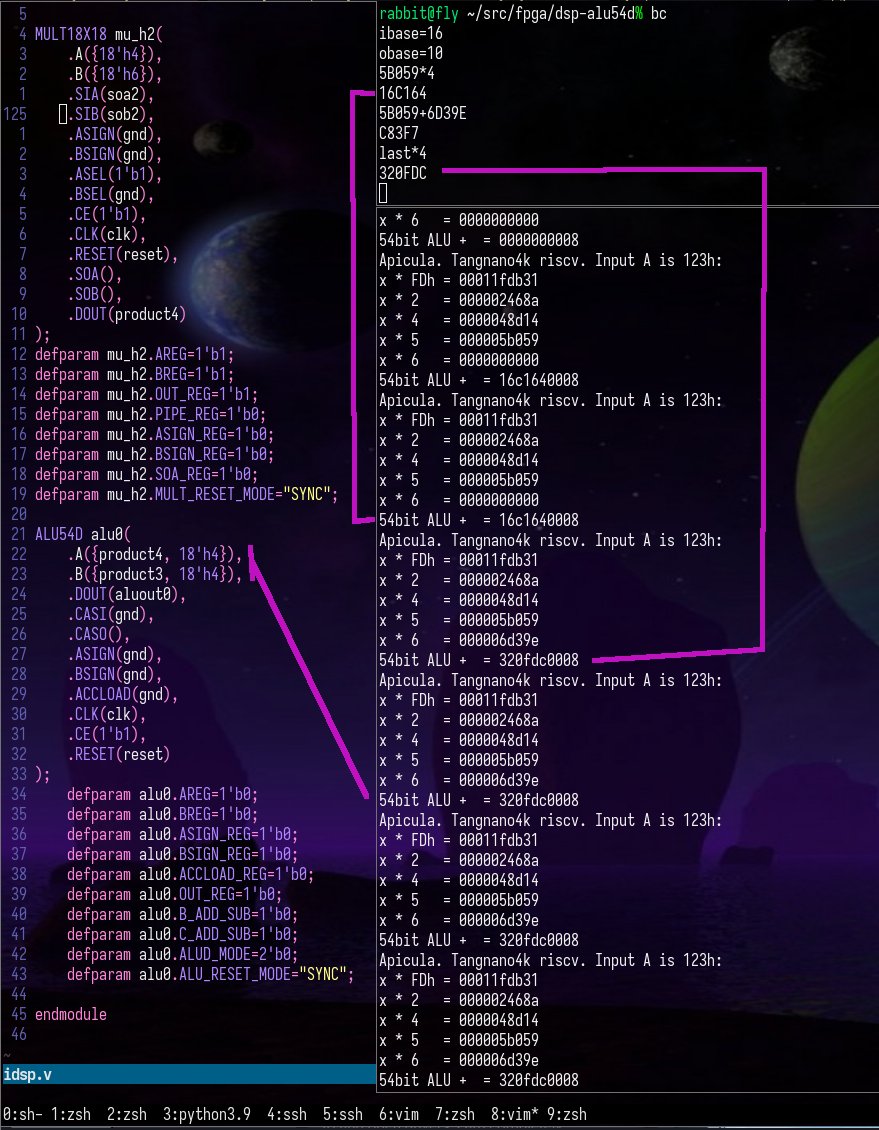

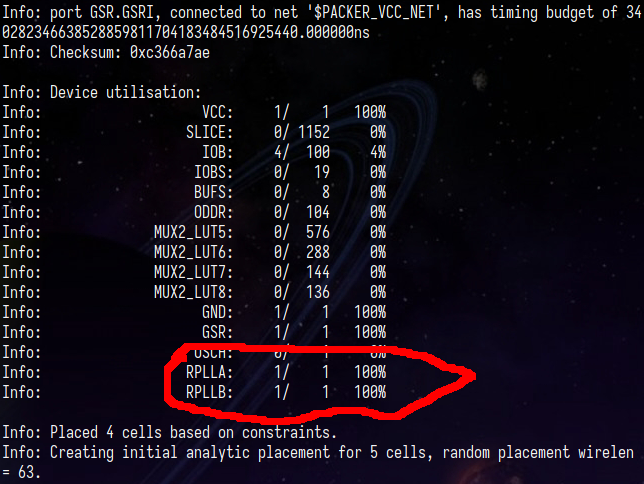

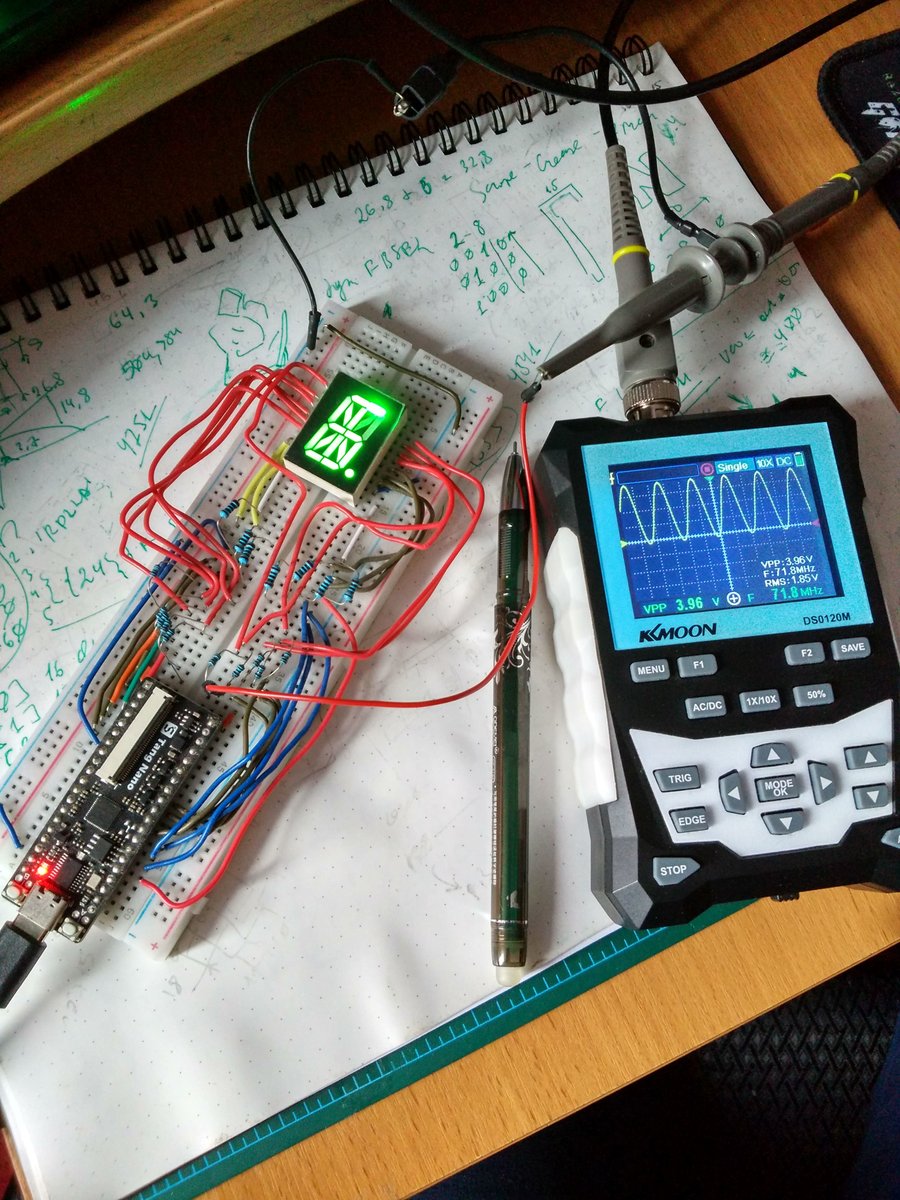

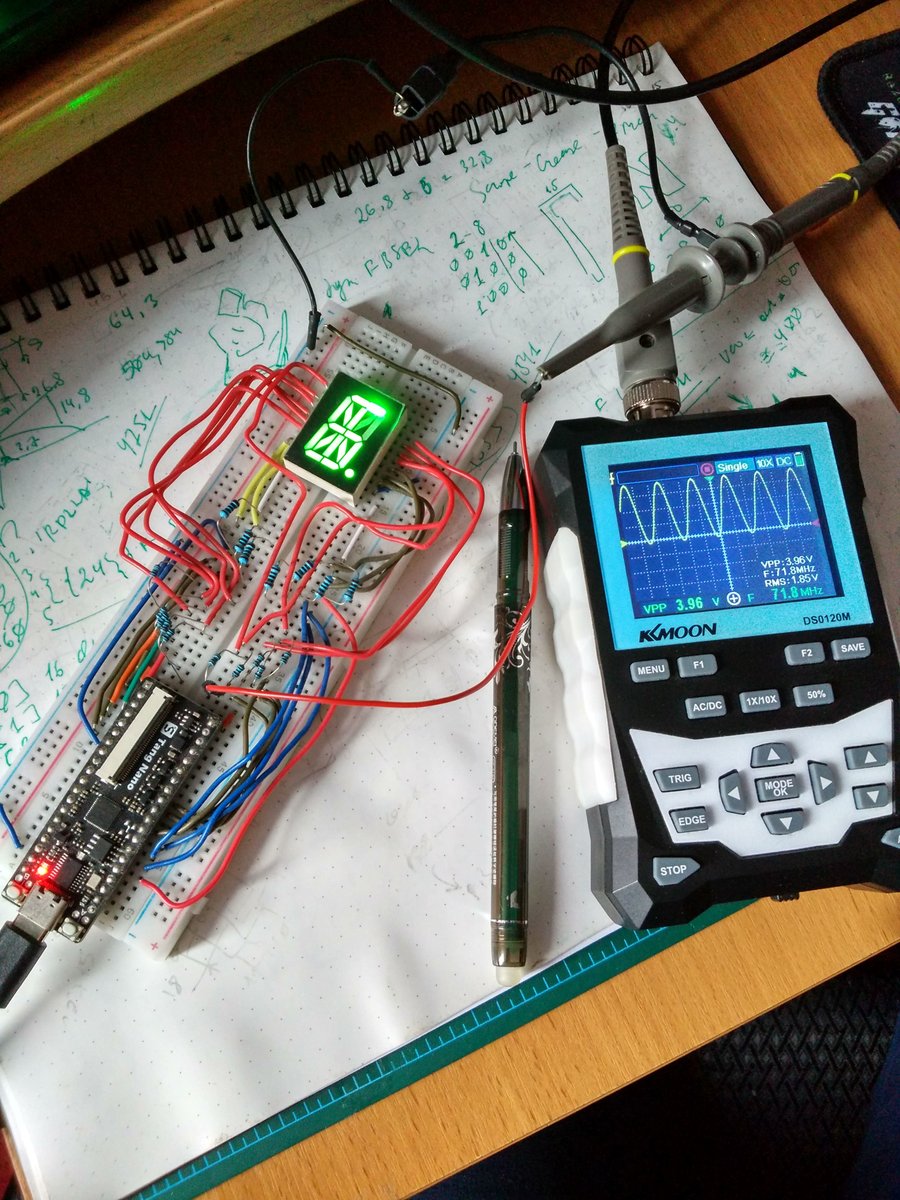

Gee! #yosys -> #nextpnr ->#gowin-pack successfully build and code a PLL primitive for #gowin #tangnano. The on-board quartz is 24MHz, the PLL generates ~72MHz Truly a great day! 😀 #apicula #fpga

#fpgafriday time for new #yosys #oss-cad-suite-build #iverilog #verilator #openfpgaloader #gtkwave.....github.com/YosysHQ/oss-ca… 💥💥💥💯💯❤️💯💥❤️❤️❤️❤️❤️❤️❤️💯💥💥💯💥💥💥💥❤️❤️💯❤️❤️💯❤️❤️💯❤️😕

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

So, I grew up with #Yosys/nextpnr... you want awesome... here's the new 5-stage pipelined CPU, Kianv StealthV, in action... live synthesis, place & route. Two firmware switches and a transformation from hardcore SystemVerilog to Verilog. Pure awesomeness! @YosysHQ

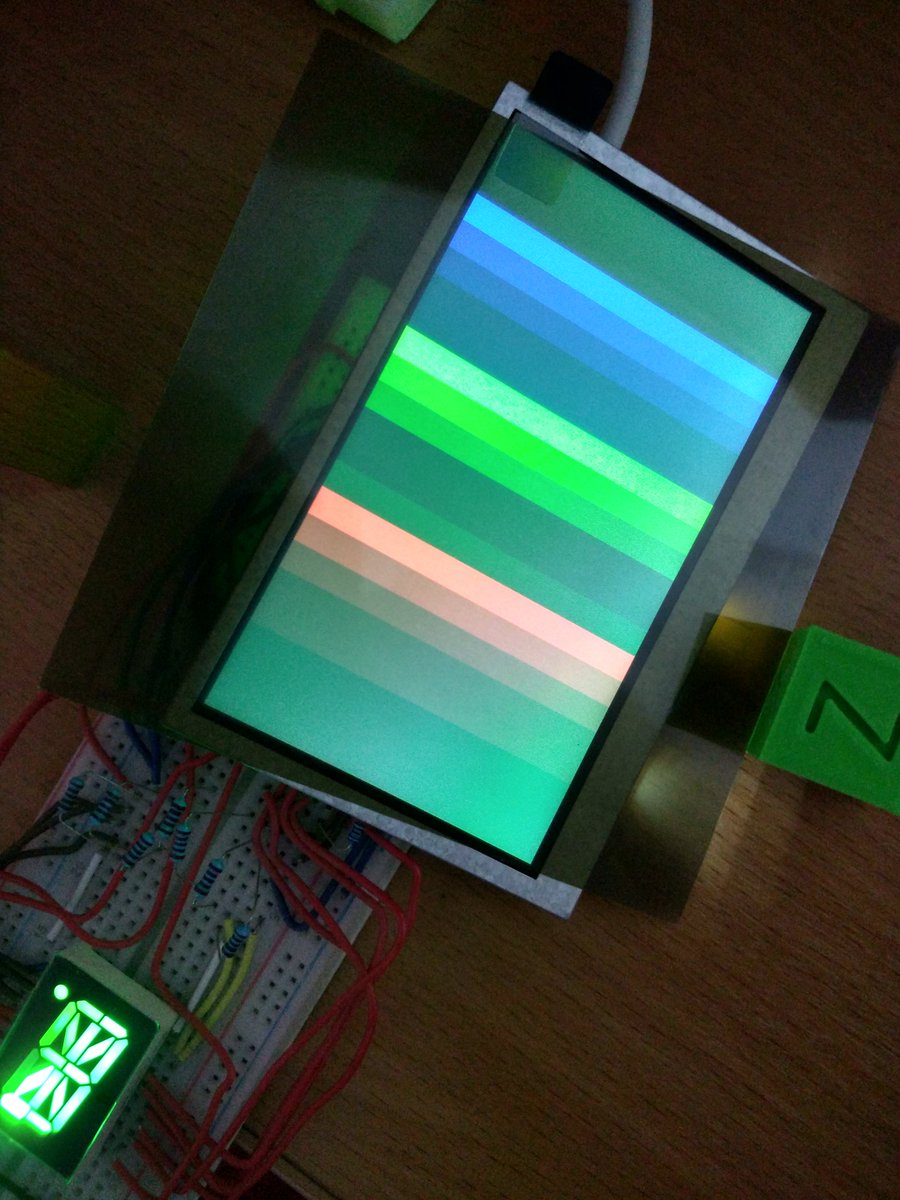

It has just come to my attention that the vendor IDE has a VGA example as part of it. So I just took it and compiled #yosys->#nextpnr->#apicula And marvel: no difference! The example uses PLL and it's the same source code! (almost) #fpga

So, now I have equipped my IceStick HX1K, which has 1280 LUTs, with my mini KianV processor + audio device. This was much easier than on my Unix SoC :). #FPGA IceStick music machine. @BrunoLevy01, we will also integrate this into your processor :) #verilog 4life #yosys

Testing the iCE40UP5K board with apio (development version). It is so easy to create and upload the bitstreams... 😀 Thanks OpenFPGA community!! #icestorm #yosys #openFPGA #FPGAwars

Gee! ADC went through #yosys and #nextpnr! Does it work on hardware? Absolutely not!🤣 #apicula#fpga#gowin#sipeed

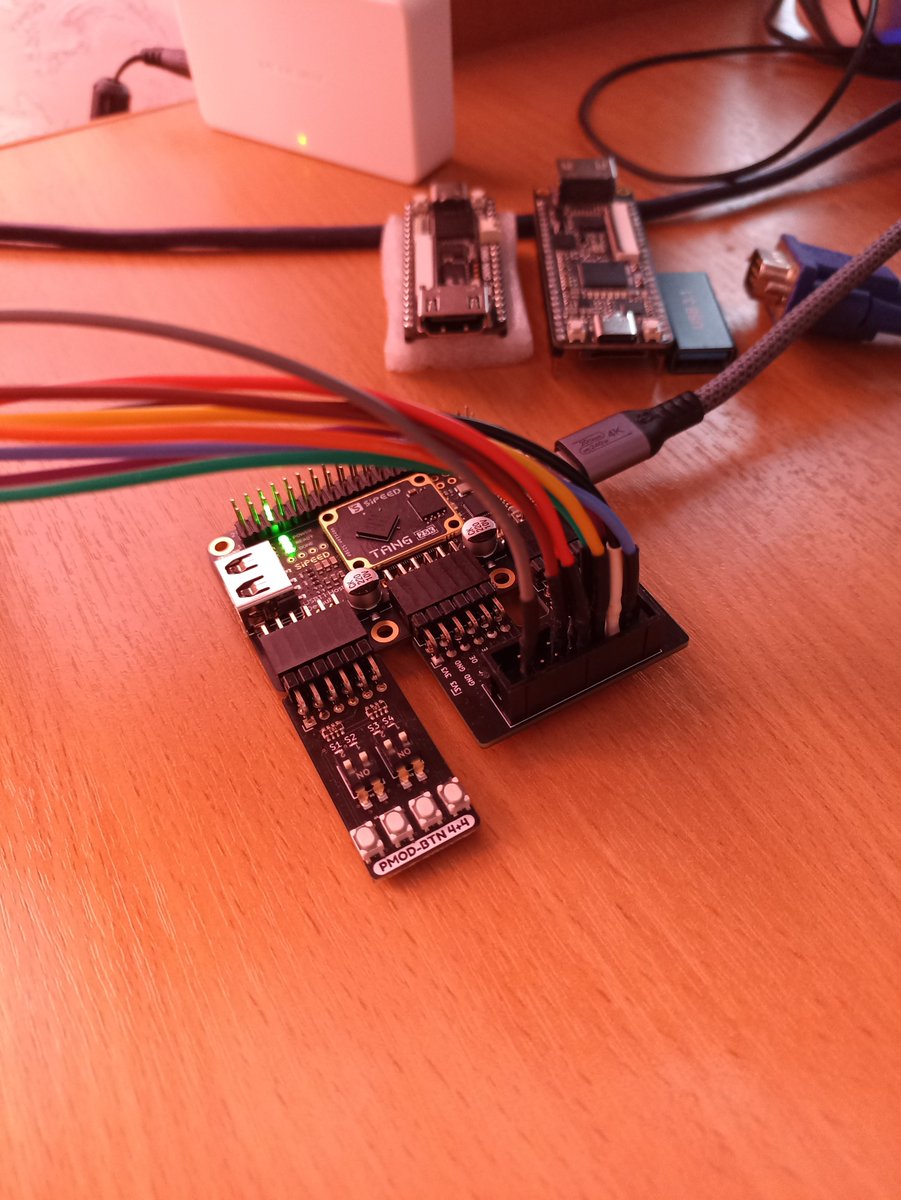

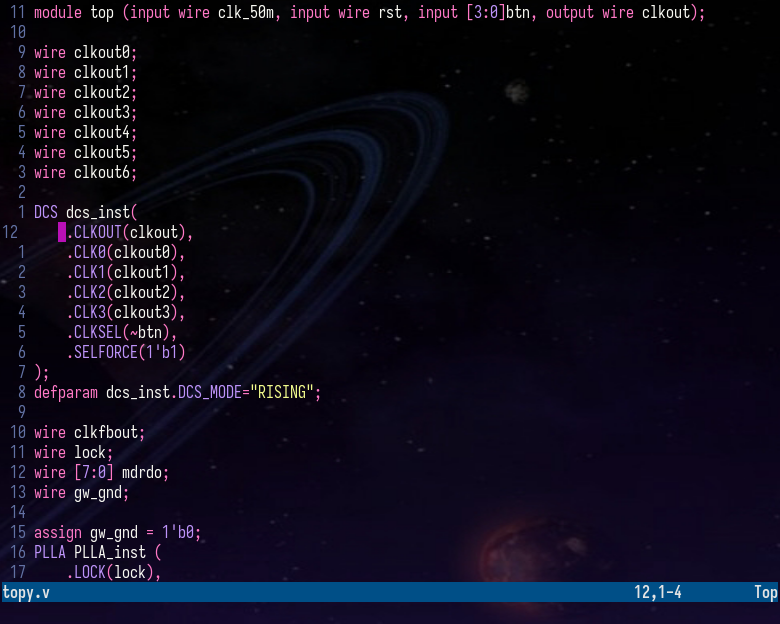

A test example of dynamic clock selection on the GW5A series #fpga, which goes through #Yosys* #nextpnr and #apicula * Strictly speaking, it does not go through Yosys because #gowin renamed the CLKx inputs to CLKINx for this primitive, but I temporarily changed their names.

News about GW5 series - PLL went through #yosys, #nextpnr, and #apicula and started working!🍾 At the moment, there are a huge number of crutches, which I plan to remove in the near future and make the appropriate PR.😉 #fpga#gowin#sipeed

Well, to the authors of #openFPGALoader😂, I can only add the ability to program this board in #Yosys #nextpnr and #apicula.😉 I don't think it will take much time, I just need it to appear on Asian marketplaces so I can buy it.😆

Design Quality: Power, Performance, Area (PPA) CVDP assesses the quality of generated RTL using logic synthesis tools (e.g., #Yosys, #Xcelium). Metrics: Worst Negative Slack (timing), total cell area, and switching power. These metrics distinguish usable designs from toy…

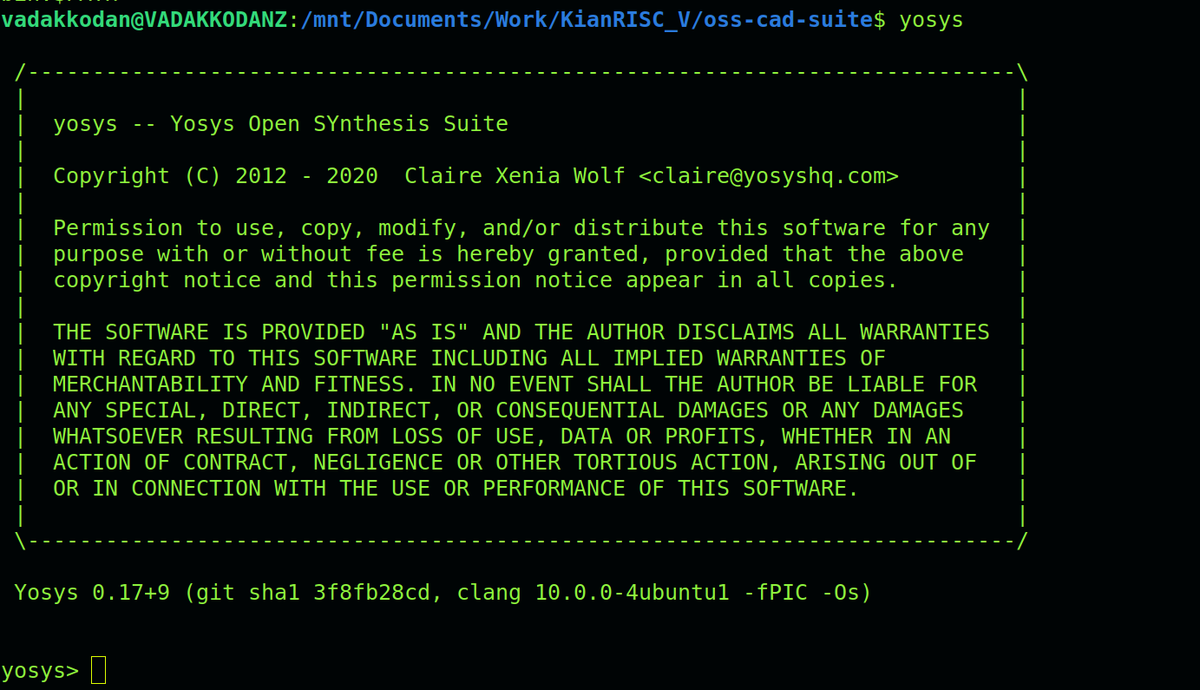

🛠️ Clifford Wolf — mastermind of Yosys, the open-source digital synthesis tool that brought FPGA design to the people. No NDAs. No million-dollar licenses. Just pure logic, unleashed. #FPGARevolution #Yosys #VerilogLiberation #OpenHardware

💡 Shoutout to Claire Wolf, creator of Yosys—the open-source synthesis tool that kicked down the FPGA gates. With her work, hackers, students, and startups can build silicon without signing NDAs. #Yosys #FPGA #OpenEDA #OSSRevolution

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

So, I grew up with #Yosys/nextpnr... you want awesome... here's the new 5-stage pipelined CPU, Kianv StealthV, in action... live synthesis, place & route. Two firmware switches and a transformation from hardcore SystemVerilog to Verilog. Pure awesomeness! @YosysHQ

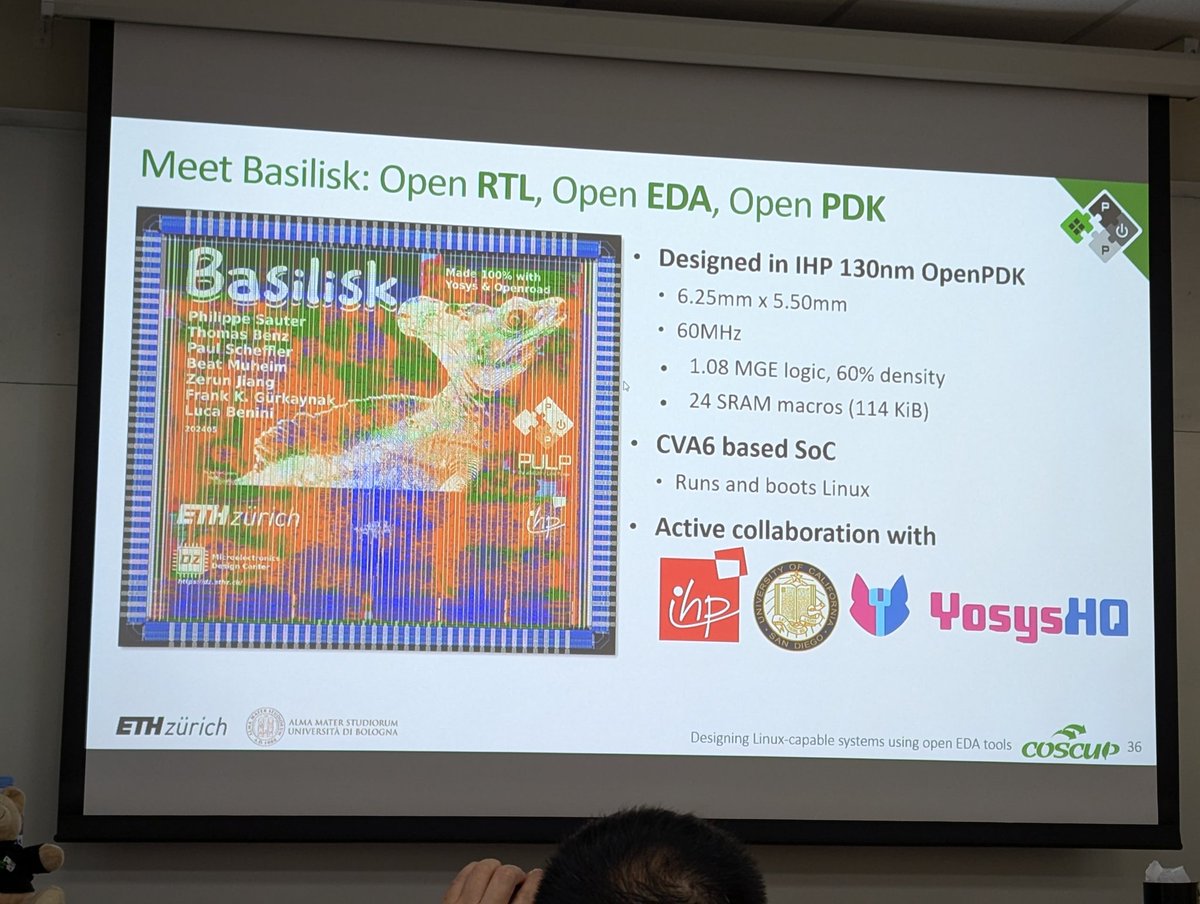

Now Philippe and Charlie from @pulp_platform talking about open tooling like #Yosys, #OpenLane , #Verilator and of course open #PDKs here at @coscup:) Happy to see @openhwgroup #CVA6 INSIDE #OpenHW #COSCUP #LINUX

It's crazy how picky one becomes with FPGAs. The toolchain is becoming more and more decisive for me. I prefer #Yosys/#nextpnr, ideally with #ECP5. It works without headaches. With Quartus, Gowin, or Vivado, or ... toolchains, I have a mental block; it doesn't feel good.

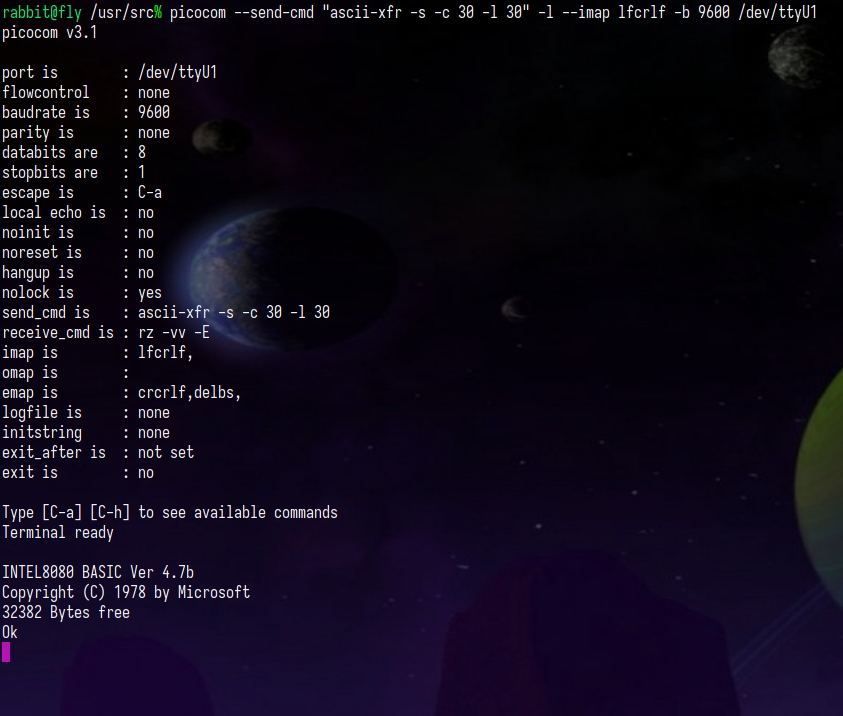

Gee! I discovered and corrected many funny features of BSRAM memory, and later this thing started working on #yosys #nextpnr #apicula! This is #Tangnano9k emulating a small system from the 80s with an i8080, 16K ROM, 32K RAM and a serial port.#fpga

Less than a week to go until out next #yosys user's group! 🙀 We'll be hosting a range of FPGA lightning talks & are thrilled to announce the following participants & their projects: ⭐️Pat Deegan's TT ASIC Simulator ⭐️Frans Skarman's Using a raspberry pi camera with an FPGA

Wanna participate in our next #yosys user group lightning talks about your #FPGA project using the open source tools? We'd love to hear from you! Just fill out the linked form. 😼 docs.google.com/forms/d/1gKbUf…

Curiously, even the simplest approach makes a pretty good hardware decoder (tools like #Yosys just do great work at optimisation) for 1.6bit (5 trits per byte) github.com/rejunity/tiny-…

I unpack 1 byte into 5 ternary. My unpacking approach is embarrassingly simple, but fits in a rather small logic circuit (#Yosys does great job here!) Each ternary is 2 bit lines: 1) 2's complement 8bit input 2) add/no-op. Accumulators are 17bit.

Join us tomorrow for the next #yosys user group! Sign up the newsletter for a reminder before we start: yosyshq.com/newsletter

This months’ #yosys user’s group will focus on hardware security! Katharina @K_CeesaySeitz & Flavian @FlavienSolt from ETH Zurich will introduce their tool for Information Flow Tracking (1/2)

This months’ #yosys user’s group will focus on hardware security! Katharina @K_CeesaySeitz & Flavian @FlavienSolt from ETH Zurich will introduce their tool for Information Flow Tracking (1/2)

Just got ICE40 UltraPlus $8 board from Texas. gnarlygrey.com/development-pl… Time to make #Yosys #IceStorm support for it.

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

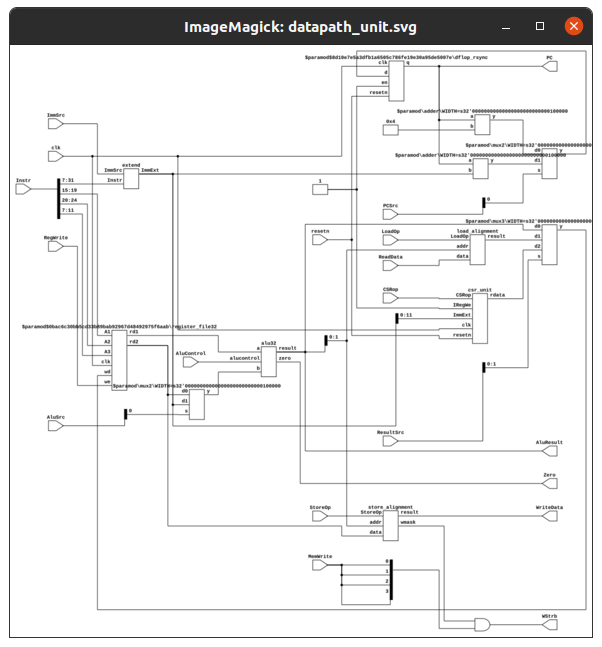

the beauty of datapath unit! Make from verilog rtl schematic via #yosys #netlistsvg. God bless that tools...fuckn fast and helpfull! Check all pathes are visually correct!

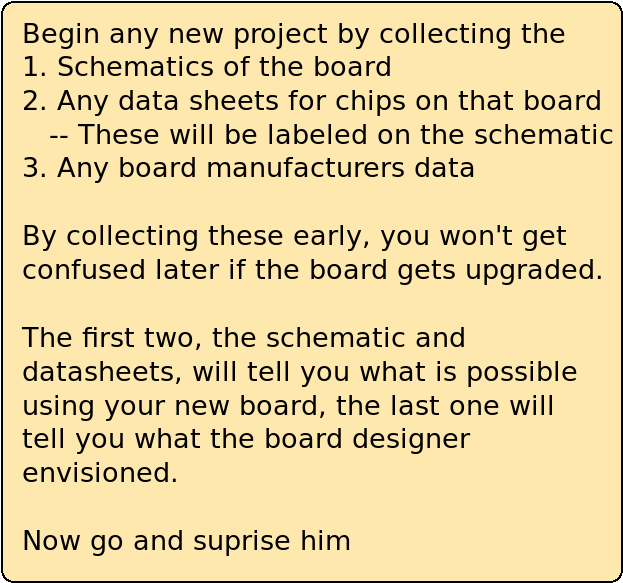

The first steps in any project, as discussed last night on #yosys -- freenode.irclog.whitequark.org/yosys/2019-01-…

Gee! ADC went through #yosys and #nextpnr! Does it work on hardware? Absolutely not!🤣 #apicula#fpga#gowin#sipeed

Finally, the Nexys Video board arrived for doing HW with Artix-7 fpga using Opensource EDA tools #Yosys #Symbiflow FuseSoC and learning languages such as #Chisel and #Amaranth hdl.

That's it, a full open source FPGA stack from @YosysHQ generating SERV, a @risc_v core by @OlofKindgren on a RISC-V host, the @SiFive Unmatched. Corescore was 100% built and programmed into @RadionaOrg ULX3S FPGA in RISC-V! Open source to the core! #RISCV #FPGA #Yosys #opensource

life is too short for #vivado just use #yosys #nextpnr to have hobby life balance... ~1.40 minutes for a bitstream instead of 20min or more

Gee! #yosys -> #nextpnr ->#gowin-pack successfully build and code a PLL primitive for #gowin #tangnano. The on-board quartz is 24MHz, the PLL generates ~72MHz Truly a great day! 😀 #apicula #fpga

Added one more mapper and expanded to the total 512Kb of sram on the @Olimex iCE40 fpga board. All with open source tools #icestorm #yosys #nextpnr

It has just come to my attention that the vendor IDE has a VGA example as part of it. So I just took it and compiled #yosys->#nextpnr->#apicula And marvel: no difference! The example uses PLL and it's the same source code! (almost) #fpga

Introducing github.com/antonblanchard… - a generator of fast and efficient standard cell adders, multipliers and multiply-adders. Written in Amaranth HDL, formally verified with #Yosys. #Verilator verification too With @OpenROAD_EDA + ASAP7 7nm a 32bit 3 cycle multiplier hits 2.7GHz

New #FPGA video, just in time for the New Year 🎉 In it, I show how to use block RAM built into the chip. Check it out here: youtu.be/CJVMFjonx_s #yosys #electronics #ice40

Something went wrong.

Something went wrong.

United States Trends

- 1. GeForce Season 4,030 posts

- 2. Comey 186K posts

- 3. Everton 145K posts

- 4. St. John 8,564 posts

- 5. Mark Kelly 123K posts

- 6. Amorim 61.6K posts

- 7. Manchester United 84.1K posts

- 8. #sjubb N/A

- 9. Iowa State 3,501 posts

- 10. UCMJ 18.2K posts

- 11. Seton Hall 2,361 posts

- 12. Opus 4.5 9,201 posts

- 13. #LightningStrikes N/A

- 14. Pickford 11.3K posts

- 15. 49ers 19.5K posts

- 16. Genesis Mission 2,166 posts

- 17. Benedict Arnold 3,907 posts

- 18. Dealing 30.5K posts

- 19. Hegseth 48.4K posts

- 20. Lipsey N/A