YosysHQ

@YosysHQ

Sign up to our newsletter! https://www.yosyshq.com/newsletter

你可能會喜歡

Have you seen how fast I synthesize? Just generating new PLLs and right away thanks to @YosysHQ and NextPNR for ECP5. This rocks! Simply awesome! FAST prototyping!

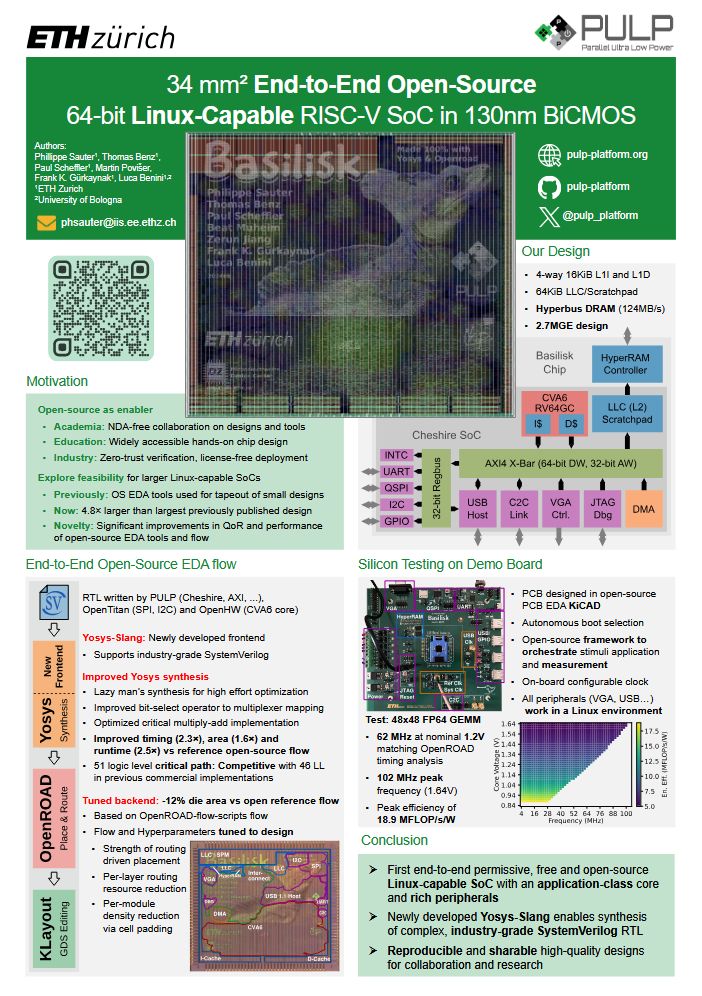

Super happy and honored for this award! @hotchipsorg is the top event for digital designers, and THE venue to show that open source HW and EDA are coming of age: We got working silicon to prove it! 🙏 to @pulp_platform's team, big 🙏 to @YosysHQ and @OpenROAD_EDA for support!

Great news from #HOTCHIPS2025! Philippe just won The Best Poster award for "34 mm² End-to-End Open-Source 64-bit Linux-Capable RISC-V SoC in 130nm BiCMOS". Find his poster here: pulp-platform.org/docs/hotchips2…

In our latest guest blog post, Matt Young introduces an Automated Triple Modular Redundancy EDA Flow for Yosys! blog.yosyshq.com/p/tamara-towar…

We’re close to making key decisions about future shuttles—and we want your input! 💬 What features matter most? What’s your price ceiling? Take our 2-min survey 👉 forms.gle/EMrSJQ6dmw4PNc… 🎁 One respondent will win a beautiful 150mm silicon wafer!

Good news open-source #FPGA fans, there's a new release of nextpnr (place and route) from @YosysHQ. The release notes mention "Numerous improvements to Gowin support": github.com/YosysHQ/nextpn…

I swear, I adjusted the Makefile for #Apicula in 5 minutes, and my uLinux SoC ran immediately with the toolchain for Gowin, in this case for my Tang Nano 20K. Big thanks to @YLRabbit, @pepijndevos, and @YosysHQ nice, awesome, it rules!

I can't believe I dared to do it: an iCE40HX8K FPGA that boots a mainline 6.13.0-rc1 #Linux kernel via OpenSBI, running 100% KianV SV32 (MMU) RV32IMA Zicntr Zicsr Zifencei SSTC RISC-V. Incredible... amazing board, thanks to @machdyne's Kuchen iCE40HX8K FPGA board. #ice40 @risc_v…

Our @YosysHQ friends released a new yosys-slang plugin! The plugin improves SystemVerilog support in open-source synthesis tooling, can process a number of open-source cores (PULP, Black Parrot, OpenTitan), provides a simpler flow w.r. existing solutions github.com/povik/yosys-sl…

We (and I cannot stress this enough) are so back. Jumperless V5 lets you prototype like a nerdy wizard that can see electricity and conjure jumpers wherever you want. And the wait is nearly over for this particular superpower, it launches September 23rd on @crowd_supply.

We're hiring! We're looking for a project manager to support our distributed team delivering technical projects. yosyshq.com/jobs

announcing... the waterloo hacker fab 📀 four months ago, a group of friends & i set out to build a diy chip fab @uwaterloo! so far, we've built a lithography machine, achieved micron-scale patterning, and have secured ~$16k to build the rest of the fab. more details below!

In my recent keynote at the free silicon conference I spoke about The long tail of semiconductors - Education, Tools and Artisanal ASICs. I'd love to know your thoughts, watch the video and comment or ask a question! youtube.com/watch?v=O6-3Df…

youtube.com

YouTube

The long tail of semiconductors - Education, Tools and Artisanal ASICs

@YosysHQ Thank you for stickers! It took me some time to place one to @RadionaOrg

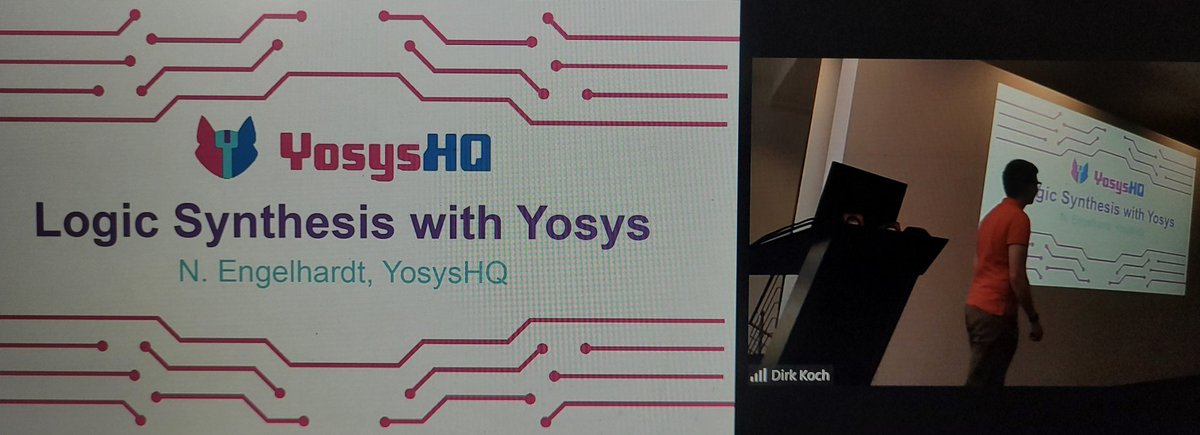

Logic Synthesis w/Nina Engelhardt & YosysHQ! Bringing your hardware description from a high level of abstraction to a gate level netlist that's optimizable looks so simple and modularized with Yosys' interactive tweaks! Fizz front-end to back-end transitions with ABC 'n nextpnr!

Today I visited @CCCAC. 🚂 First time trying an #FPGA with the @1bitsquared #OrangeCrab board, #UX is superb with @YosysHQ and #Amaranth. PRs filed for supporting the 85F variant 👩💻 Blinky was up and running in no time. 👍 Huge thanks to everyone developing the awesome tools! 🧡

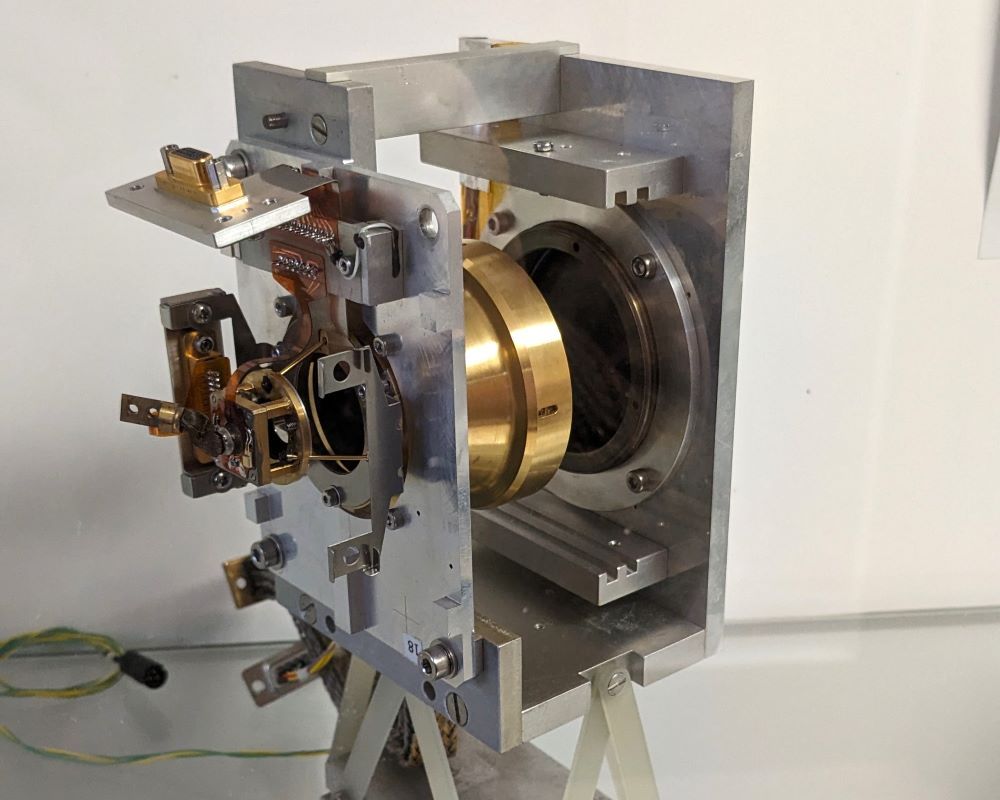

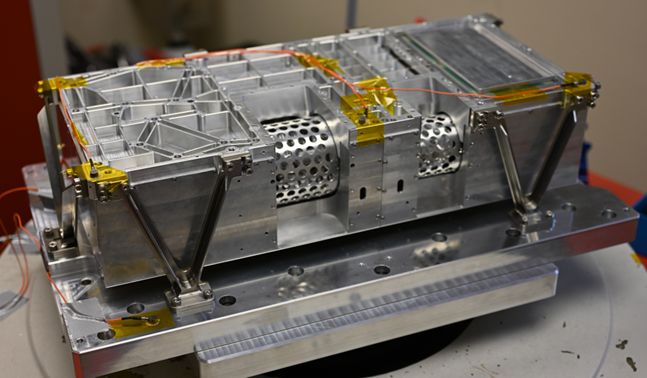

Our latest blog post is by Liam McSherry on how his group is using our formal verification tools for testing a very interesting satellite sensor. 🚀 blog.yosyshq.com/p/community-sp…

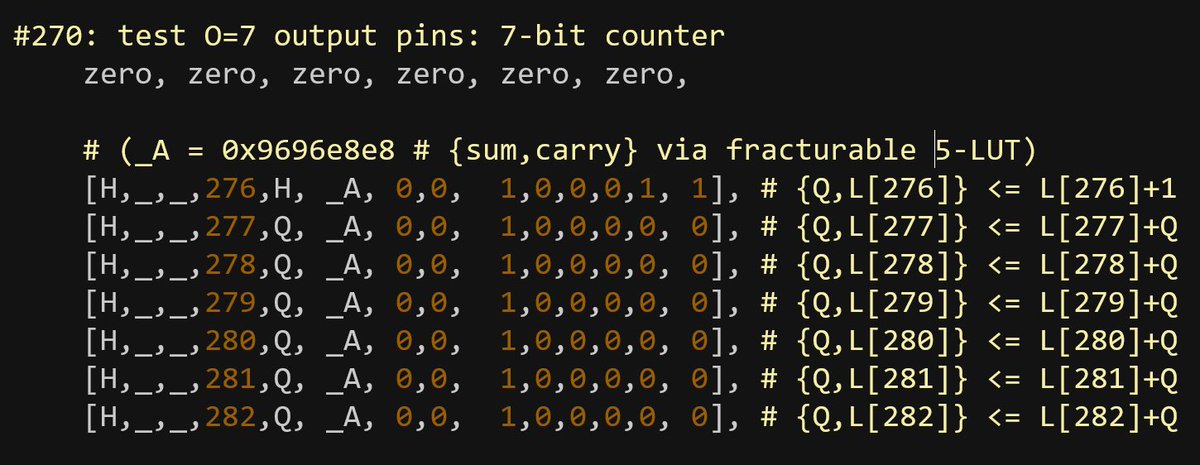

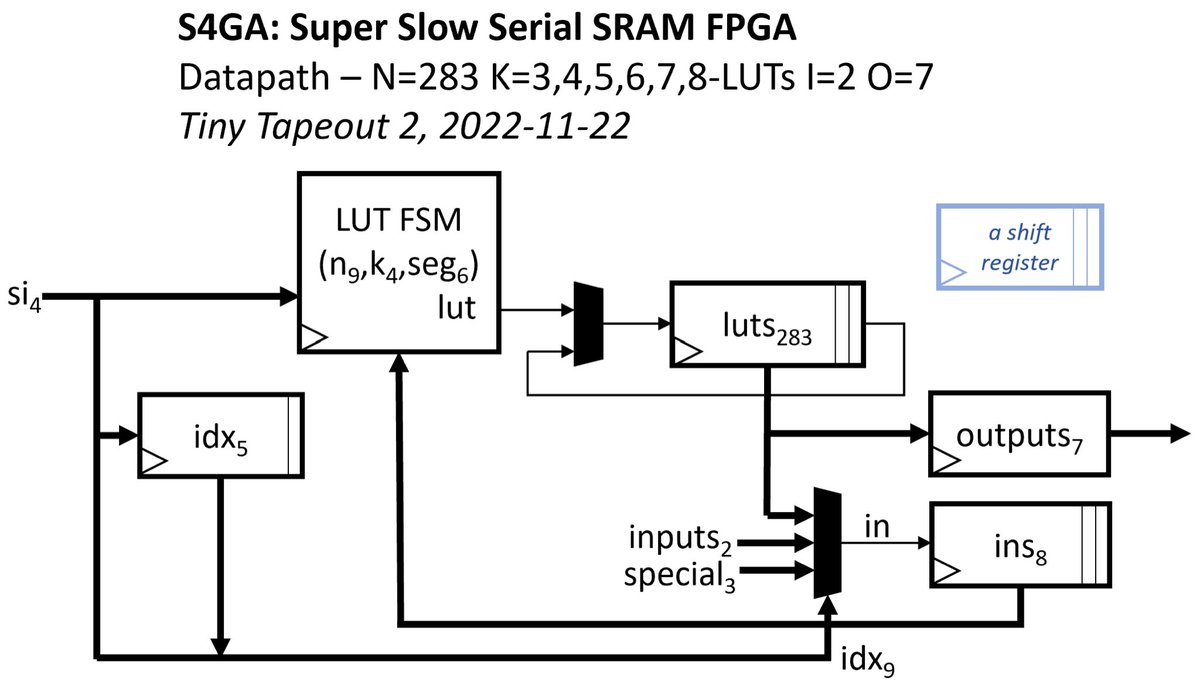

#FPGA tt02-s4ga works. I have streamed several netlists’ bitstreams into the design and so far all is well. A 283 5-LUT, 376 milliHertz FPGA datapath (2.5 kHz SoC clk) in ~150x170um of Skywater 130nm. github.com/grayresearch/t… Thanks again @tinytapeout @efabless @YosysHQ OpenROAD…

United States 趨勢

- 1. zendaya 5,922 posts

- 2. trisha paytas 2,100 posts

- 3. Apple TV 10.5K posts

- 4. No Kings 227K posts

- 5. #FursuitFriday 14.4K posts

- 6. #FanCashDropPromotion 1,519 posts

- 7. #FridayVibes 8,130 posts

- 8. #เพียงเธอตอนจบ 2.2M posts

- 9. #Yunho 29.1K posts

- 10. LINGORM ONLY YOU FINAL EP 2.14M posts

- 11. GAME DAY 32.1K posts

- 12. Arc Raiders 5,306 posts

- 13. Trevon Diggs N/A

- 14. Mamdani 293K posts

- 15. Eli Roth N/A

- 16. Cuomo 128K posts

- 17. My President 57.6K posts

- 18. Ramesh 4,485 posts

- 19. Karoline Leavitt 45K posts

- 20. $RANI 5,915 posts

你可能會喜歡

-

Matthew Venn

Matthew Venn

@matthewvenn -

OpenHW Foundation

OpenHW Foundation

@OpenHWFdn -

RISC-V International

RISC-V International

@risc_v -

Enjoy Digital

Enjoy Digital

@enjoy_digital -

Flux

Flux

@WillFlux -

Zip CPU

Zip CPU

@zipcpu -

lowRISC

lowRISC

@lowRISC -

CHIPSAlliance

CHIPSAlliance

@CHIPSAlliance -

Tim 'mithro' Ansell

Tim 'mithro' Ansell

@mithro -

Antmicro

Antmicro

@antmicro -

Luke Wren @[email protected]

Luke Wren @[email protected]

@wren6991 -

logic destroyer

logic destroyer

@splinedrive -

Marcelo Samsoniuk

Marcelo Samsoniuk

@samsoniuk -

Tom Verbeure

Tom Verbeure

@tom_verbeure -

PULP Platform

PULP Platform

@pulp_platform

Something went wrong.

Something went wrong.