#fpga 搜尋結果

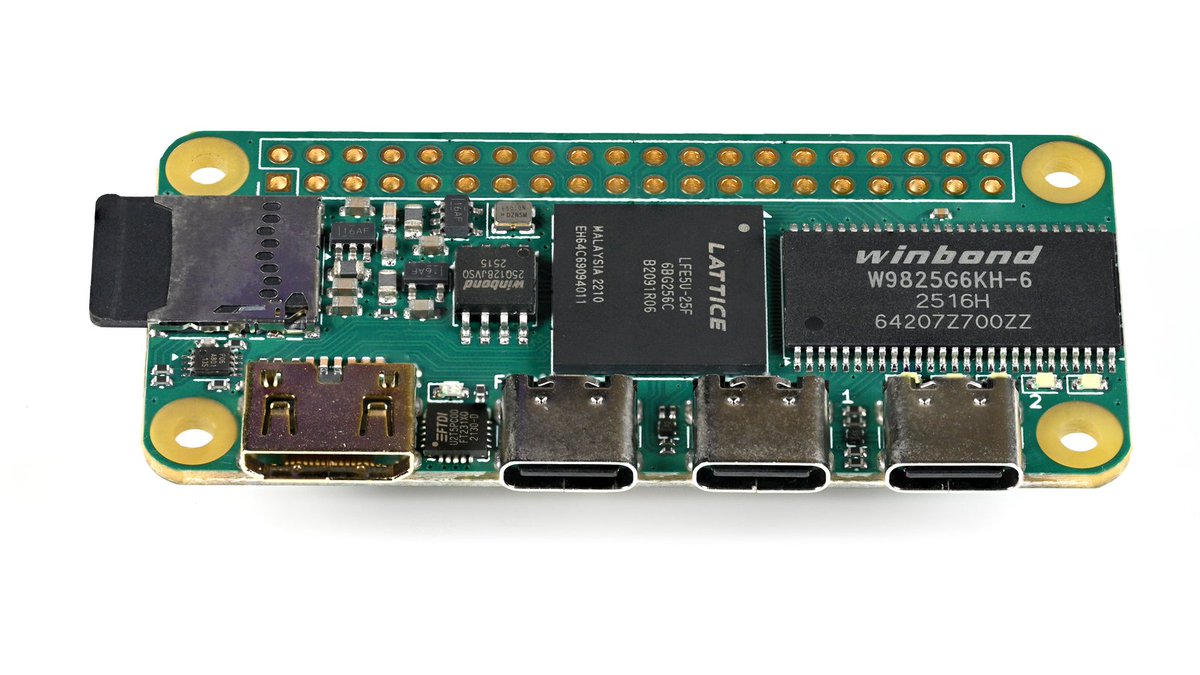

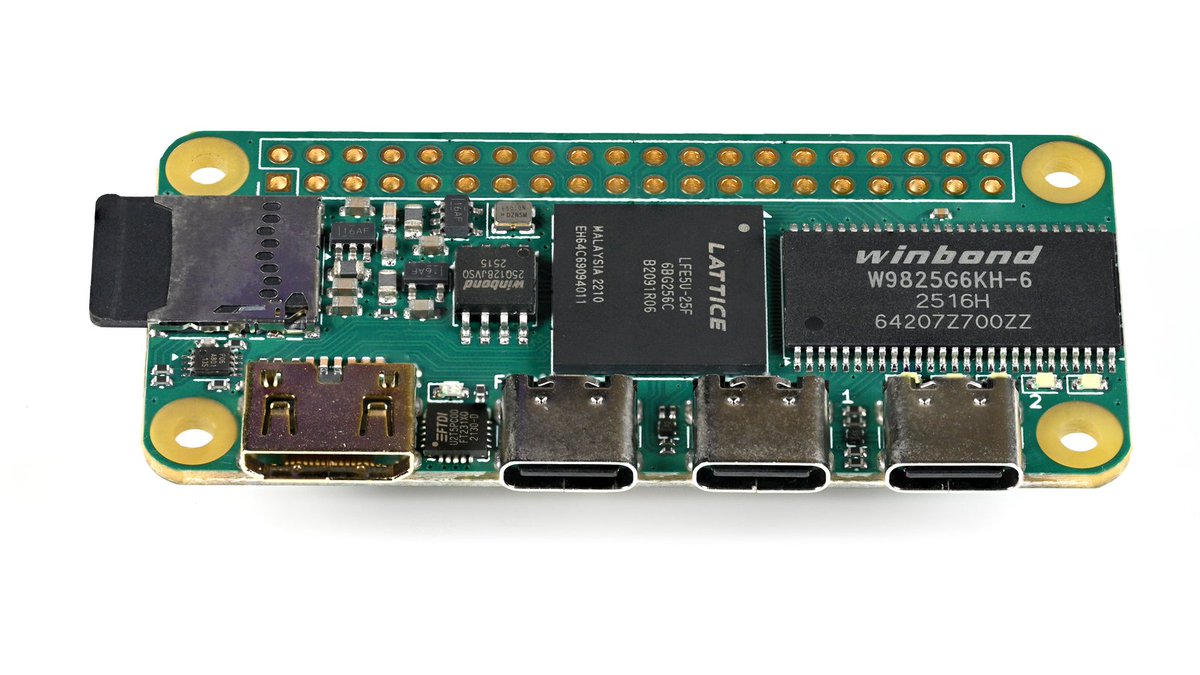

Icepi Zero looks like an interesting open-source ECP5 #FPGA dev board. It’s got a decent spec in a small form factor. The only obvious omission is audio out. The big question is, how much will it cost? crowdsupply.com/icy-electronic…

Do you remember your first serious PCB design? Mine is this #Zynq 7010 4-layer board without DDR. The moment of #FPGA JTAG detection will be forever remembered, together with the rusty table, still air, and glorious, responsibility-free days.

Gee! 🤣 The GW5 series has very fun PLLs—each can generate 7 different freqs at the outputs. The question: why do you need as many as 6 suchPLLs? :) Well, anyway, #apicula can generate all 7 outputs and distribute them across the clock spines as long as it can :) #fpga#gowin

#FPGA Showdown Here's mine! Also just a part of them, maybe one third. Digilent boards are the prettiest in my collection.

After a whole day talking about #FPGA, it's time for a relaxing evening playing with this new tiny FPGA board based on an @efinixinc Trion FPGA.

First light! 🔥 ao486 boots DOS on the #TangConsole 138K. HDD, VGA, BIOS, and VGA BIOS are all up and running — watching it hit the DOS prompt on real hardware is surreal. #FPGA #RetroComputing 🎥👇

Seeking ideas for a new #Tang #FPGA board! What would you use a $49 FPGA board with 35K LUTs and 512Mbit DDR4 and MIPI DSI/CSI for? Let us know your project ideas!

👏 We had a great time at AutoSens Europe and @FPGAHorizons! Lattice, @LIPS_Corp, and @econSystems demoed EMS, DMS, and OMS for next-gen automotive, and we led edge AI talks to spotlight low power #FPGA innovation. 👇 Learn more.

Dropped the Bitcoin miner, got handed a Zama FPGA - total upgrade! Big love to @zama_fhe for making homomorphic encryption cool AND practical. Respect for the real innovation!🙌 #FHE #Privacy #FPGA #ZamaCreatorProgram #ZamaFHE #Crypto #Zama #Web3 #DeFiSecurity #DeFi #Blockchain

Extend the Military Rugged Real-Time Spectrum Analyzer "V6 MIL V2"😀 Full access to the 2x32TB SSD & additional 4 M.2 slots to add Wi-Fi, #5G, #LoRa, #FPGA boards etc. More to come soon! #Aaronia #RF #Tech #Laptop #Spectrumanalyzer #SDR #SigInt #AMD #WiFi

Bientôt la fin du développement de l'émulateur de CD-rom2. Confirmation que le port USB fonctionne bien et que les jeux peuvent être lancés depuis les CDs. #PCENGINE #FPGA #RETROGAMING

News about GW5 series - PLL went through #yosys, #nextpnr, and #apicula and started working!🍾 At the moment, there are a huge number of crutches, which I plan to remove in the near future and make the appropriate PR.😉 #fpga#gowin#sipeed

A 100-byte monitor that understands three commands via the serial port: write and read a byte, and call a subroutine at an address. Works with Tangnano9k, Tangnano20k, TangPrimer25k. #fpga#apicula#forth#gowin

هواپیمایم در #امهرست که نشست ایمیلی دریافت کردم که برای داوری یک تز دکترا در دانشگاه نیوسات ولز #استرالیا انتخاب شدم. تز جالبی بود و در زمینه تخصصی من قرار داشت. دانشجو از #FPGA برای موازی سازی یک الگوریتم حل جریان رقیق استفاده کرده بود و مدل برخوردی جالبی ارائه کرده بود. با…

Built a dual-clock async FIFO in pure Verilog: Gray-coded pointers, registered full/empty, clean CDC. Lint-clean and passes a self-checking testbench. Tiny, fast, rock-solid. #FPGA #Verilog #logicDestroyer

💡 Upgrading RF FPGAs? Altera’s Agilex™ 9 Direct RF devices offer a powerful option for medium-band applications with unmatched performance & flexibility. 👉 Read more: community.intel.com/t5/Blogs/Produ… #FPGA #Agilex9 #DirectRF #DesignInnovation

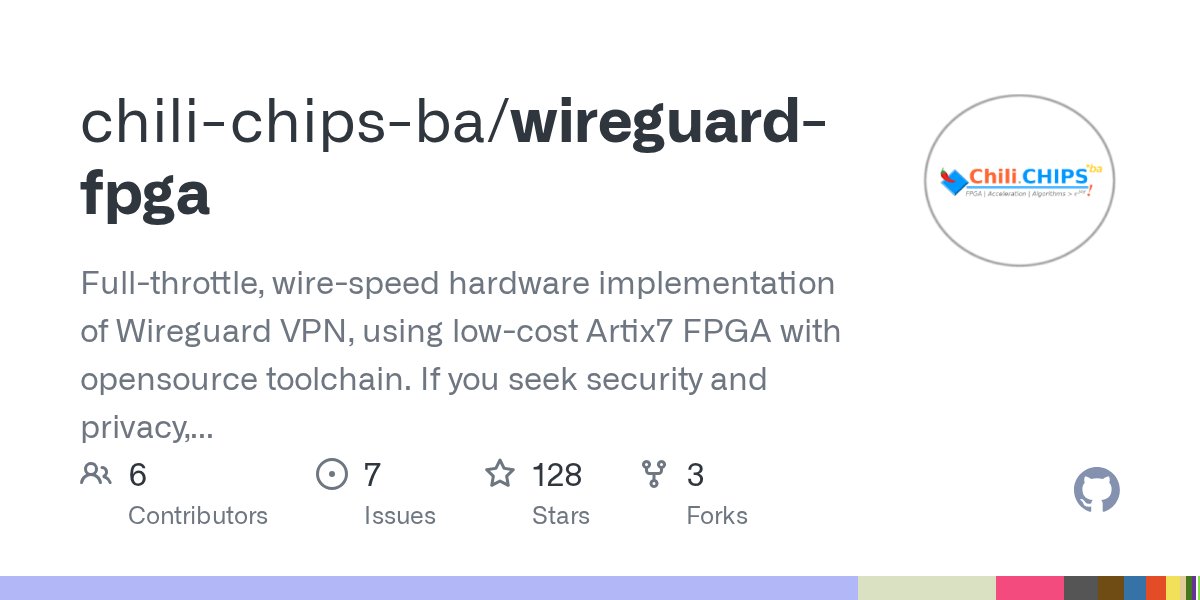

Is the future of secure networking in hardware? Wireguard FPGA shows how we can boost performance and security simultaneously, turning encryption into a dedicated process. How do you see hardware impacting network security? #Wireguard #FPGA

Новое видео на канале AMD: AMD Vivado™ Design Suite Tutorial Targeting AMD Spartan™ Ultrascale+™ FPGAs youtu.be/mnSd7qmYV9w #xilinx #vivado #fpga #плис #vitis

Dropped the Bitcoin miner, got handed a Zama FPGA - total upgrade! Big love to @zama_fhe for making homomorphic encryption cool AND practical. Respect for the real innovation!🙌 #FHE #Privacy #FPGA #ZamaCreatorProgram #ZamaFHE #Crypto #Zama #Web3 #DeFiSecurity #DeFi #Blockchain

"#Wireguard is..a modern, secure data tunneling and encryption method..easier to manage than the incumbents. The intent of this project is to bridge these gaps with an #FPGA open-source implementation of Wireguard, written in SystemVerilog HDL." github.com/chili-chips-ba…"

Last August I was at DEF CON 33 talking about the role of #FPGA in #Cybersecurity focusing on the advantages of using them as reconfigurable #HSM. Now this talk is live on YouTube. Check it out! youtube.com/watch?v=9slY1D…

youtube.com

YouTube

DEF CON 33 - Reconfigurable HSMs: Future Proofing Hardware Security -...

3/ 💡 Photonic FPGAs Logic in light, not electrons. Compute at light speed, zero heat. Ideal for wave-phase market models. Quantum-like parallelism, classical control. #Photonic #FPGA #Quantum

🧵 8️⃣ Hardware Arbitrage Exchange desyncs = profit. FPGA sees it before CPU wakes up. Signal → Order → Win. #Arbitrage #FPGA

🧵 6️⃣ Entropy = Edge Each tick adds entropy. FPGAs measure it live. High entropy = volatility = opportunity. #Quant #FPGA

🧵 2️⃣ Inside an HFT FPGA Network → Parser → Signal → Risk → Order. All inside one chip. No software stack. Pure parallel speed. #LowLatency #FPGA

👏 We had a great time at AutoSens Europe and @FPGAHorizons! Lattice, @LIPS_Corp, and @econSystems demoed EMS, DMS, and OMS for next-gen automotive, and we led edge AI talks to spotlight low power #FPGA innovation. 👇 Learn more.

Hands-on Workshop on “FPGA Prototyping using Verilog HDL” conducted for Final Year ECE students of Adi Shankara Institute of Engineering and Technology! An exciting session exploring FPGA design, Verilog coding, and real-time implementation 🔧⚙️ #FPGA #VerilogHDL #Electronics

@Microsoft open sources Kanagawa #HLS for #FPGA and #ASIC development, check it out... github.com/microsoft/kana…

What Is Excess Electronic Inventory and How to Turn It Into Profit icdrex.com/what-is-excess… #lattice #fpga #avant #semiconductor #chip #drex #drexelectronic

Reducing BER means improving reliability. Whether it’s FEC, modulation schemes, or SNR tweaks — every bit counts. #FPGA #DigitalComms

🎓 “Our partnership with the Altera University Program has been instrumental in advancing our students’ skills.” — Dr. Dunne, Imperial College London 💡 Hands-on FPGA experience. Real-world innovation. 👉 Learn more: altera.com/contact-us/ema… #FPGA #AlteraUniversity

#TMNT Turtles in Time recently got a public release on the #AnaloguePocket as an Open #FPGA Arcade Core. So I have been thinking of playing through it on stream. I just wish I had someone to play with. I'm a single player looking for my player 2 or 3 or 4 lol. #retrogamer

#FPGA Showdown Here's mine! Also just a part of them, maybe one third. Digilent boards are the prettiest in my collection.

Do you remember your first serious PCB design? Mine is this #Zynq 7010 4-layer board without DDR. The moment of #FPGA JTAG detection will be forever remembered, together with the rusty table, still air, and glorious, responsibility-free days.

Icepi Zero looks like an interesting open-source ECP5 #FPGA dev board. It’s got a decent spec in a small form factor. The only obvious omission is audio out. The big question is, how much will it cost? crowdsupply.com/icy-electronic…

Isle 🏝️ is my new #FPGA project. Isle is a simple, modern computer — an open design that encourages tinkering, experimentation, and doing your own thing. I hope to inspire you to come on a journey with me and build your own computer. projectf.io/isle/fpga-comp…

Gee! 🤣 The GW5 series has very fun PLLs—each can generate 7 different freqs at the outputs. The question: why do you need as many as 6 suchPLLs? :) Well, anyway, #apicula can generate all 7 outputs and distribute them across the clock spines as long as it can :) #fpga#gowin

After a whole day talking about #FPGA, it's time for a relaxing evening playing with this new tiny FPGA board based on an @efinixinc Trion FPGA.

GW5A series PLLs! Only two so far. Do they work? Hell no. Will they work? Of course.🤣 #fpga#apicula#gowin

Extend the Military Rugged Real-Time Spectrum Analyzer "V6 MIL V2"😀 Full access to the 2x32TB SSD & additional 4 M.2 slots to add Wi-Fi, #5G, #LoRa, #FPGA boards etc. More to come soon! #Aaronia #RF #Tech #Laptop #Spectrumanalyzer #SDR #SigInt #AMD #WiFi

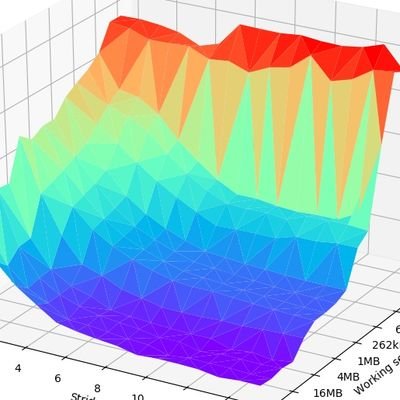

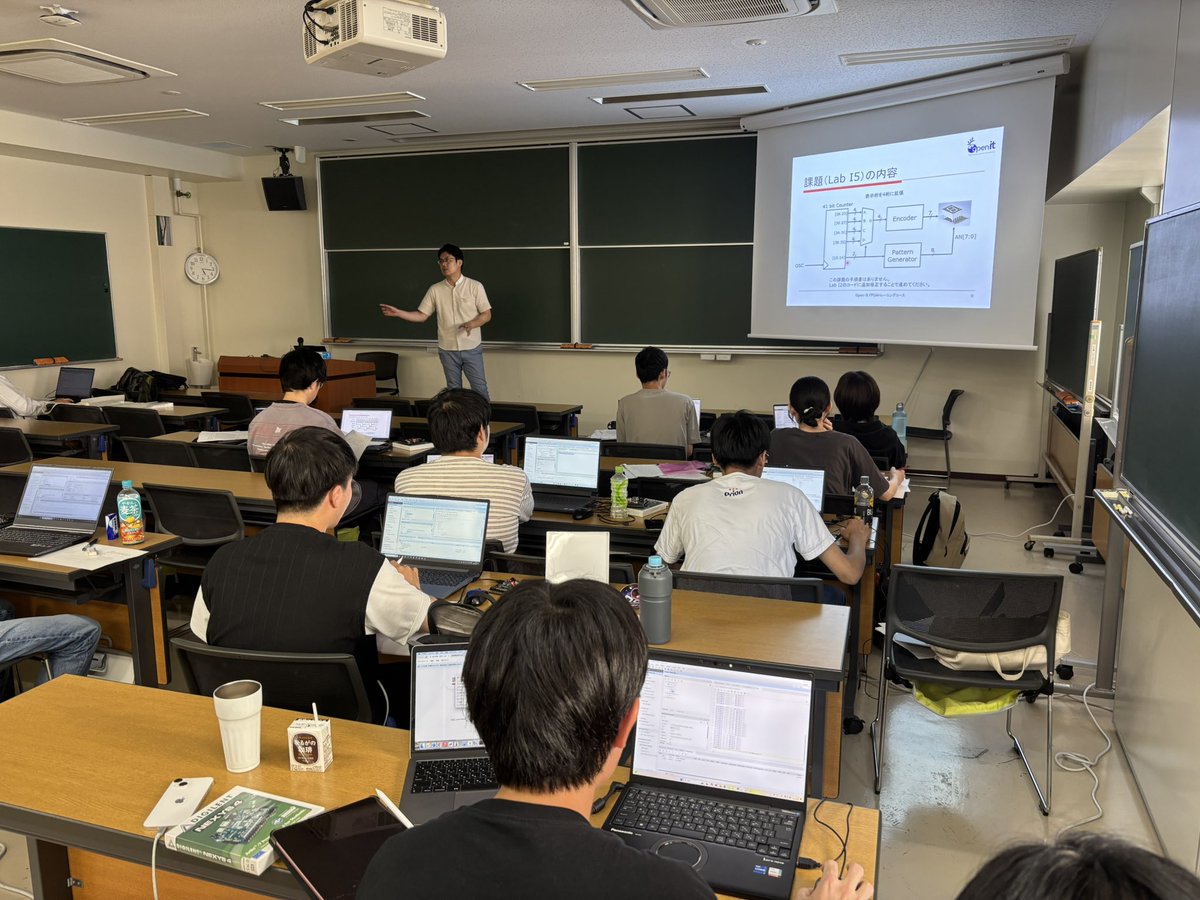

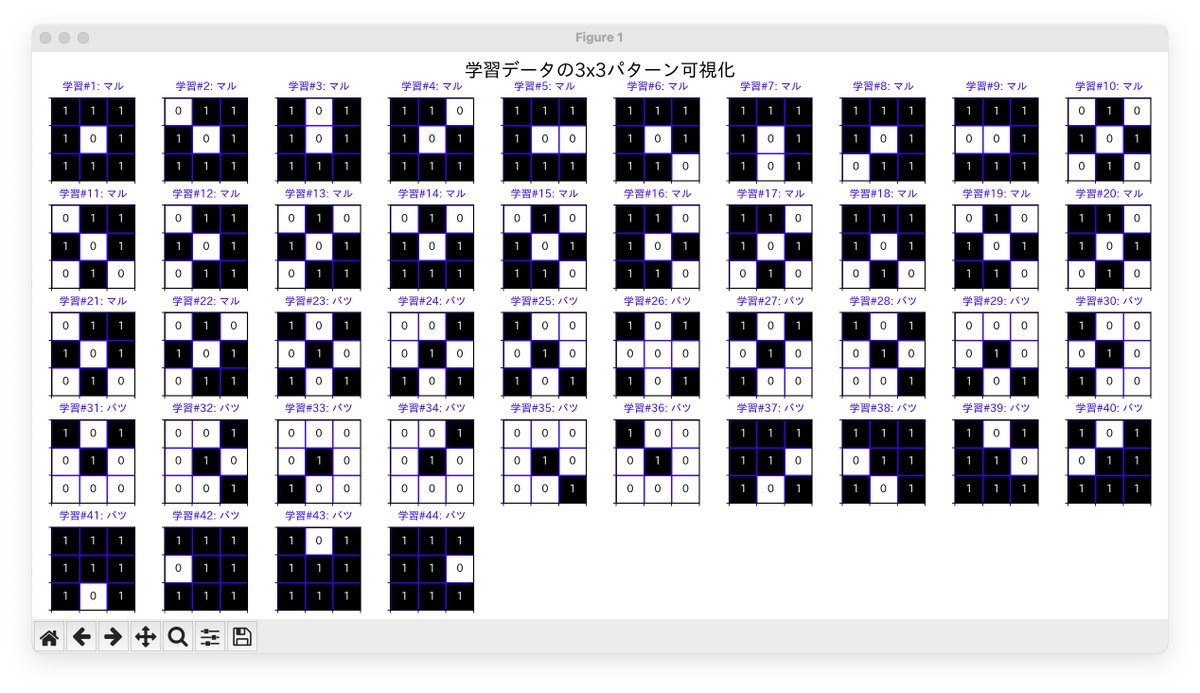

Tried running a custom neural net on FPGA with 3×3 images. Similar to a 2-layer NN, theoretically hitting 75M fps. Now building neurons that learn all weights in parallel—no backprop or gradients! 28×28(MNIST) might be tough tho 😅 #NeuralNetworks #FPGA #mnist

VGA to RGB Scart cable for the Analogizer by @RndMnkIII - double shielded 1.5m cable - 470ohm resistor on the sync line - stereo lead - 15khz only - pcb board on scart plug #mister #fpga #gaming #retro #RETROGAMING #games #RGB

Seeking ideas for a new #Tang #FPGA board! What would you use a $49 FPGA board with 35K LUTs and 512Mbit DDR4 and MIPI DSI/CSI for? Let us know your project ideas!

Spotted inside a BYD inverter control board: a GOWIN FPGA. (At 13:40) youtu.be/VukUHrX2b1U?si… A noteworthy example of how China’s EV ecosystem is increasingly supported by domestic semiconductor solutions. ⚡🚗 #EV #Semiconductors #FPGA #BYD #TechEcosystem #AutomotiveInnovation…

A team of 11 people built this. Want to be the 12th and build bigger? Apply now: careers.armory.in/jobs/Careers #hiring #fpga #rfhardware #digitalsignalprocessing

هواپیمایم در #امهرست که نشست ایمیلی دریافت کردم که برای داوری یک تز دکترا در دانشگاه نیوسات ولز #استرالیا انتخاب شدم. تز جالبی بود و در زمینه تخصصی من قرار داشت. دانشجو از #FPGA برای موازی سازی یک الگوریتم حل جریان رقیق استفاده کرده بود و مدل برخوردی جالبی ارائه کرده بود. با…

Here we are! If you are in the Embedded World Conference come to see me this afternoon at the #FPGA track!

Something went wrong.

Something went wrong.

United States Trends

- 1. #GalxeID 7,355 posts

- 2. Branch 38.4K posts

- 3. Red Cross 61.1K posts

- 4. #njkopw 14.1K posts

- 5. Chiefs 113K posts

- 6. Knesset 24K posts

- 7. All 20 47.5K posts

- 8. Use GiveRep N/A

- 9. Lions 90.1K posts

- 10. Rod Wave 1,795 posts

- 11. Air Force One 61.5K posts

- 12. Mahomes 35.3K posts

- 13. Eitan Mor 20.3K posts

- 14. #LaGranjaVIP 85.2K posts

- 15. #LoveCabin 1,425 posts

- 16. Ziv Berman 23.9K posts

- 17. Alon Ohel 21.3K posts

- 18. Tom Homan 83.6K posts

- 19. Matan Angrest 18.8K posts

- 20. #TNABoundForGlory 61.7K posts