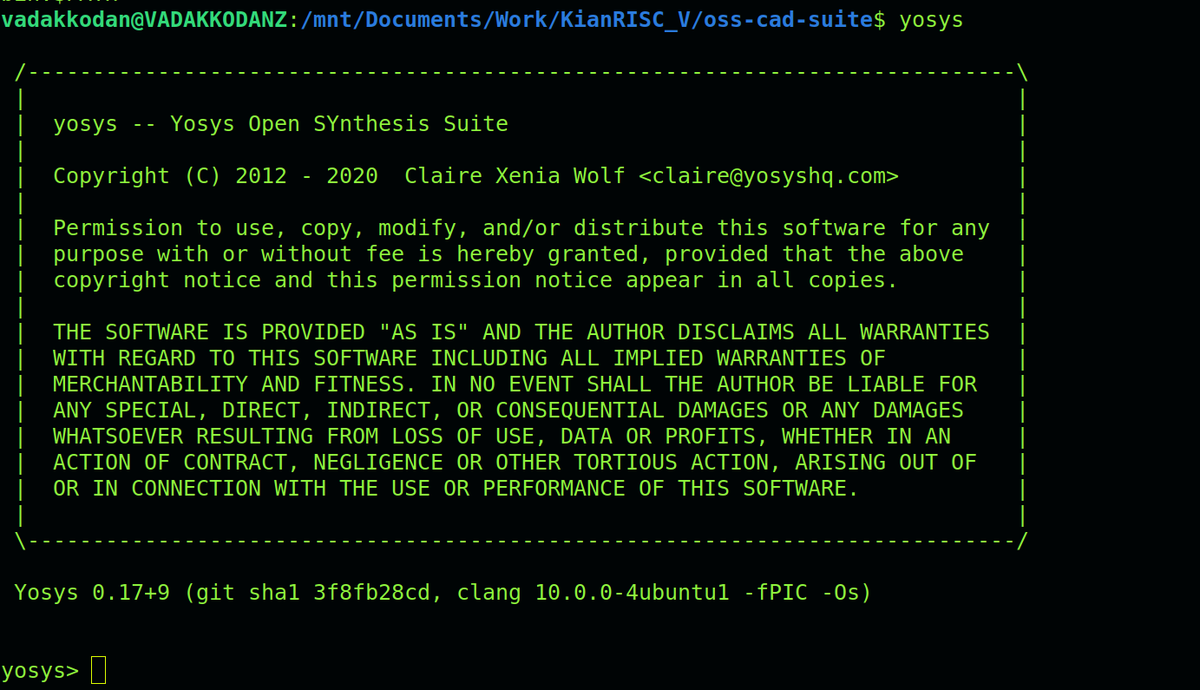

#yosys kết quả tìm kiếm

An update on my #flamegraph FPGA resource usage experiment. I wrote a #yosys plugin to generate a flamegraph for each cell type used in the design and combine it all in a single HTML page

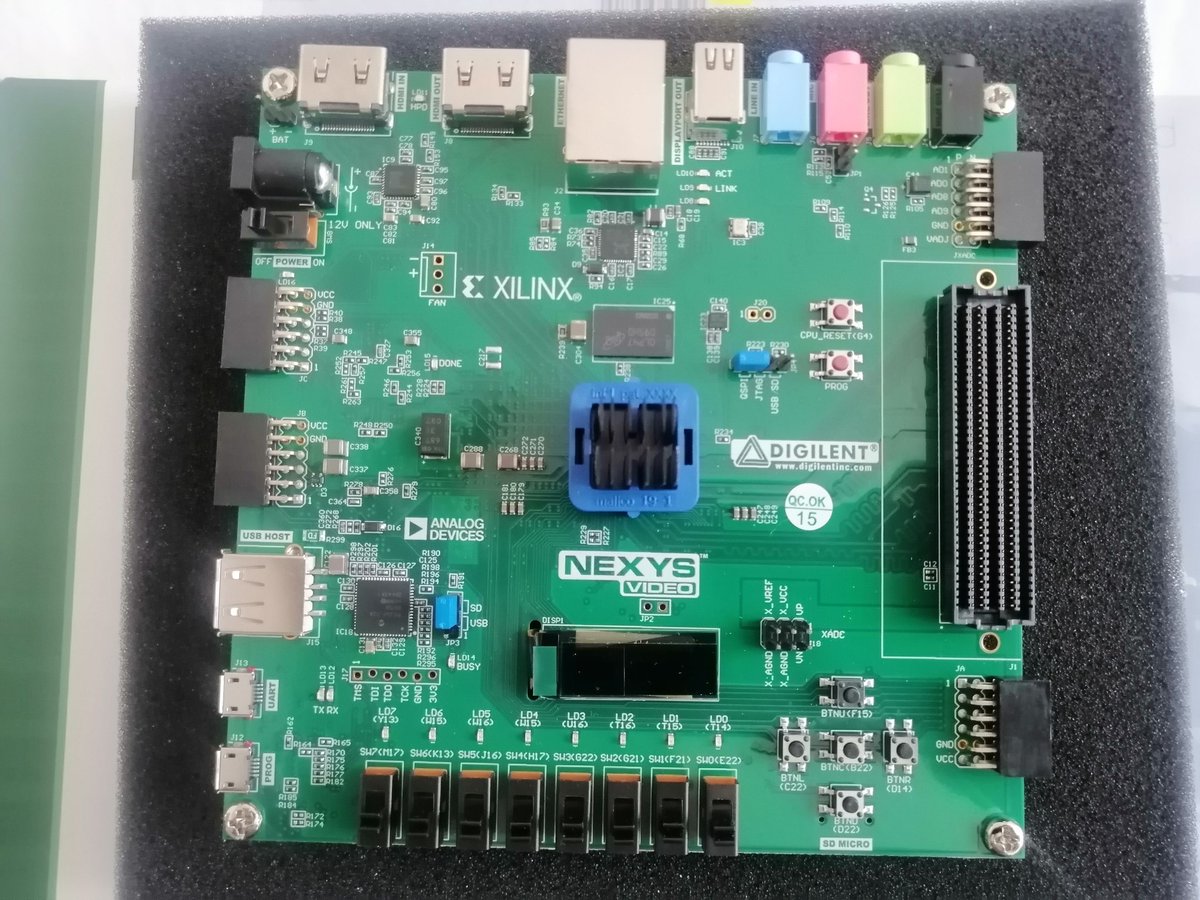

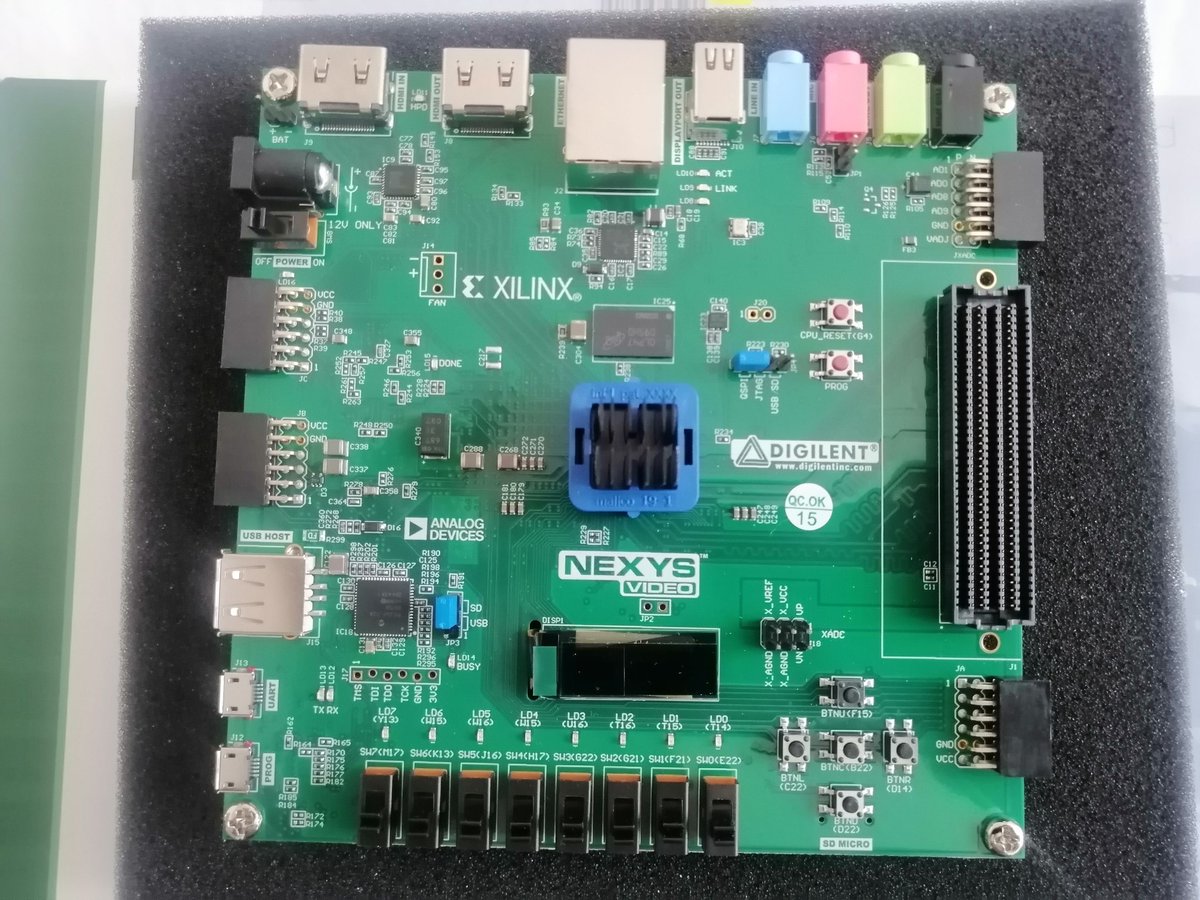

Finally, the Nexys Video board arrived for doing HW with Artix-7 fpga using Opensource EDA tools #Yosys #Symbiflow FuseSoC and learning languages such as #Chisel and #Amaranth hdl.

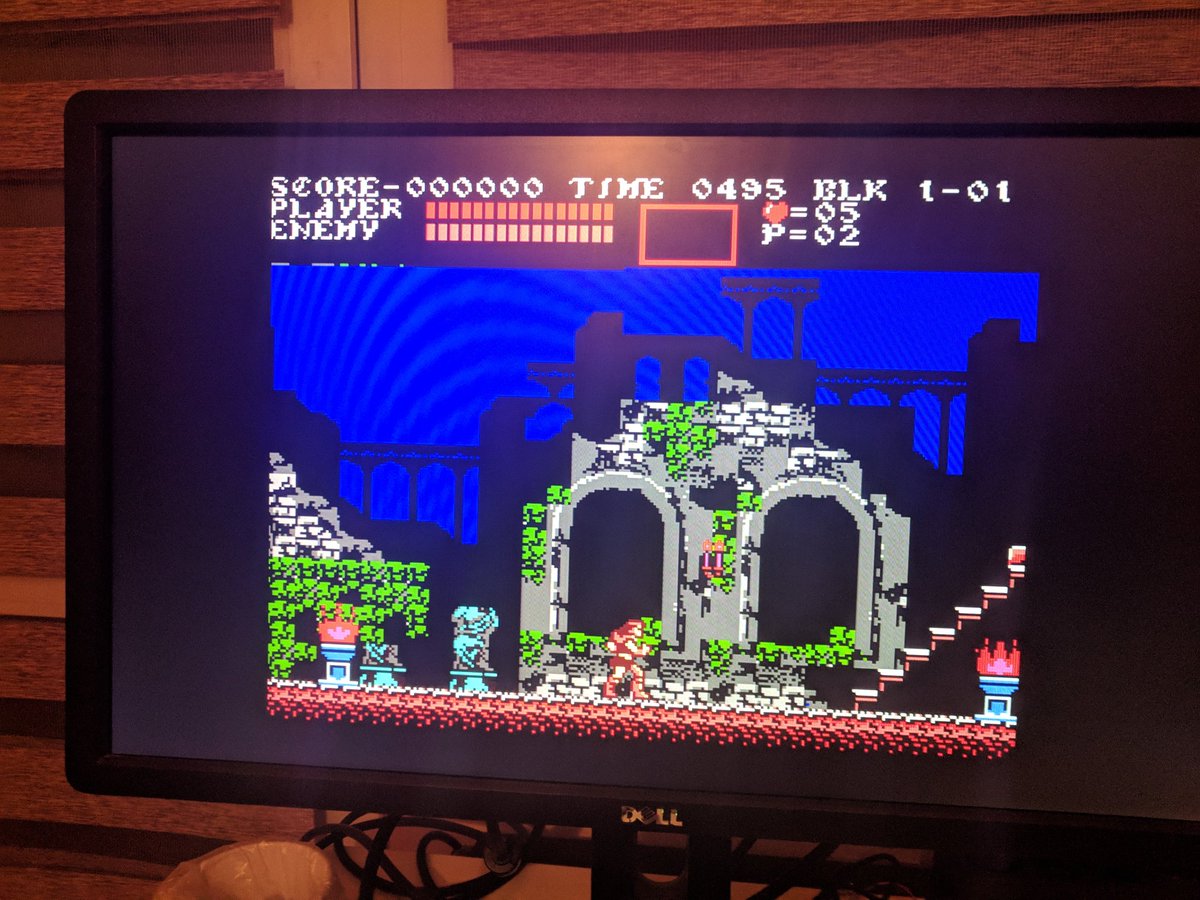

The new PnR architecture for gowin chips has flashing LEDs! The departure from the old Generic-based architecture was long overdue. Himbächel - a series of bigger arches github.com/YosysHQ/nextpn… #fpga #gowin #yosys

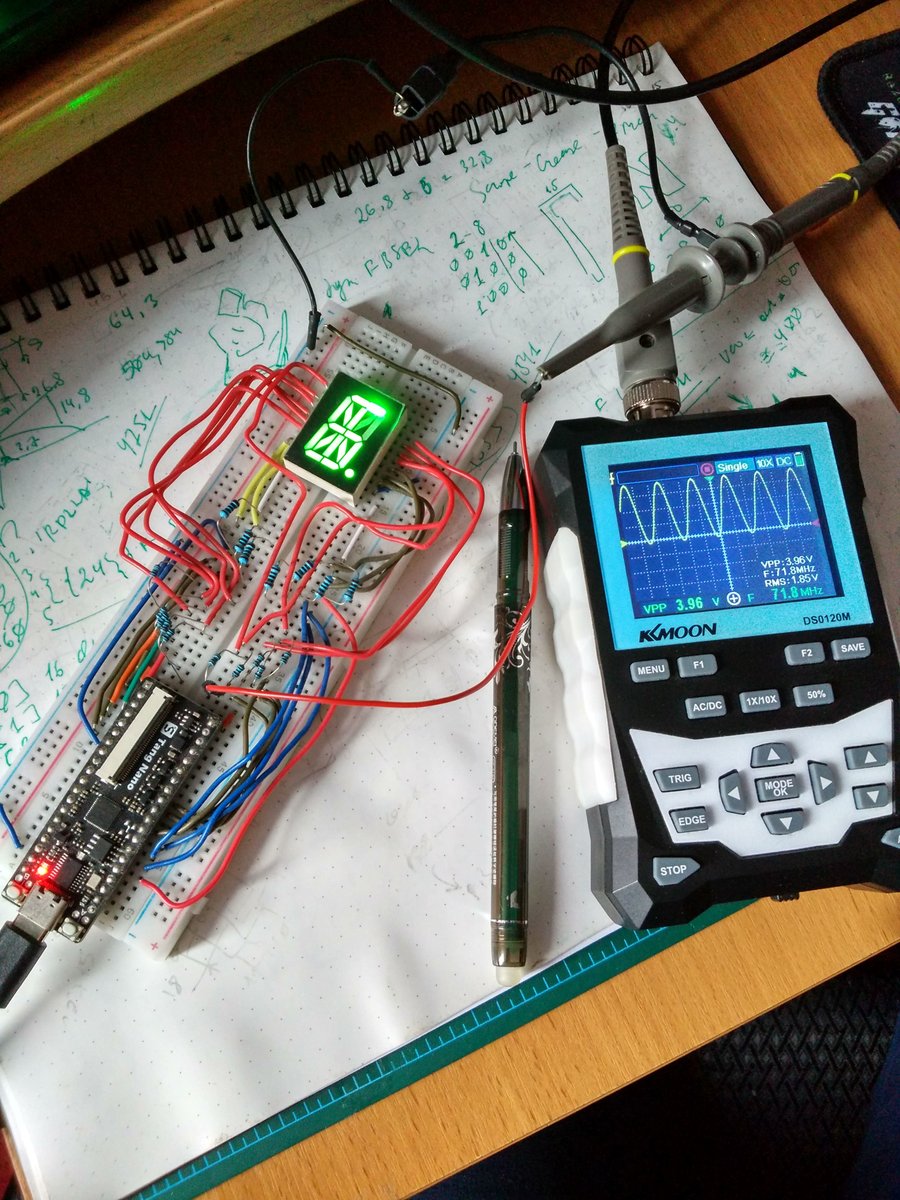

#femtorv32 running on the ULX3S, now at 60MHz. Using EHXPLLL. Can probably go faster. #yosys says "$glbnet$clk: 74.43 MHz max frequency". Anybody knows how to go faster ? (Started to read about clock distribution on the ECP5, but it seems complicated).

Simulating #fpga designs on a GPU made simple! I stumbled upon a gem in the Google CTF contest: reversing-gpurtl. This is from 2019, but I missed it somehow (1/13) TL;DR: Simulating a (simple) design #Verilog => #Yosys => #GPU (yes, for real). Let's take a closer look! 👇

Running the PicoSoC in the Nexys Video using #Symbiflow. I'm astonished how automated is this toolchain. #FPGA #Yosys #Artix7

That's it, a full open source FPGA stack from @YosysHQ generating SERV, a @risc_v core by @OlofKindgren on a RISC-V host, the @SiFive Unmatched. Corescore was 100% built and programmed into @RadionaOrg ULX3S FPGA in RISC-V! Open source to the core! #RISCV #FPGA #Yosys #opensource

#fpgafriday time for new #yosys #oss-cad-suite-build #iverilog #verilator #openfpgaloader #gtkwave.....github.com/YosysHQ/oss-ca… 💥💥💥💯💯❤️💯💥❤️❤️❤️❤️❤️❤️❤️💯💥💥💯💥💥💥💥❤️❤️💯❤️❤️💯❤️❤️💯❤️😕

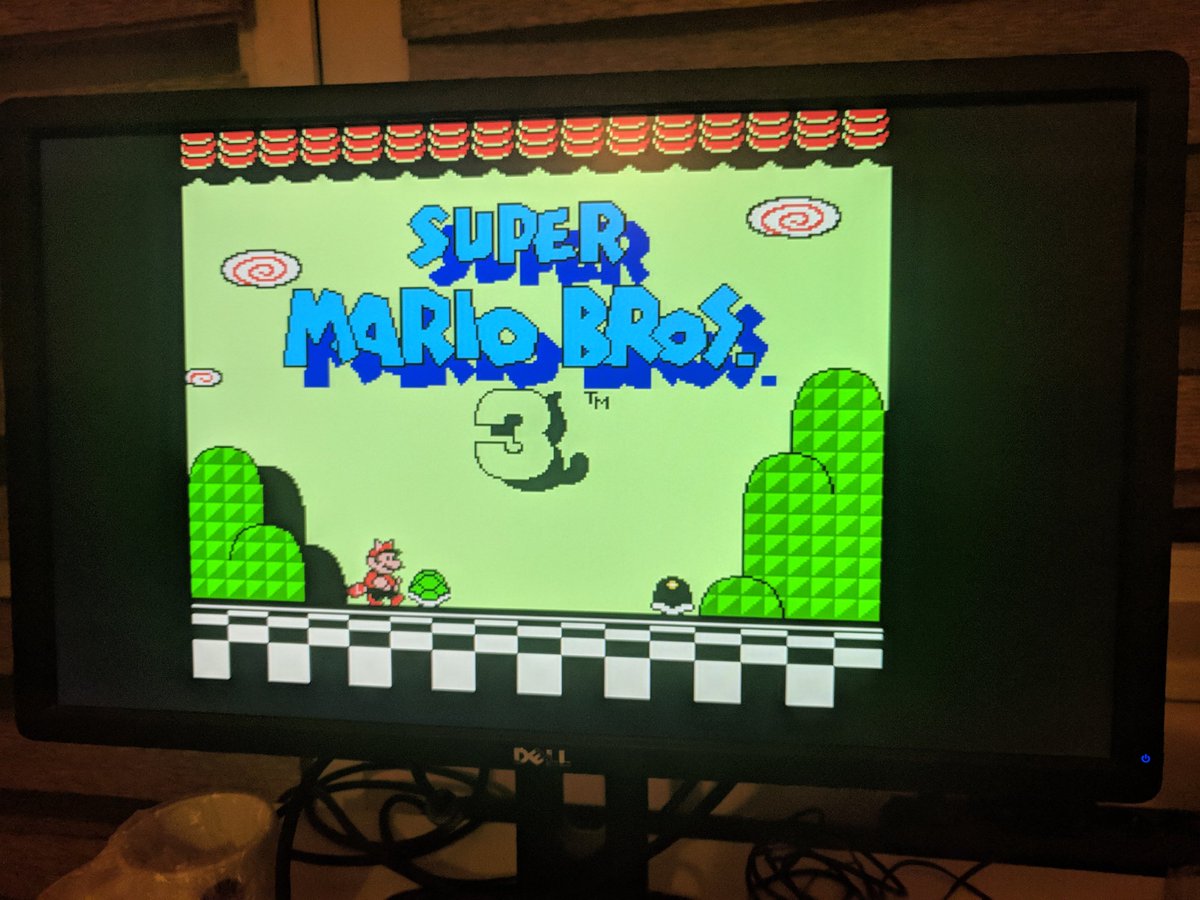

Switch back to #yosys and #ulx3s and run first time my new 5-staged pipelining #riscv cpu on ecp5 lattice fpga. CPU is written in SystemVerilog and I used sv2v transform it to verilog to have the possibility to synthesis it with yosys. Yosys works like hell in comparison to viva

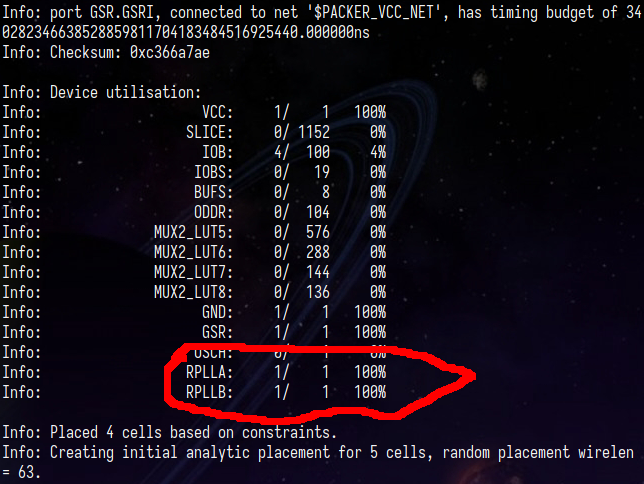

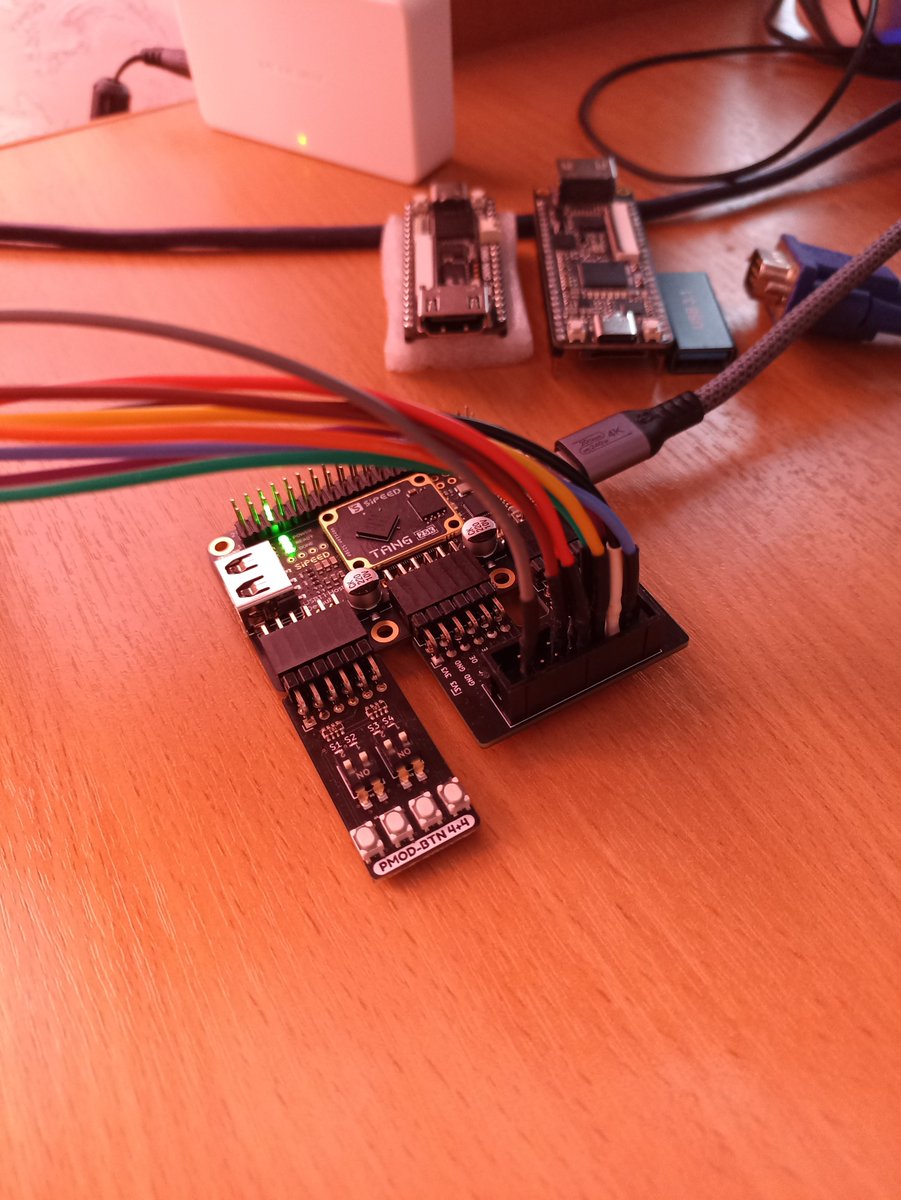

News about GW5 series - PLL went through #yosys, #nextpnr, and #apicula and started working!🍾 At the moment, there are a huge number of crutches, which I plan to remove in the near future and make the appropriate PR.😉 #fpga#gowin#sipeed

Gee! #yosys -> #nextpnr ->#gowin-pack successfully build and code a PLL primitive for #gowin #tangnano. The on-board quartz is 24MHz, the PLL generates ~72MHz Truly a great day! 😀 #apicula #fpga

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

Curious about gate level simulation? I prepared a github repo with detailed explanations - and source code - on how to simulate #Yosys output on CPU and GPU (incl. VGA display). It's surprisingly simple! Repo: github.com/sylefeb/Silixel

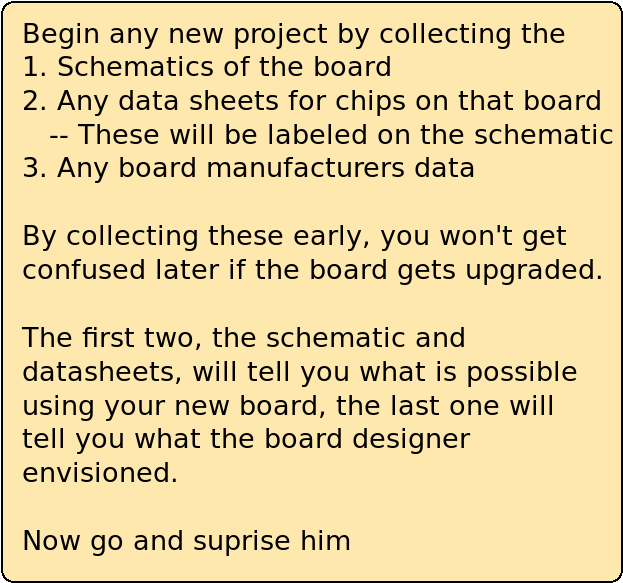

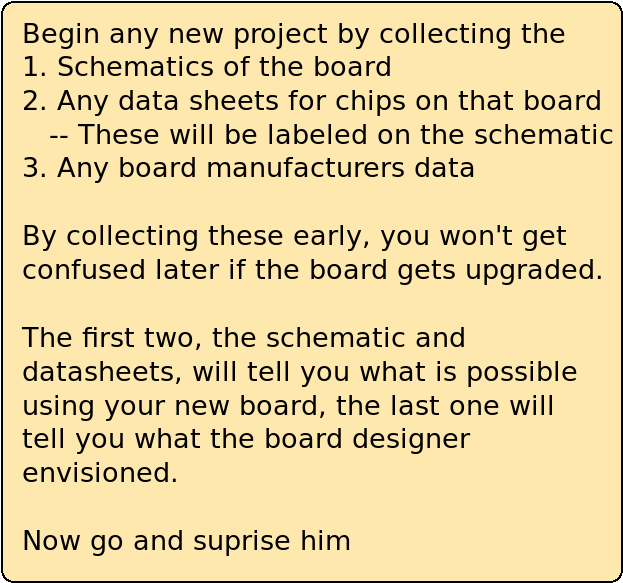

The first steps in any project, as discussed last night on #yosys -- freenode.irclog.whitequark.org/yosys/2019-01-…

So, now I have equipped my IceStick HX1K, which has 1280 LUTs, with my mini KianV processor + audio device. This was much easier than on my Unix SoC :). #FPGA IceStick music machine. @BrunoLevy01, we will also integrate this into your processor :) #verilog 4life #yosys

It has just come to my attention that the vendor IDE has a VGA example as part of it. So I just took it and compiled #yosys->#nextpnr->#apicula And marvel: no difference! The example uses PLL and it's the same source code! (almost) #fpga

TL;DR I tracked down a #yosys #ice40 DSP issue, took a deep dive into yosys internals and (I think?) squashed a tiny bug! (long thread) It all started with this difference (running #icebreaker):

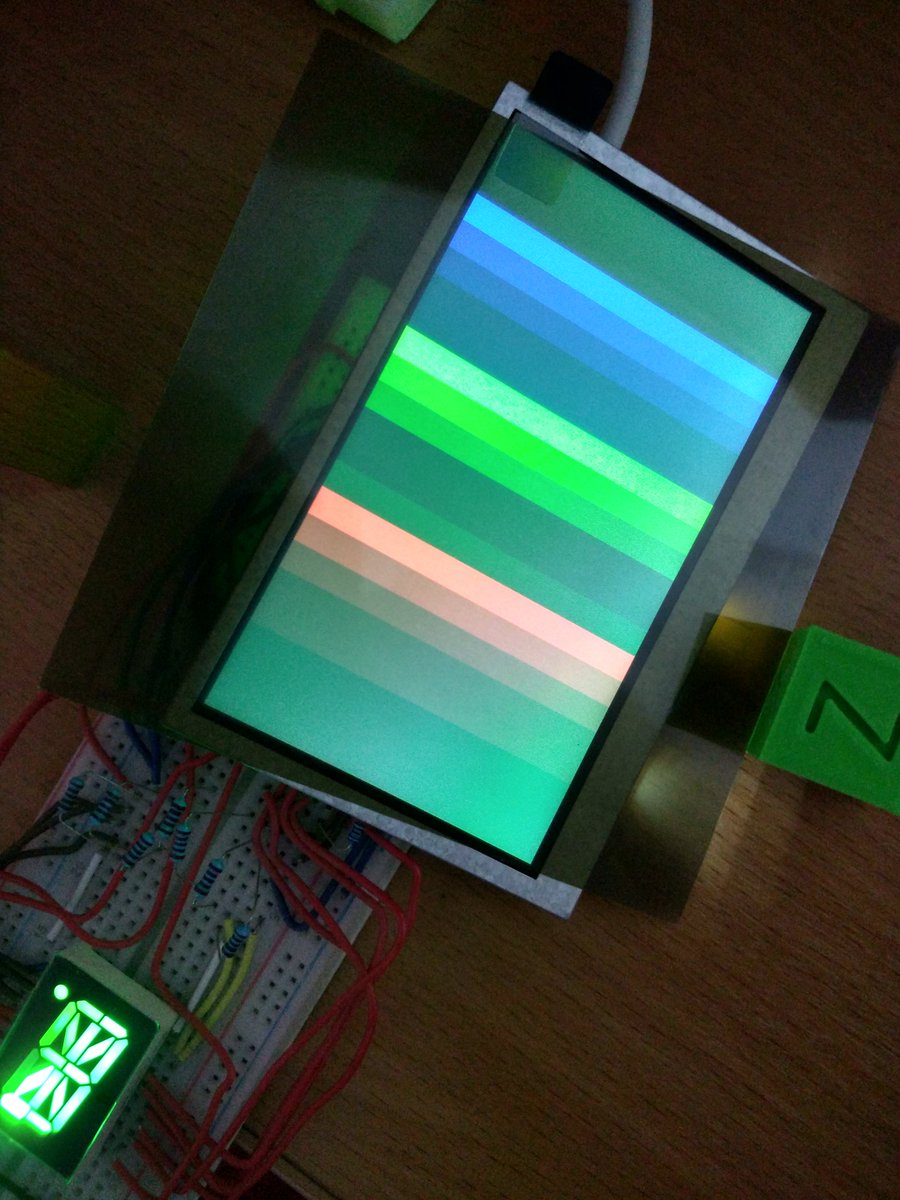

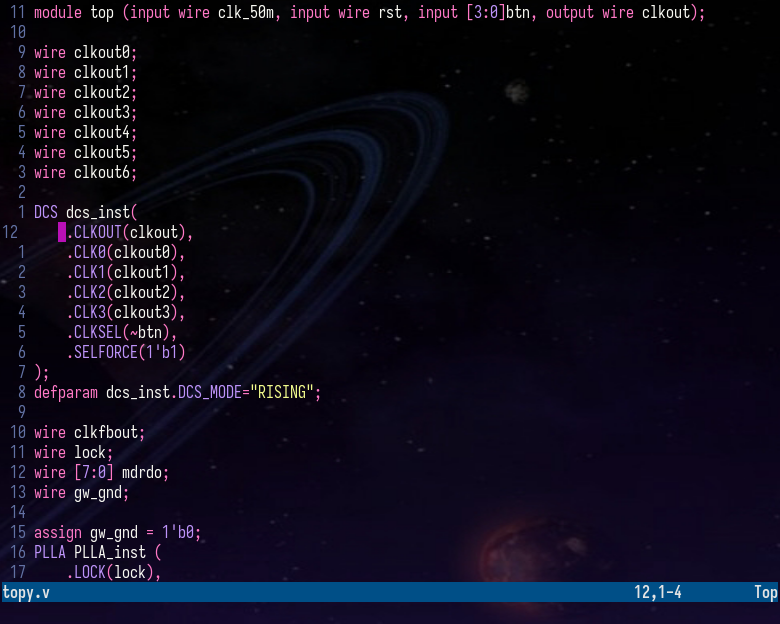

A test example of dynamic clock selection on the GW5A series #fpga, which goes through #Yosys* #nextpnr and #apicula * Strictly speaking, it does not go through Yosys because #gowin renamed the CLKx inputs to CLKINx for this primitive, but I temporarily changed their names.

News about GW5 series - PLL went through #yosys, #nextpnr, and #apicula and started working!🍾 At the moment, there are a huge number of crutches, which I plan to remove in the near future and make the appropriate PR.😉 #fpga#gowin#sipeed

Well, to the authors of #openFPGALoader😂, I can only add the ability to program this board in #Yosys #nextpnr and #apicula.😉 I don't think it will take much time, I just need it to appear on Asian marketplaces so I can buy it.😆

Design Quality: Power, Performance, Area (PPA) CVDP assesses the quality of generated RTL using logic synthesis tools (e.g., #Yosys, #Xcelium). Metrics: Worst Negative Slack (timing), total cell area, and switching power. These metrics distinguish usable designs from toy…

🛠️ Clifford Wolf — mastermind of Yosys, the open-source digital synthesis tool that brought FPGA design to the people. No NDAs. No million-dollar licenses. Just pure logic, unleashed. #FPGARevolution #Yosys #VerilogLiberation #OpenHardware

💡 Shoutout to Claire Wolf, creator of Yosys—the open-source synthesis tool that kicked down the FPGA gates. With her work, hackers, students, and startups can build silicon without signing NDAs. #Yosys #FPGA #OpenEDA #OSSRevolution

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

So, I grew up with #Yosys/nextpnr... you want awesome... here's the new 5-stage pipelined CPU, Kianv StealthV, in action... live synthesis, place & route. Two firmware switches and a transformation from hardcore SystemVerilog to Verilog. Pure awesomeness! @YosysHQ

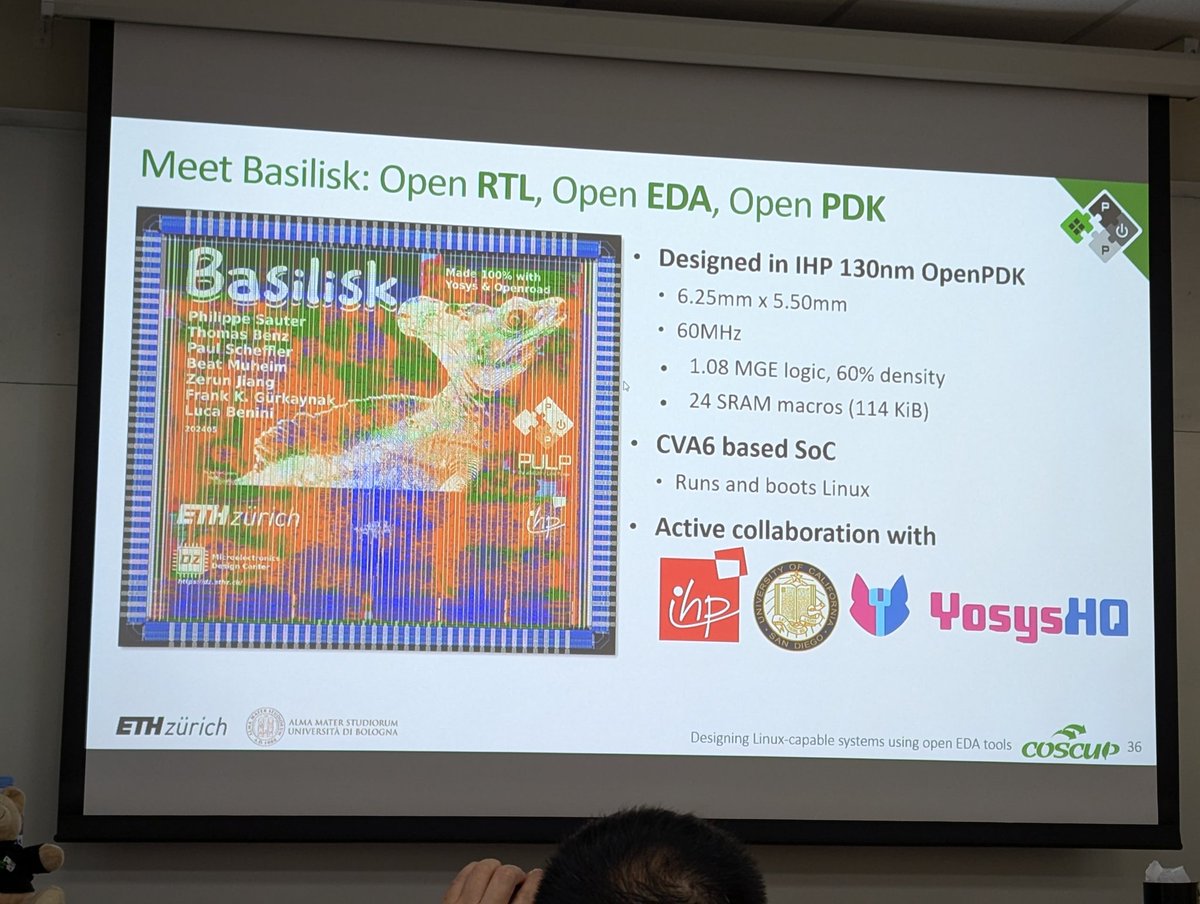

Now Philippe and Charlie from @pulp_platform talking about open tooling like #Yosys, #OpenLane , #Verilator and of course open #PDKs here at @coscup:) Happy to see @openhwgroup #CVA6 INSIDE #OpenHW #COSCUP #LINUX

It's crazy how picky one becomes with FPGAs. The toolchain is becoming more and more decisive for me. I prefer #Yosys/#nextpnr, ideally with #ECP5. It works without headaches. With Quartus, Gowin, or Vivado, or ... toolchains, I have a mental block; it doesn't feel good.

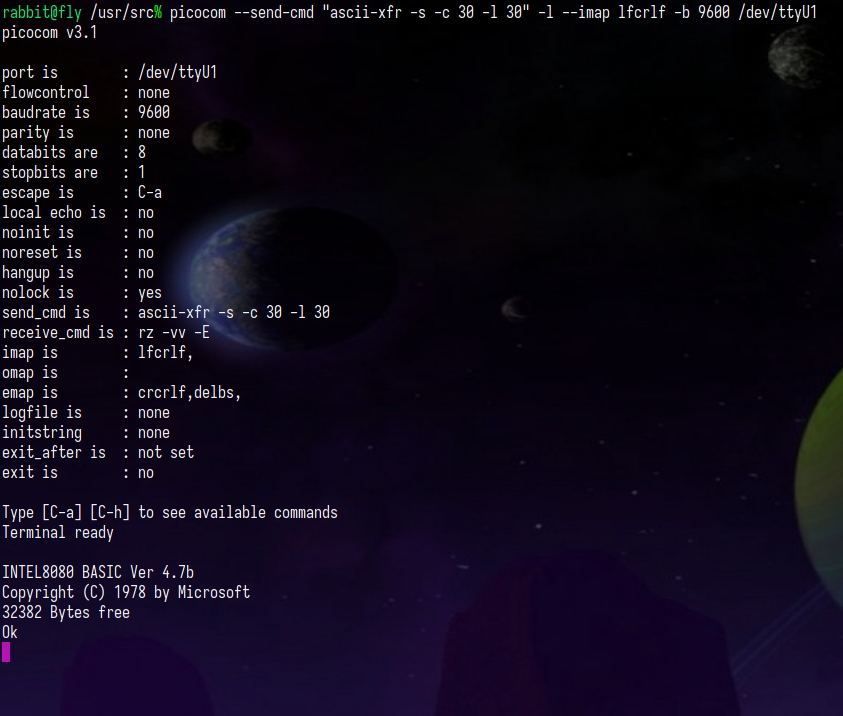

Gee! I discovered and corrected many funny features of BSRAM memory, and later this thing started working on #yosys #nextpnr #apicula! This is #Tangnano9k emulating a small system from the 80s with an i8080, 16K ROM, 32K RAM and a serial port.#fpga

Less than a week to go until out next #yosys user's group! 🙀 We'll be hosting a range of FPGA lightning talks & are thrilled to announce the following participants & their projects: ⭐️Pat Deegan's TT ASIC Simulator ⭐️Frans Skarman's Using a raspberry pi camera with an FPGA

Wanna participate in our next #yosys user group lightning talks about your #FPGA project using the open source tools? We'd love to hear from you! Just fill out the linked form. 😼 docs.google.com/forms/d/1gKbUf…

Curiously, even the simplest approach makes a pretty good hardware decoder (tools like #Yosys just do great work at optimisation) for 1.6bit (5 trits per byte) github.com/rejunity/tiny-…

I unpack 1 byte into 5 ternary. My unpacking approach is embarrassingly simple, but fits in a rather small logic circuit (#Yosys does great job here!) Each ternary is 2 bit lines: 1) 2's complement 8bit input 2) add/no-op. Accumulators are 17bit.

Join us tomorrow for the next #yosys user group! Sign up the newsletter for a reminder before we start: yosyshq.com/newsletter

This months’ #yosys user’s group will focus on hardware security! Katharina @K_CeesaySeitz & Flavian @FlavienSolt from ETH Zurich will introduce their tool for Information Flow Tracking (1/2)

This months’ #yosys user’s group will focus on hardware security! Katharina @K_CeesaySeitz & Flavian @FlavienSolt from ETH Zurich will introduce their tool for Information Flow Tracking (1/2)

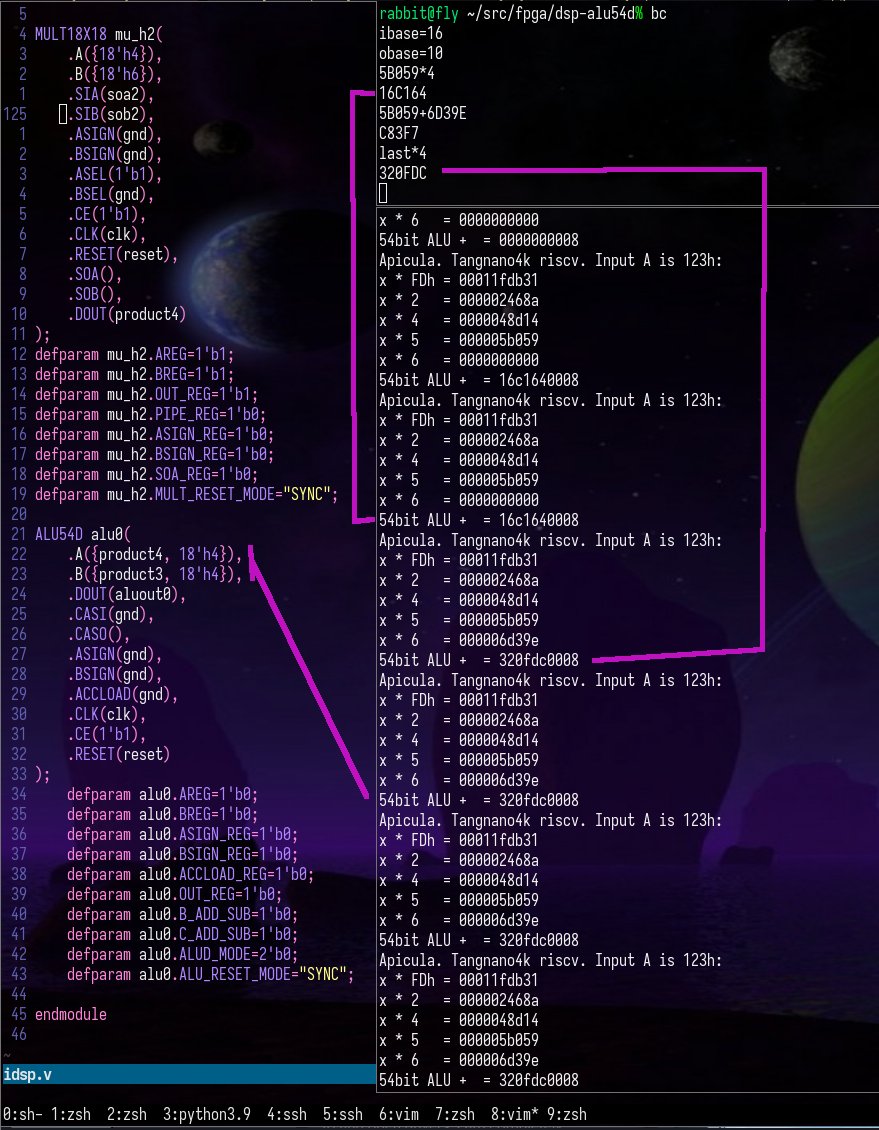

The ALU54D primitive from #dsp passed through #yosys - #nextpnr - #apicula earlier than planned. The picture shows the launch of a test example when an ALU is added to the end of a chain of five multipliers and adds the results of the 4th and 5th multipliers.#gowin#sipeed #riscv

Happy birthday @YosysHQ ! My favorite project powered by #yosys is @sylefeb's SILICE HDL: github.com/sylefeb/Silice It is fantastic to see new HDLs making things super easy. Love also @pipelinec_hdl, @suarezvictor does amazing things with it: github.com/JulianKemmerer…

Just got ICE40 UltraPlus $8 board from Texas. gnarlygrey.com/development-pl… Time to make #Yosys #IceStorm support for it.

Finally, the Nexys Video board arrived for doing HW with Artix-7 fpga using Opensource EDA tools #Yosys #Symbiflow FuseSoC and learning languages such as #Chisel and #Amaranth hdl.

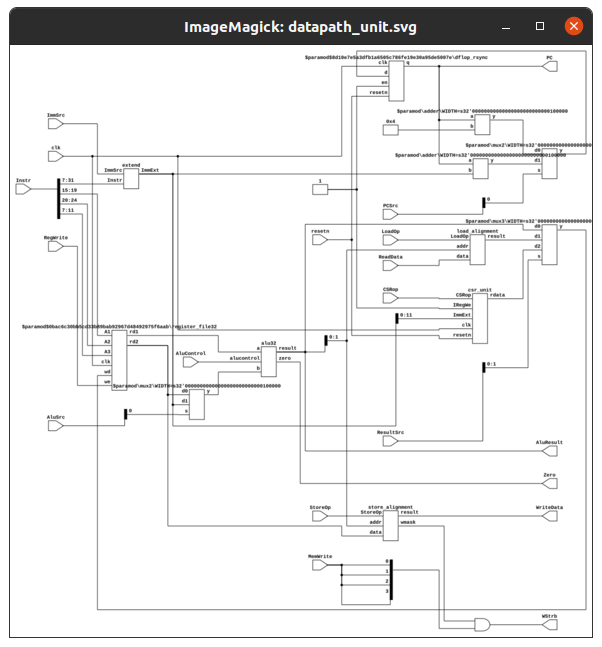

the beauty of datapath unit! Make from verilog rtl schematic via #yosys #netlistsvg. God bless that tools...fuckn fast and helpfull! Check all pathes are visually correct!

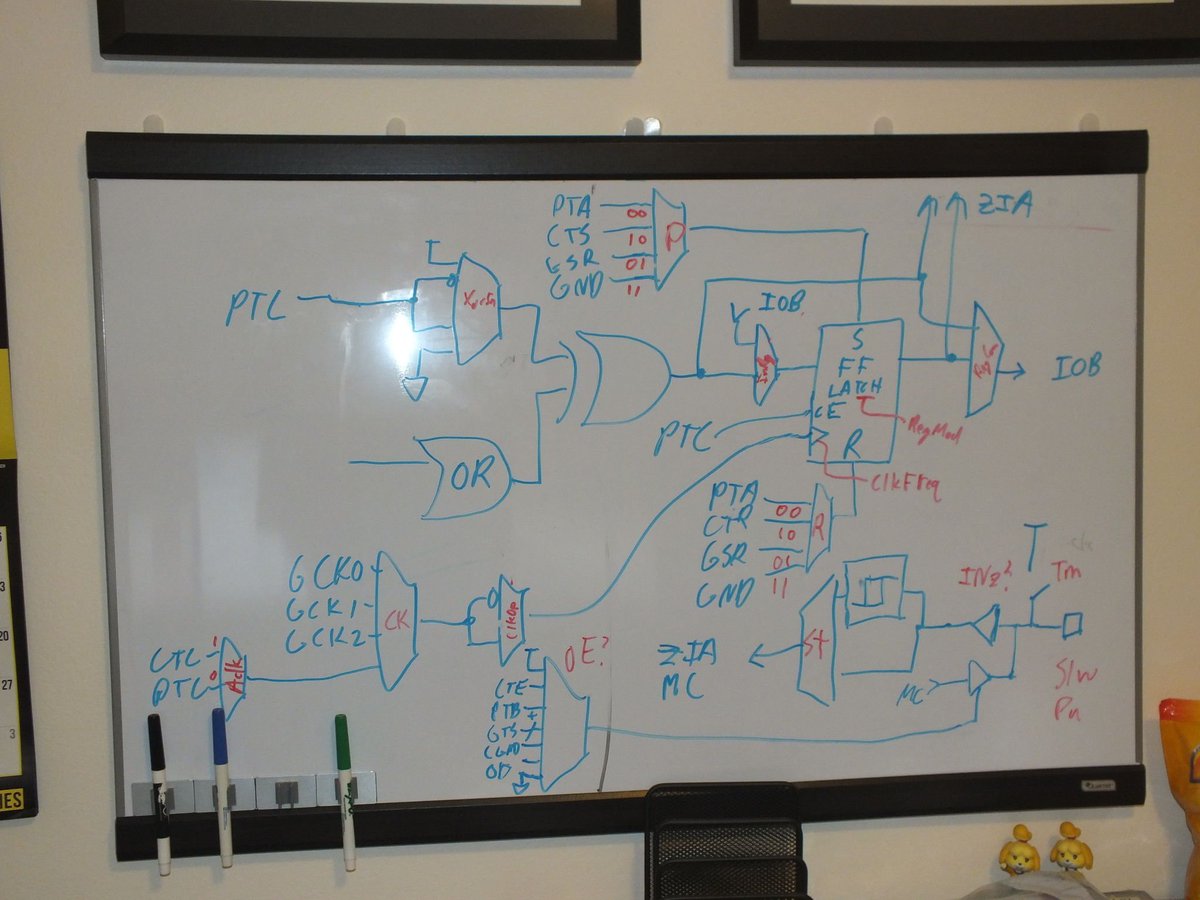

#CPLD bitstream reverse engineering with @rqou_. Coming soon: #openfpga + #yosys support for CoolRunner-II?

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

That's it, a full open source FPGA stack from @YosysHQ generating SERV, a @risc_v core by @OlofKindgren on a RISC-V host, the @SiFive Unmatched. Corescore was 100% built and programmed into @RadionaOrg ULX3S FPGA in RISC-V! Open source to the core! #RISCV #FPGA #Yosys #opensource

The first steps in any project, as discussed last night on #yosys -- freenode.irclog.whitequark.org/yosys/2019-01-…

Simulating #fpga designs on a GPU made simple! I stumbled upon a gem in the Google CTF contest: reversing-gpurtl. This is from 2019, but I missed it somehow (1/13) TL;DR: Simulating a (simple) design #Verilog => #Yosys => #GPU (yes, for real). Let's take a closer look! 👇

life is too short for #vivado just use #yosys #nextpnr to have hobby life balance... ~1.40 minutes for a bitstream instead of 20min or more

2/ Some weeks ago I started investigating gate-level simulation, using Google CTF 2019 reversing-gpurtl as a starting point. After revisiting it I was able to simulate several designs, such as #Silice VGA demos and @risc_v processors. This directly simulates the output of #yosys

Thanks to the Open Source #fpga community for making all of this possible! #yosys #nextpnr @yosyshq @1bitsquared , and many other great contributors.

News about GW5 series - PLL went through #yosys, #nextpnr, and #apicula and started working!🍾 At the moment, there are a huge number of crutches, which I plan to remove in the near future and make the appropriate PR.😉 #fpga#gowin#sipeed

Curious about gate level simulation? I prepared a github repo with detailed explanations - and source code - on how to simulate #Yosys output on CPU and GPU (incl. VGA display). It's surprisingly simple! Repo: github.com/sylefeb/Silixel

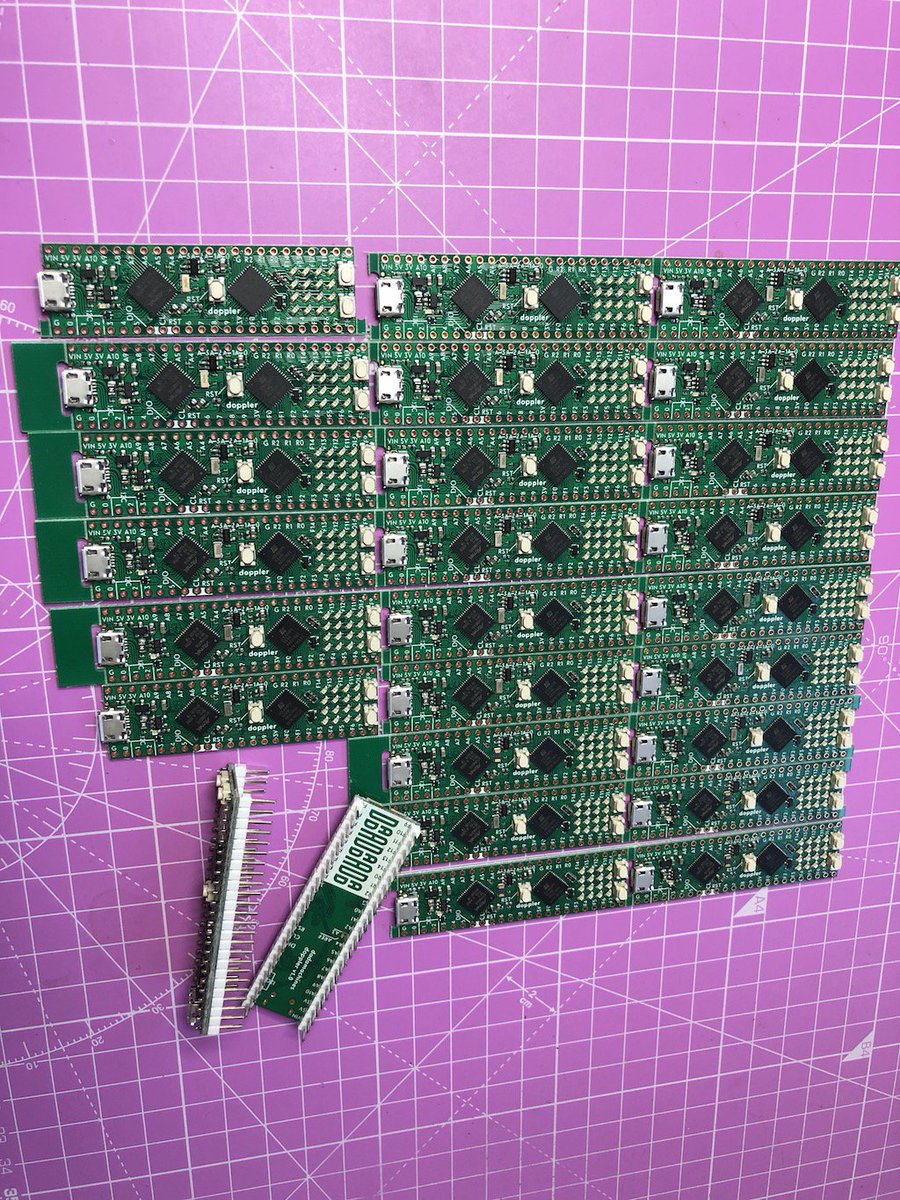

got first test batch of doppler prototype boards. FPGA meets samd51. #verilog #yosys #Arduino #FPGA @ico_TC

Something went wrong.

Something went wrong.

United States Trends

- 1. Jets 83.1K posts

- 2. Jets 83.1K posts

- 3. Justin Fields 9,439 posts

- 4. Aaron Glenn 4,549 posts

- 5. Sean Payton 2,576 posts

- 6. London 204K posts

- 7. #HardRockBet 3,398 posts

- 8. Bo Nix 3,669 posts

- 9. Garrett Wilson 3,441 posts

- 10. HAPPY BIRTHDAY JIMIN 155K posts

- 11. #DENvsNYJ 2,217 posts

- 12. Tyrod 1,706 posts

- 13. #OurMuseJimin 200K posts

- 14. #JetUp 2,003 posts

- 15. #30YearsofLove 176K posts

- 16. Bam Knight N/A

- 17. Peart 1,906 posts

- 18. Kurt Warner N/A

- 19. Sutton 2,826 posts

- 20. Breece Hall 1,964 posts