#pipelinec résultats de recherche

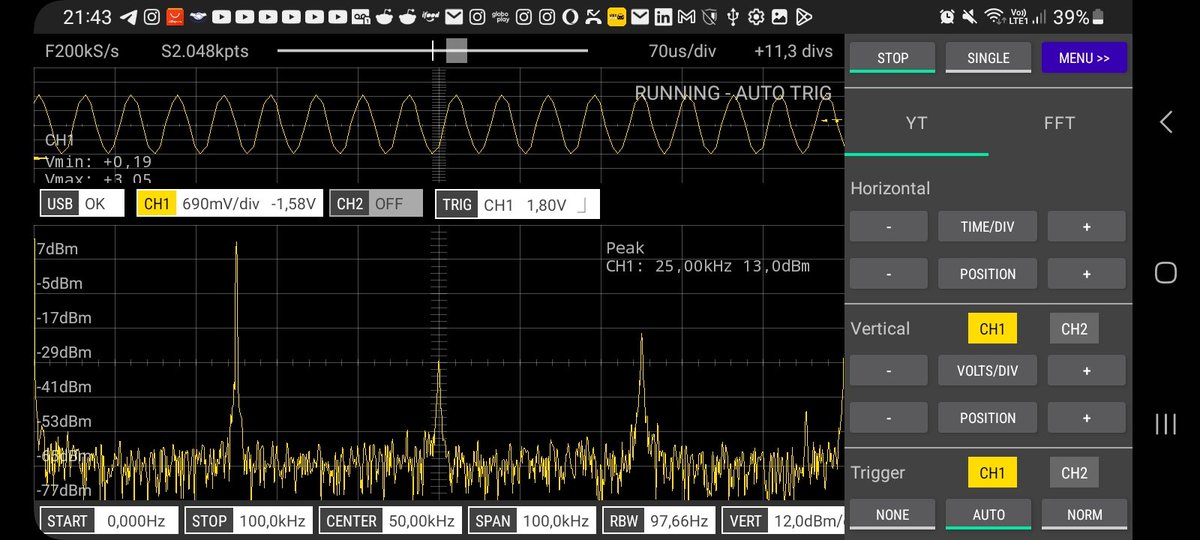

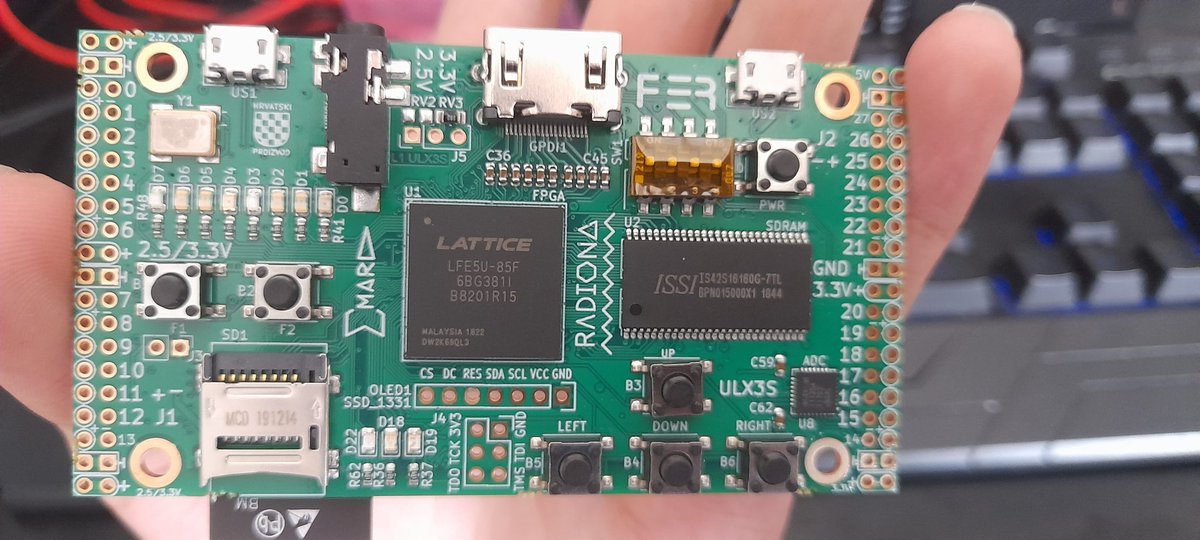

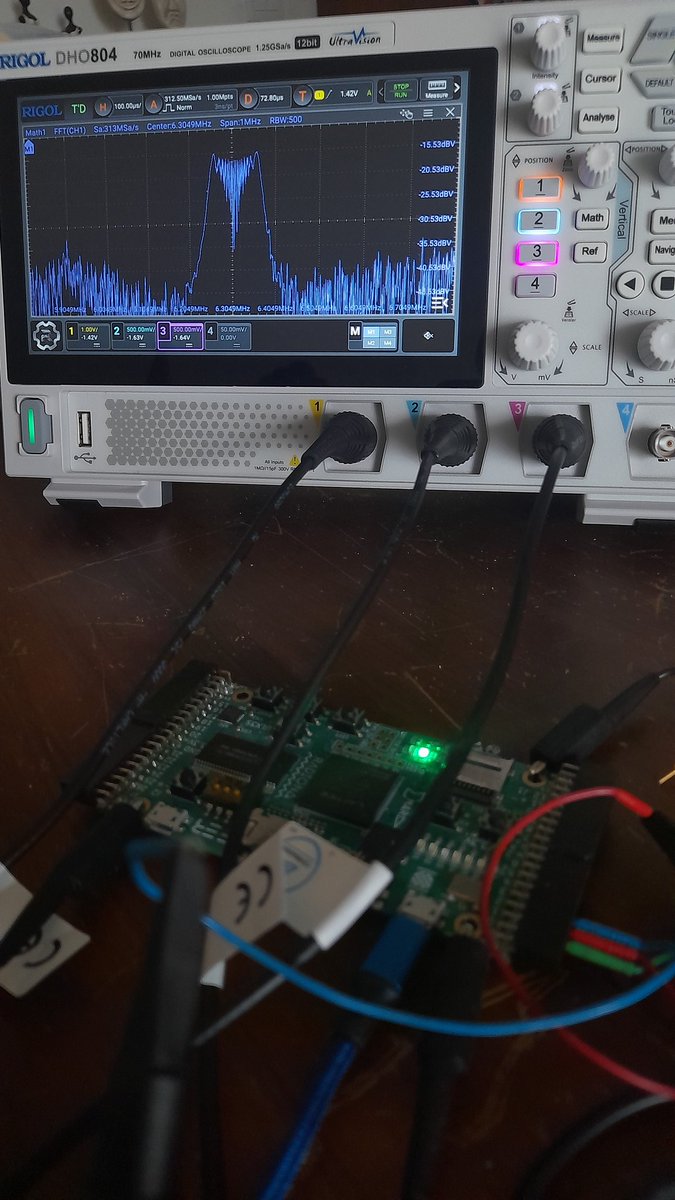

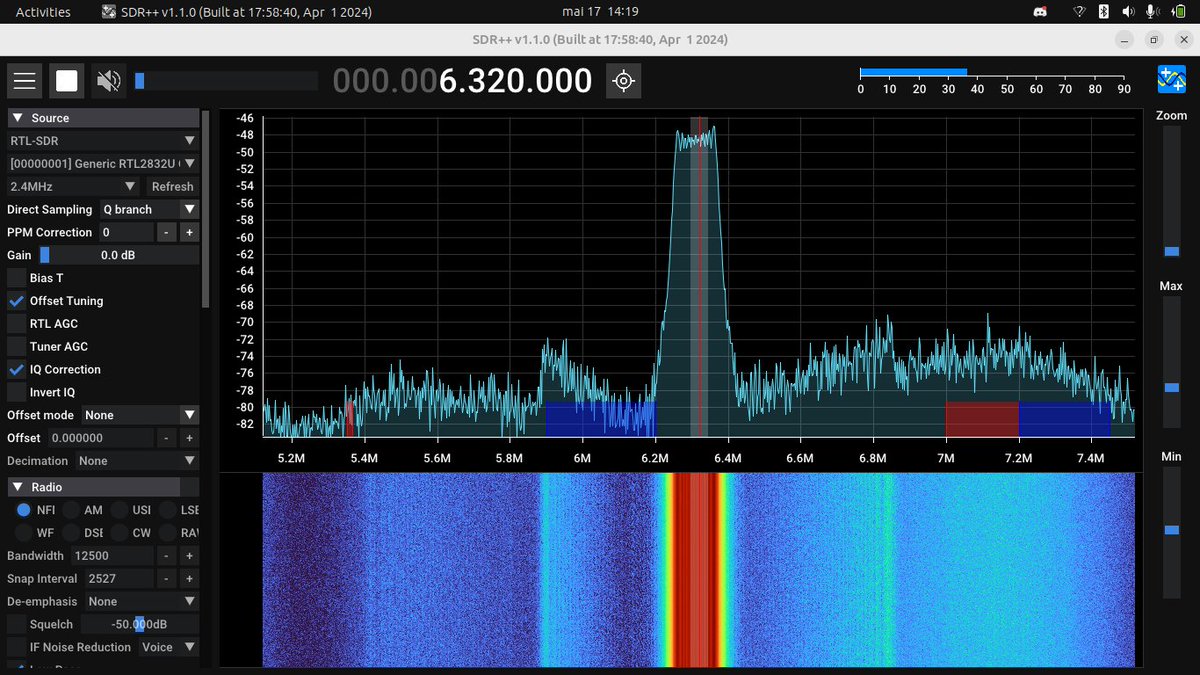

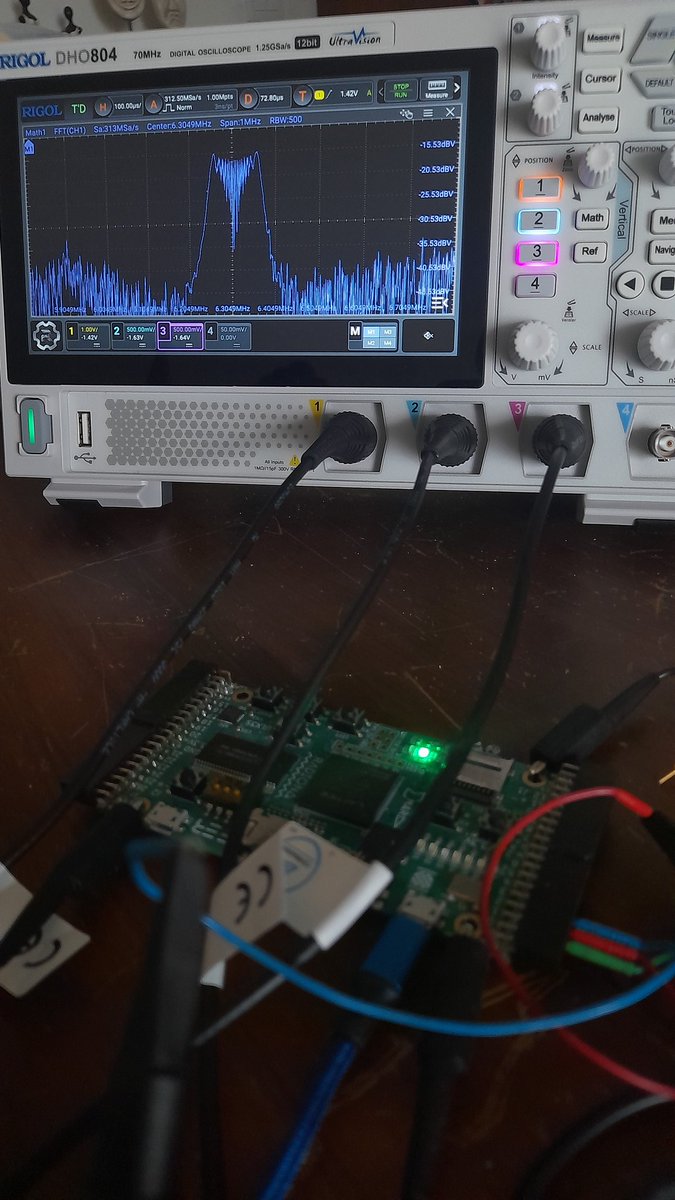

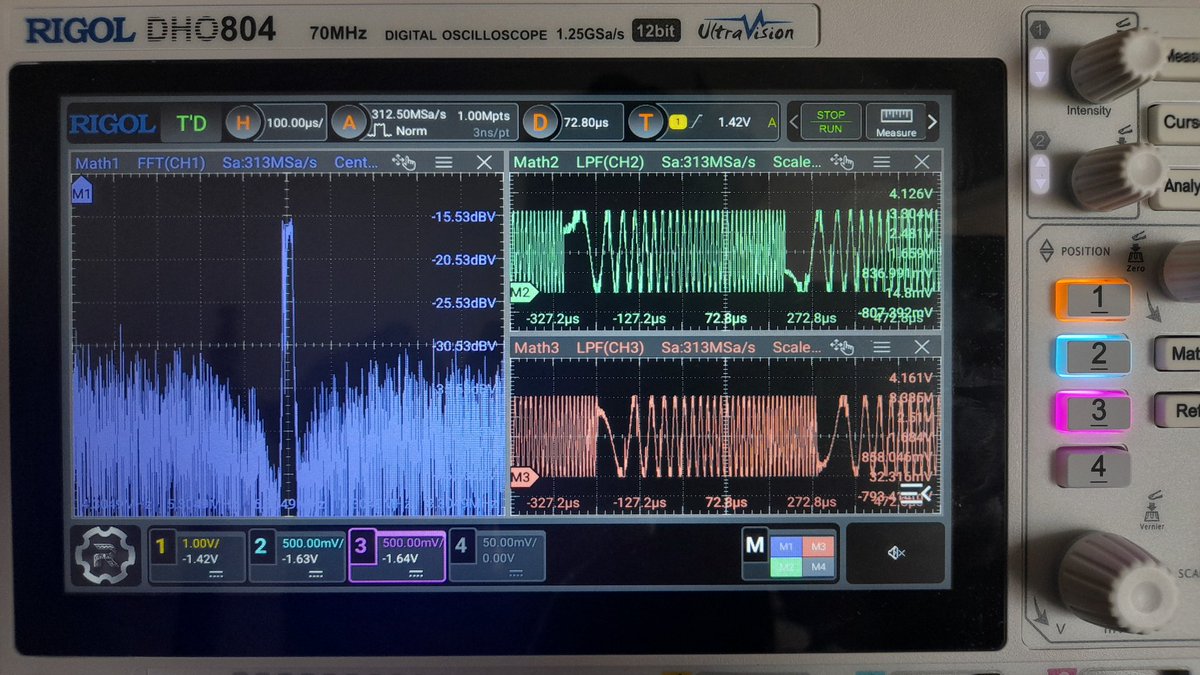

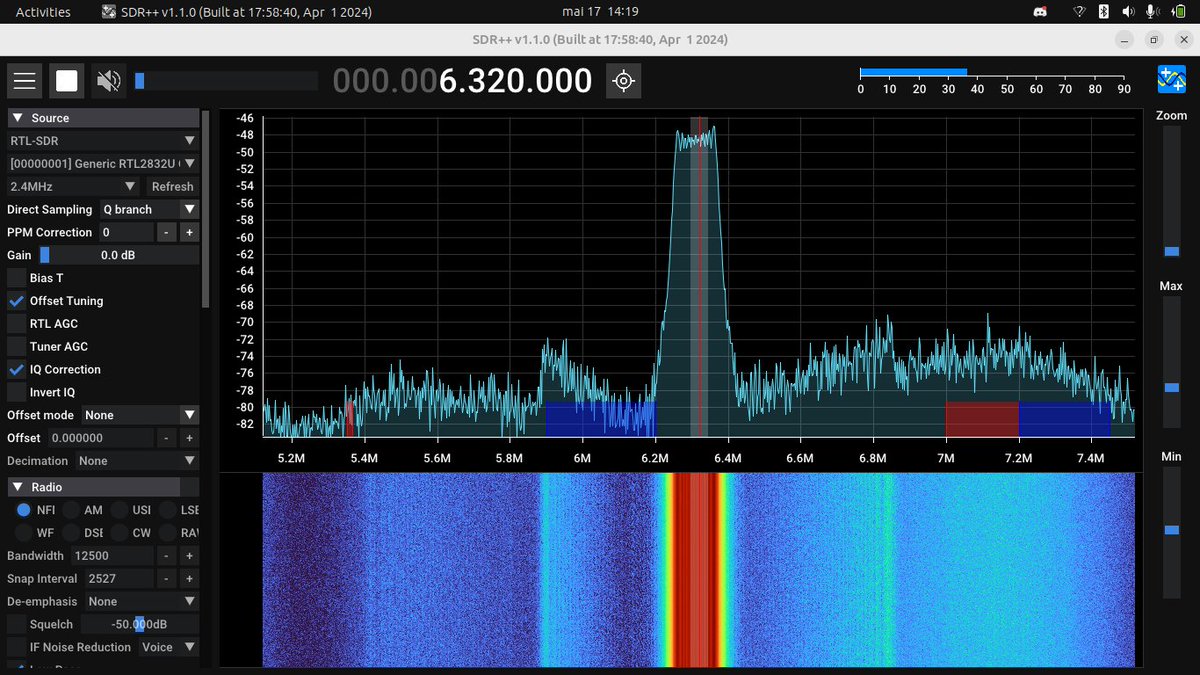

So... I've made a little "LoRa" (CSSS) beacon demo with #ULX3S and #PipelineC ! Ramp Nco ("SF6") -> Sine / Cosine NCO's => 2nd Order Delta sigma DAC => digital iq mixer -> output #sdr #fpga #rf #csss #lora #dsp #dac #sigmadelta #alldigitaltx

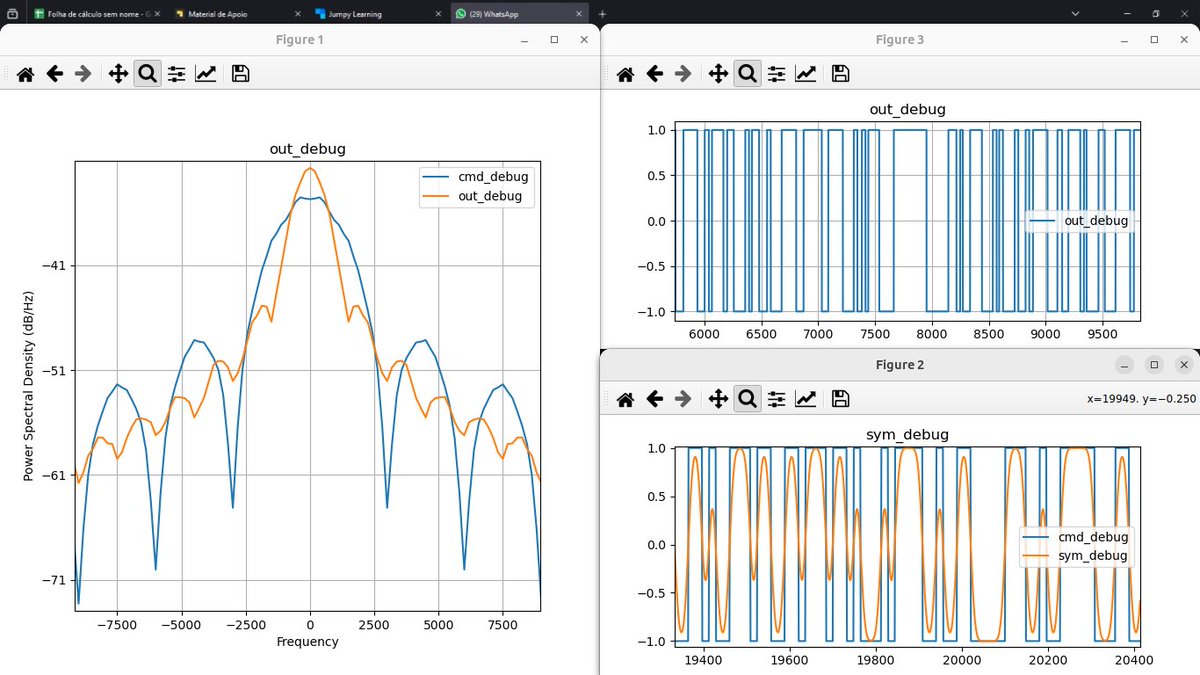

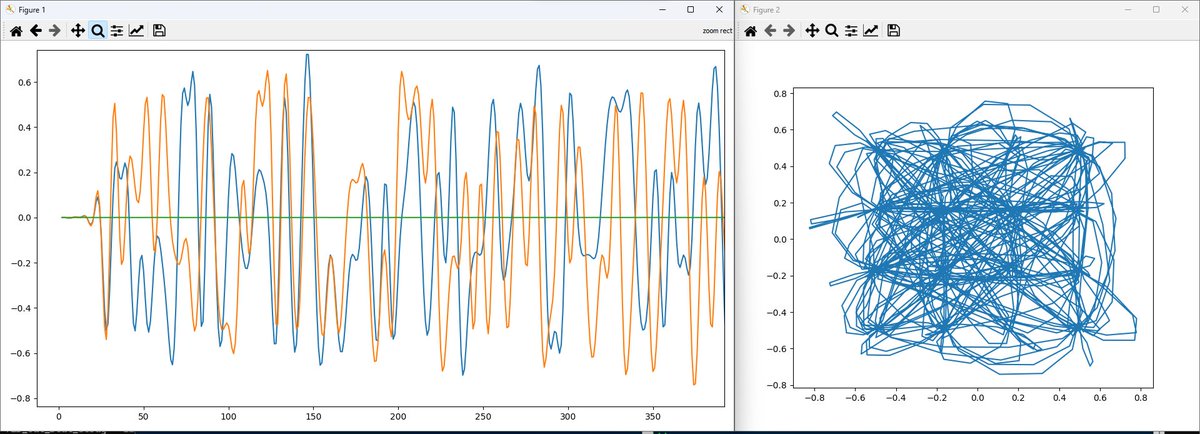

#QAM16 Modulator made with #PipelineC simulation with #GHDL and cocotb! Raised Cosine filter with 0.35 rollof and 4 samples/symbol ! #fpga #qam #sdr #dsp

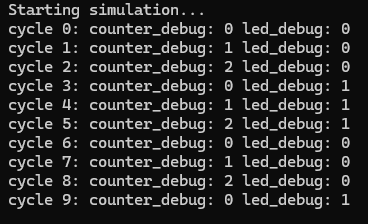

Blinking the #ULX3S led with #PipelineC ! @pipelinec_hdl is a Magic tool that turns C into HDL 🔥 #fpga #ledblink #lattice

Ethernet Loopback Works! Made with #PipelineC! Thanks for the help Julian Kemmerer @pipelinec_hdl ! #100baseT #ethernet on a #ulx3s #fpga using a #lan7820 board!

Blinking leds on the #StratixV #FPGA using C code with #PipelineC ! #gsd5 #altera #quartus #intel #microsoft #catapult #sotoreypeak

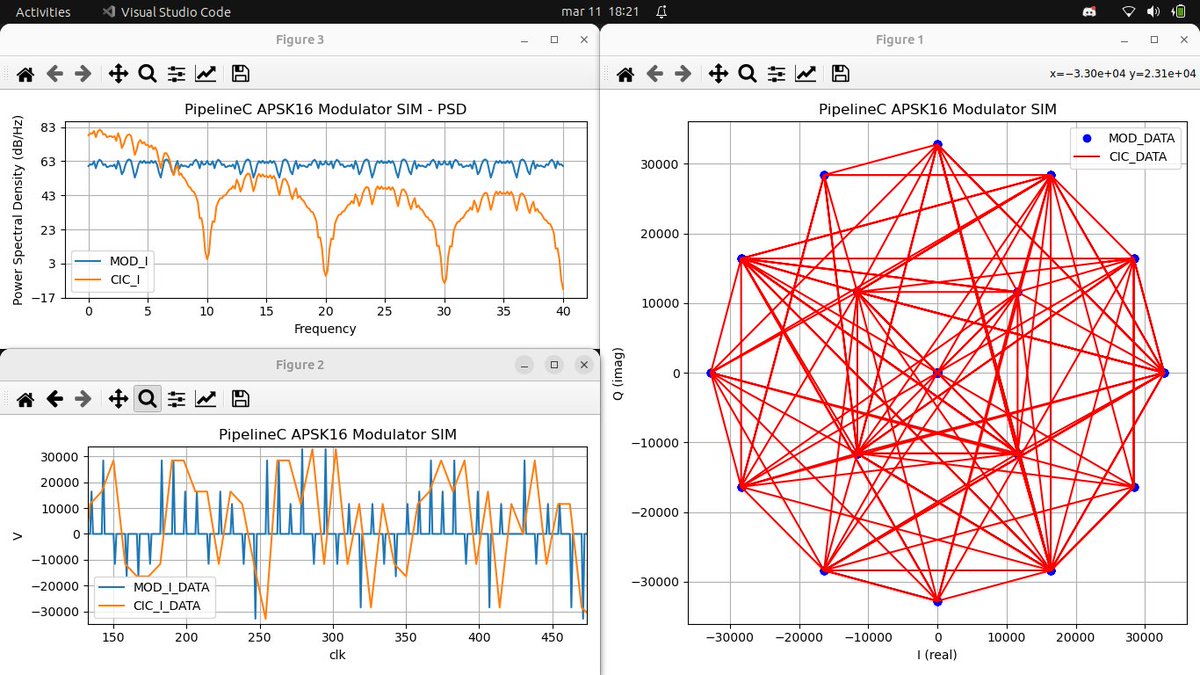

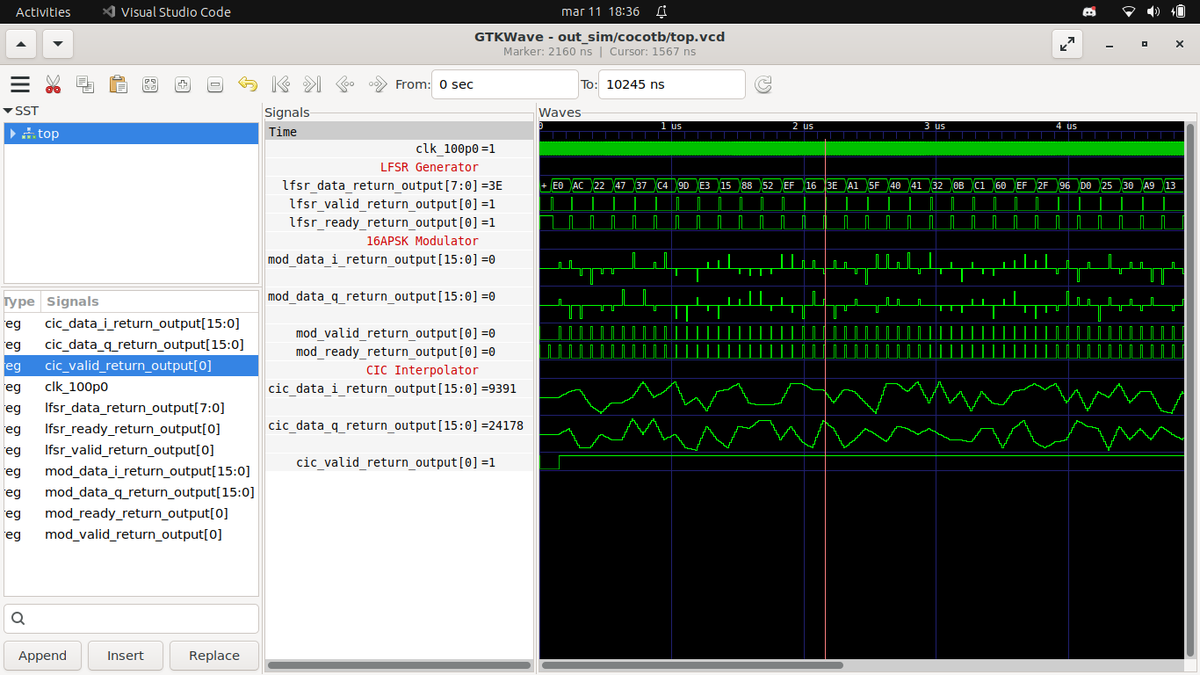

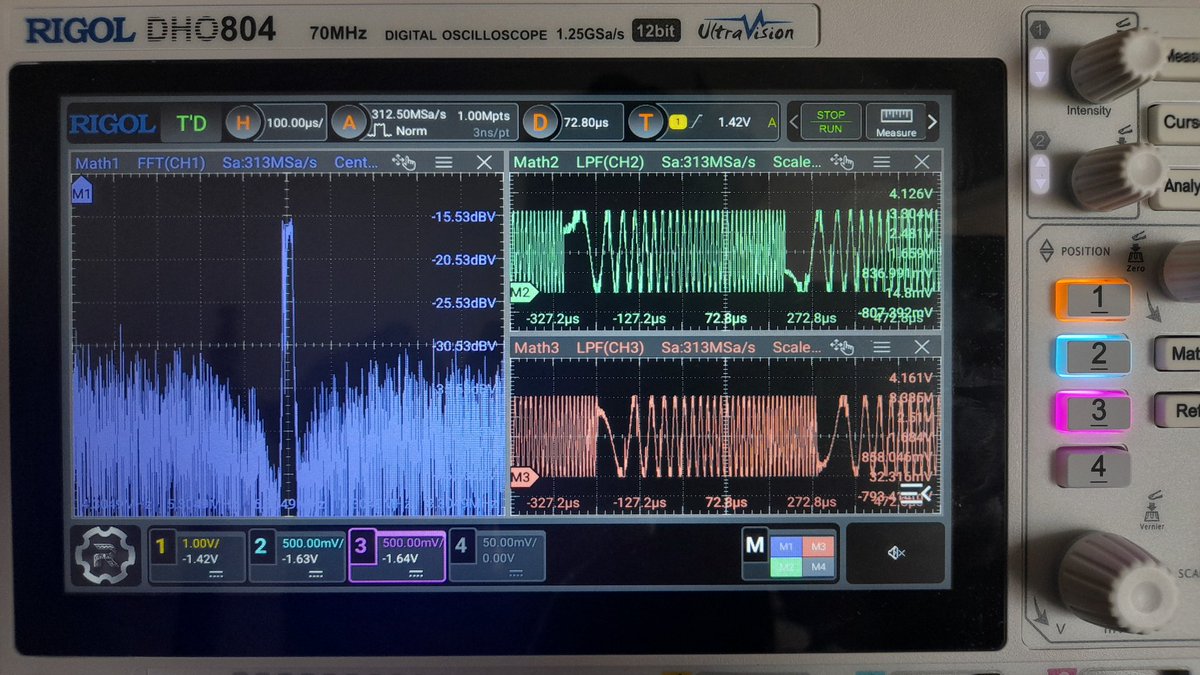

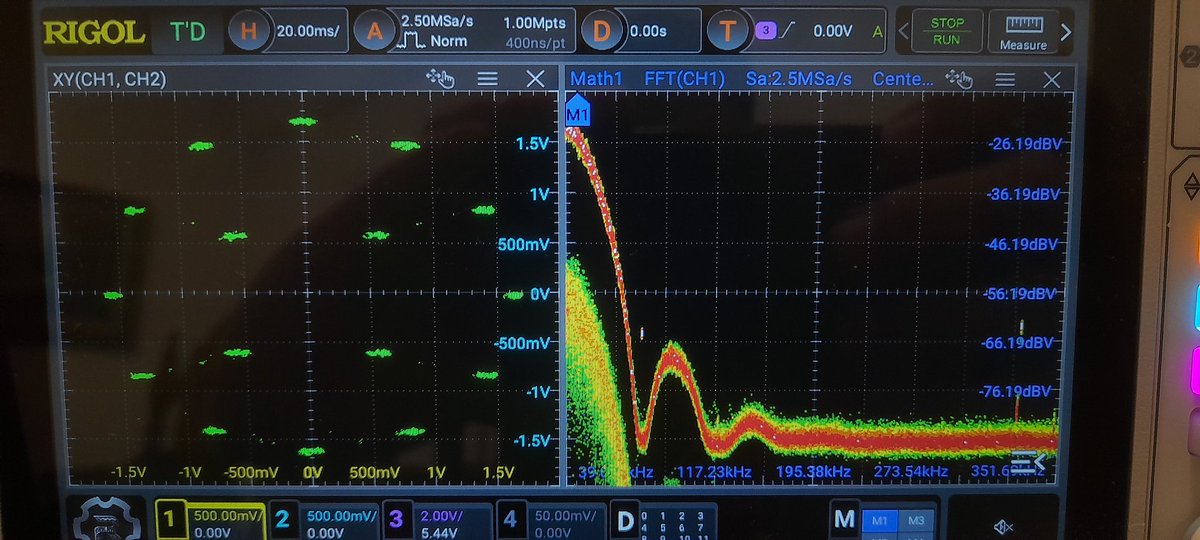

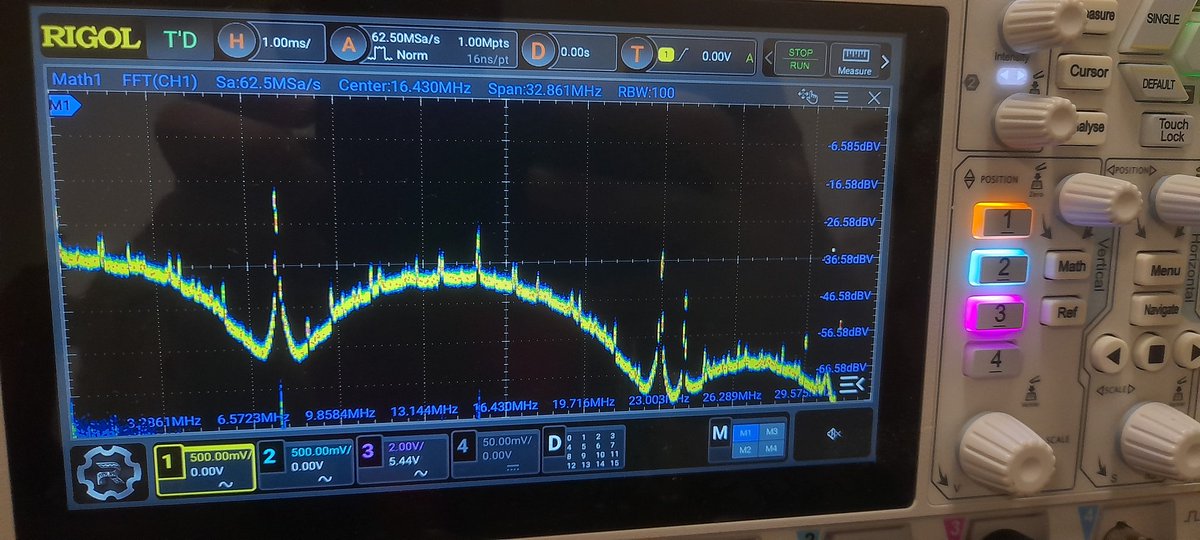

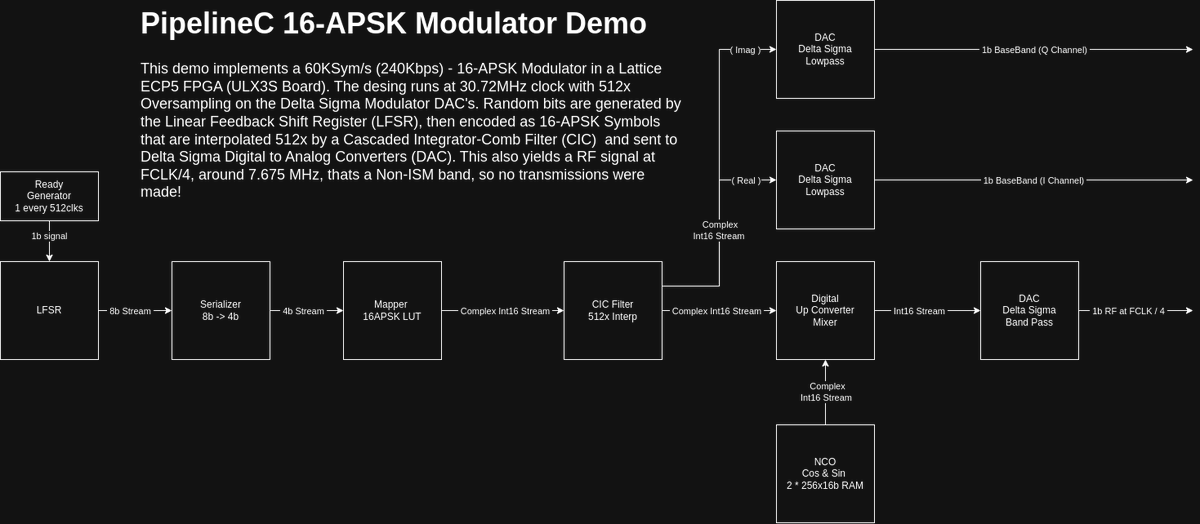

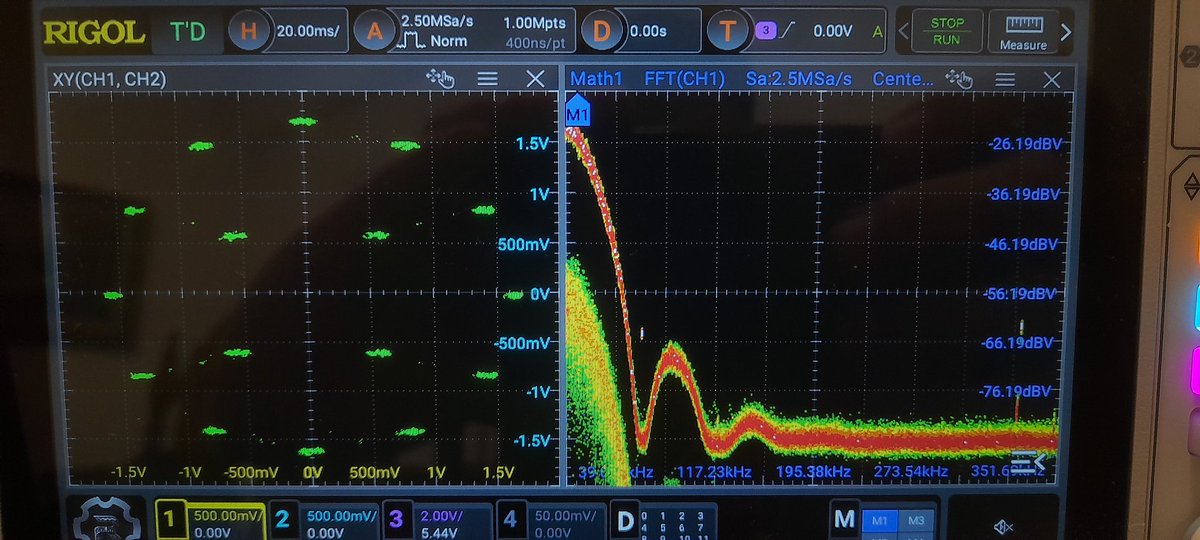

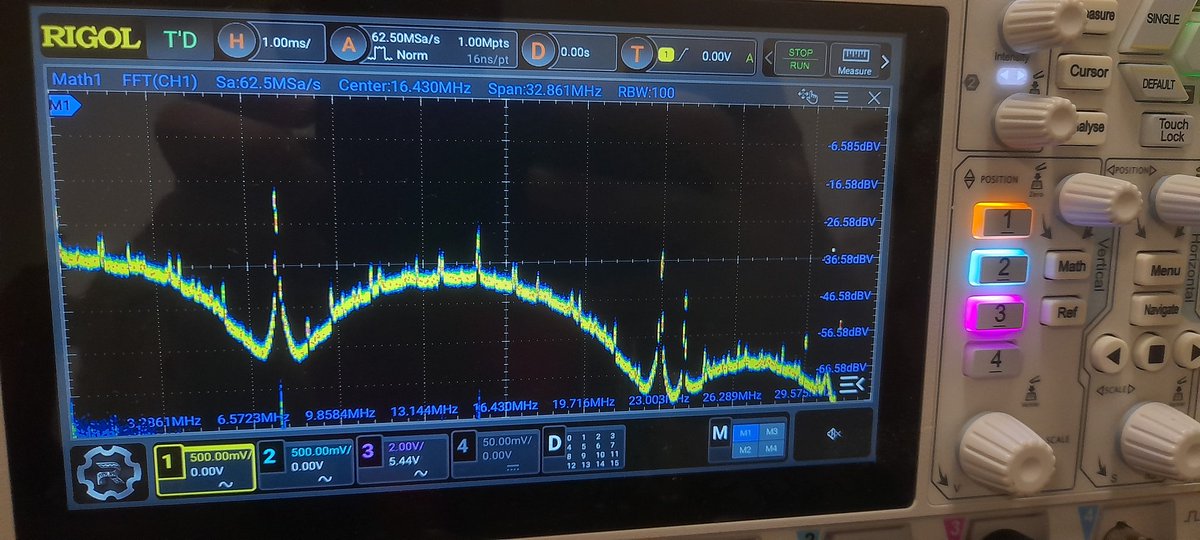

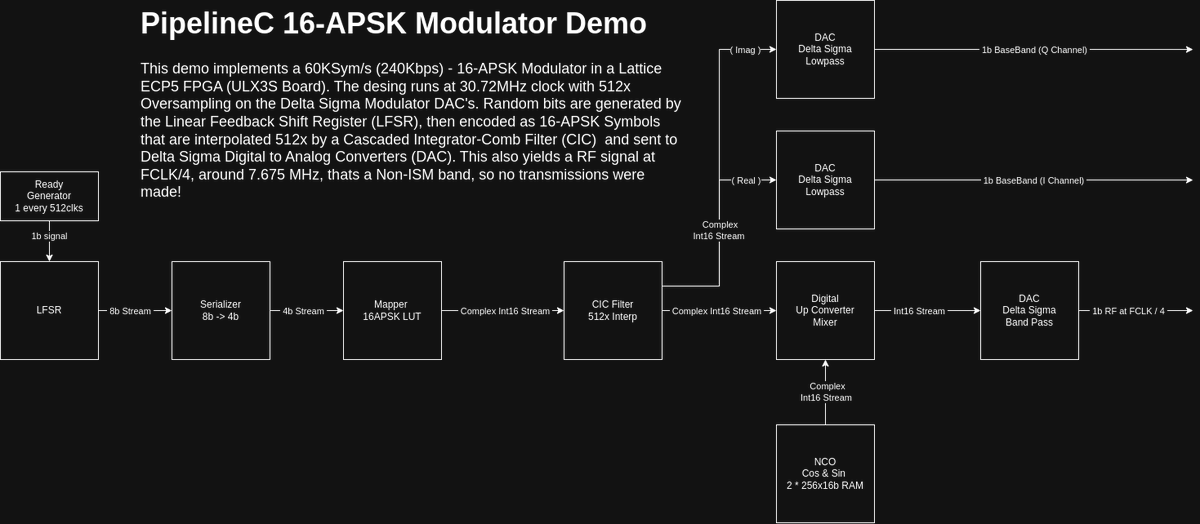

Following the previous post about the #FPGA #16APSK Modulator made with #PipelineC ... Here are some real world tests using the ULX3S Board! #dsp #sdr #apsk #hdl #ulx3s #dac #deltasigma #rf

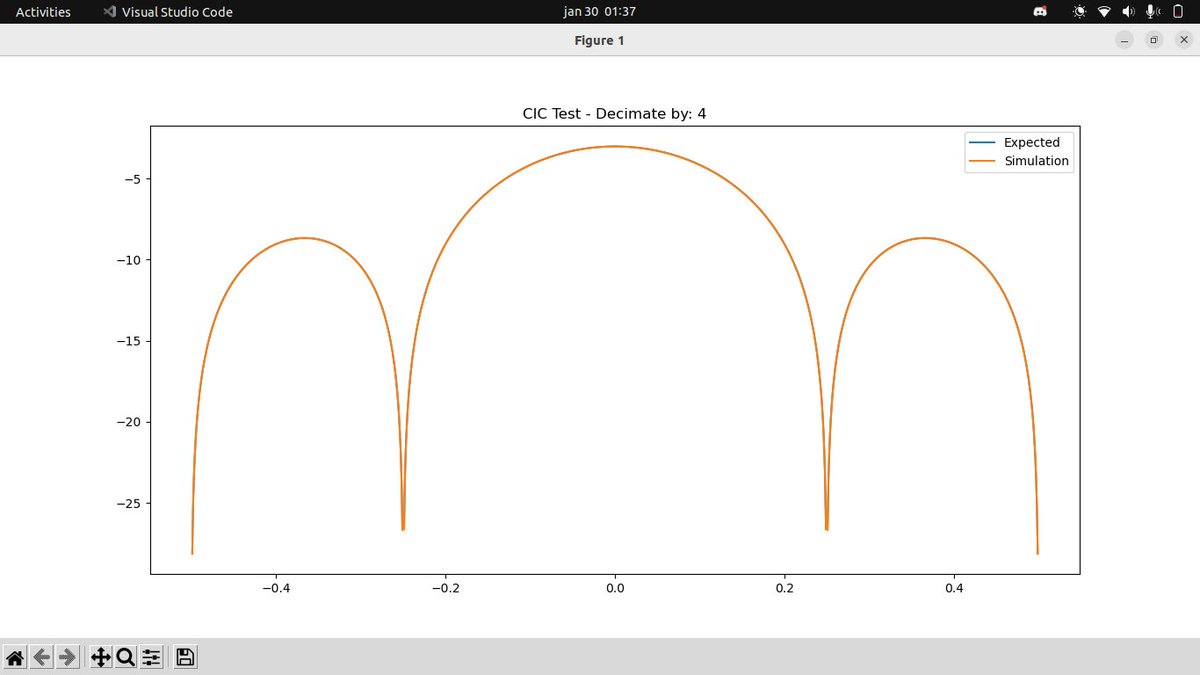

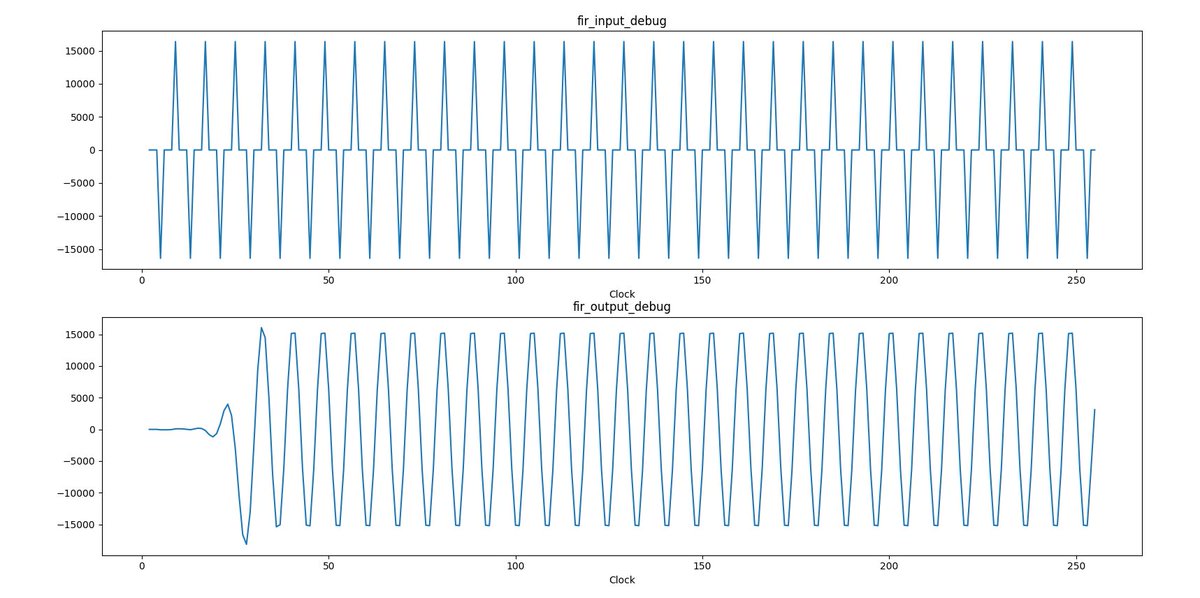

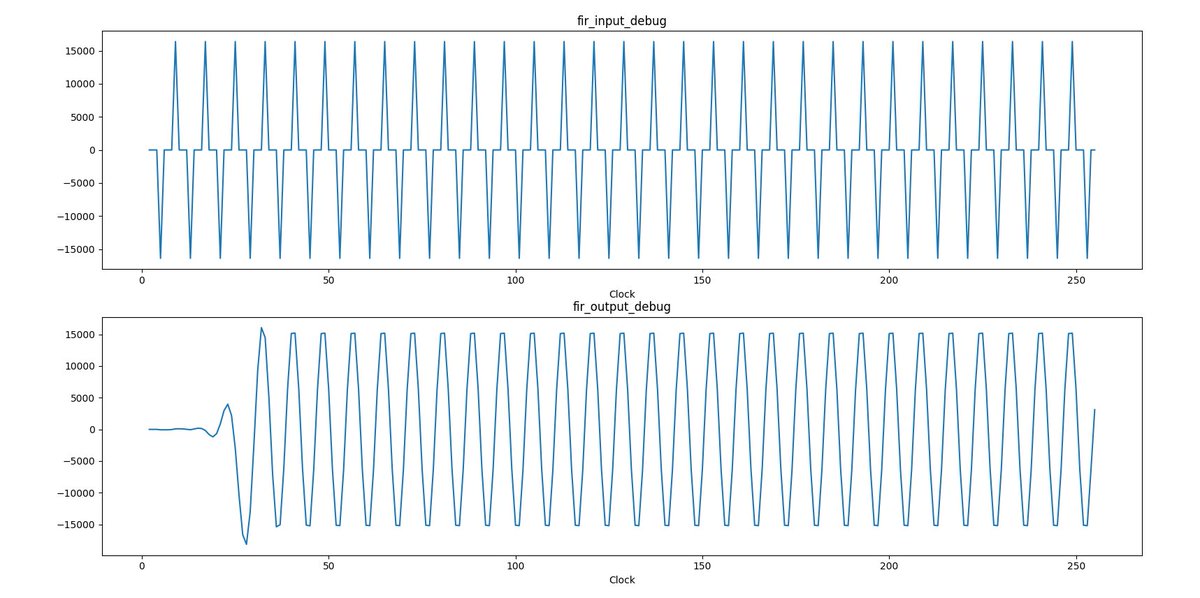

#PipelineC Raised Cosine FIR Filter simulation with GDHL + cocotb! QAM modulator comming next... #fpga #ghdl #vhdl #rf #dsp #sdr

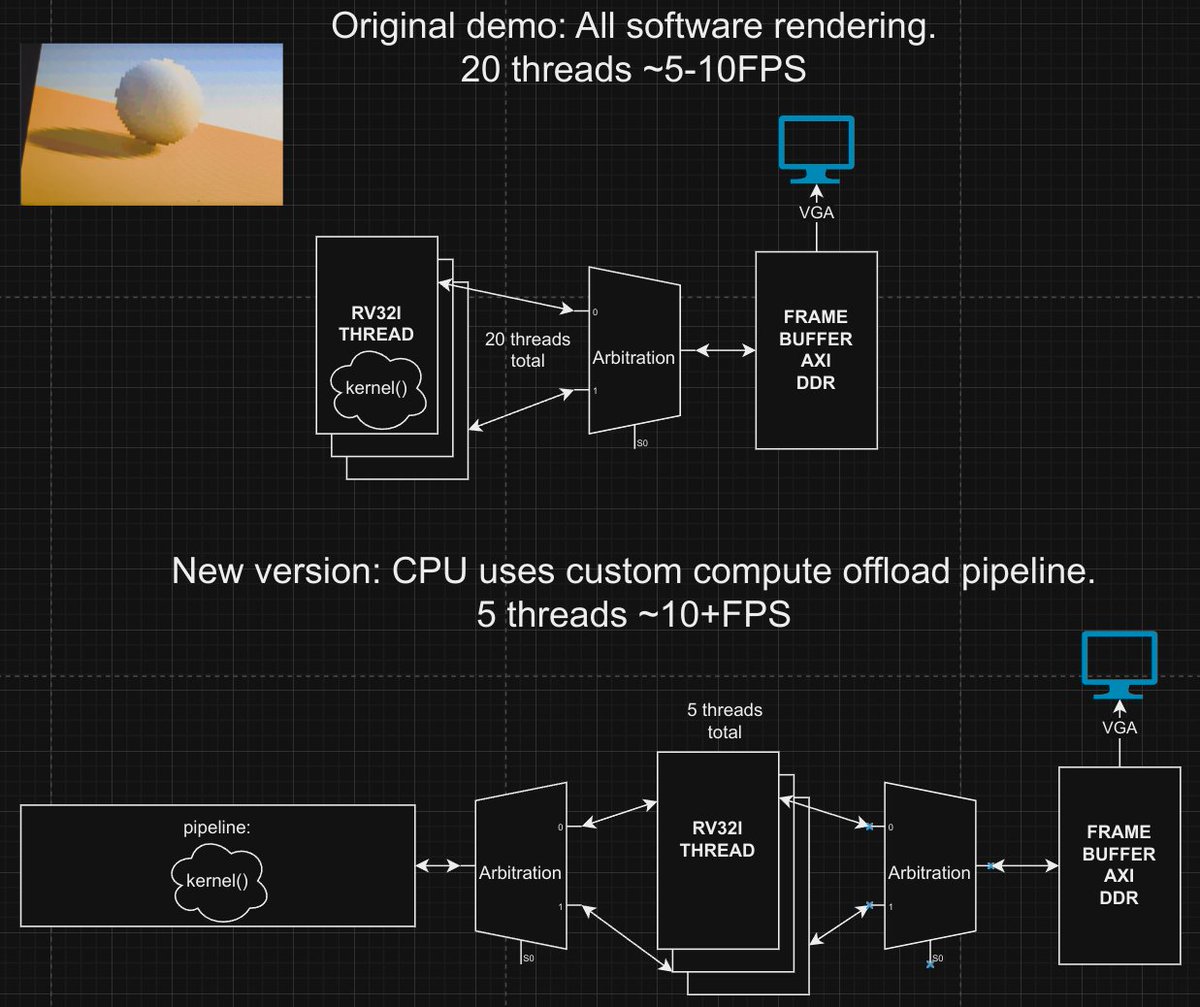

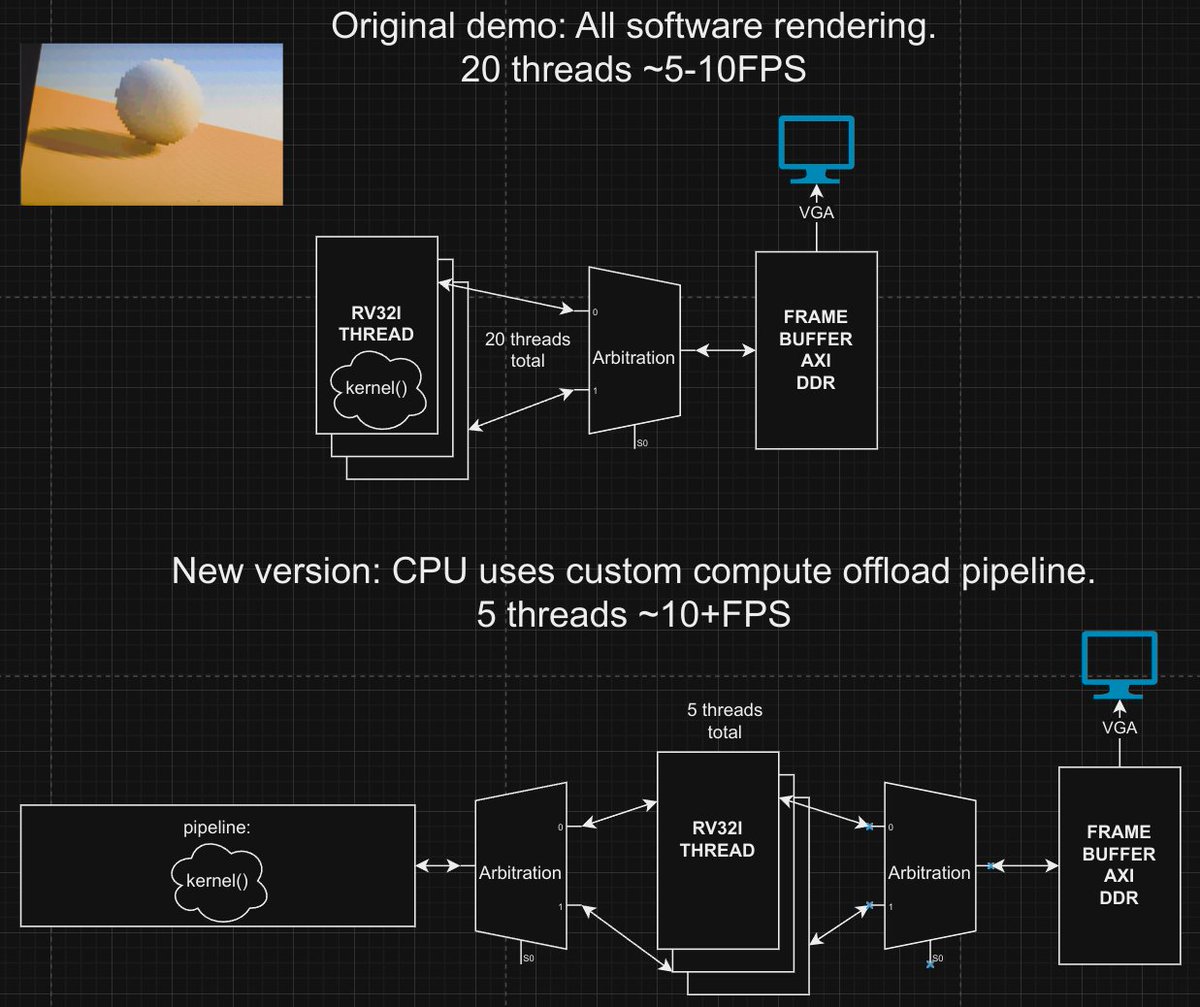

Four RV32I @risc_v cores totaling ~333M IPS do work with a 480p frame buffer 🤓. 20 threads, ~software rendering, but focus isn't on CPU core, next up: experiments with custom accelerator pipelines to offload compute 😏 #PipelineC #FPGA #HDL #RTL #graphics #riscv

1/4 as many RV32I @risc_v cores for same or better performance. Threads share #PipelineC auto pipelined ~15 stage kernel() hardware function to offload shader compute. CPU is now bottleneck for moving data around from RAM to pipeline and back. #FPGA #HDL #RTL #graphics #riscv

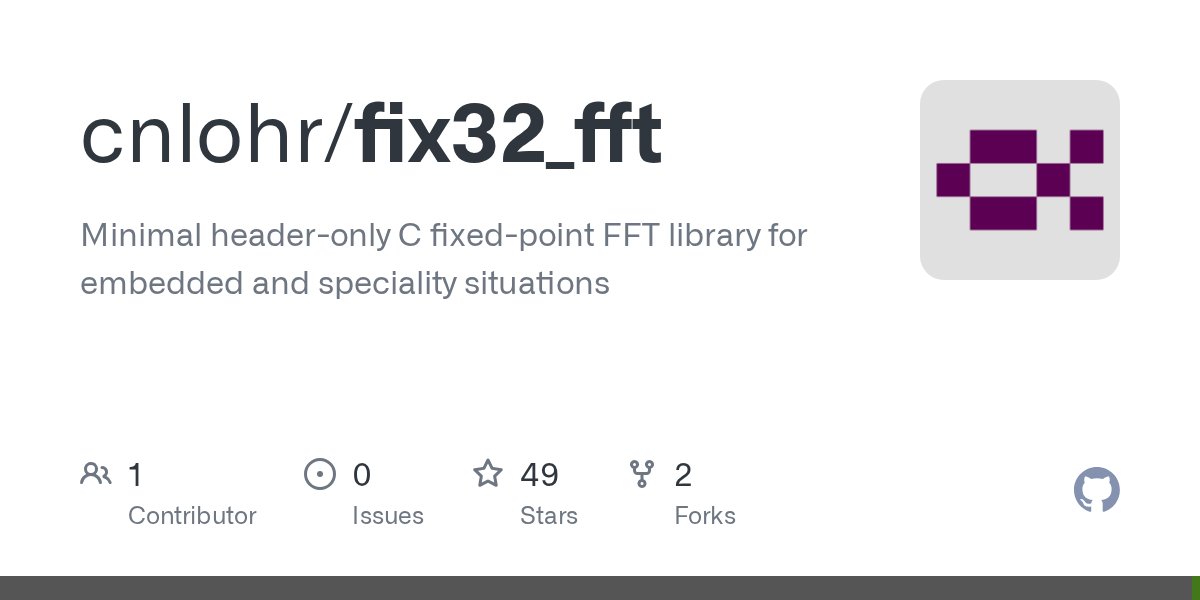

Nice... We did something similar for #PipelineC and ended up doing the FFT in hardware too! @pipelinec_hdl

Want a fast, simple, and small integer FFT implementation geared for 32-bit (ARM + RISC-V) processors? I have largely rewritten one of the more popular fix_fft implementations and got the OK by most recent maintainers to put it under the MIT license. github.com/cnlohr/fix32_f…

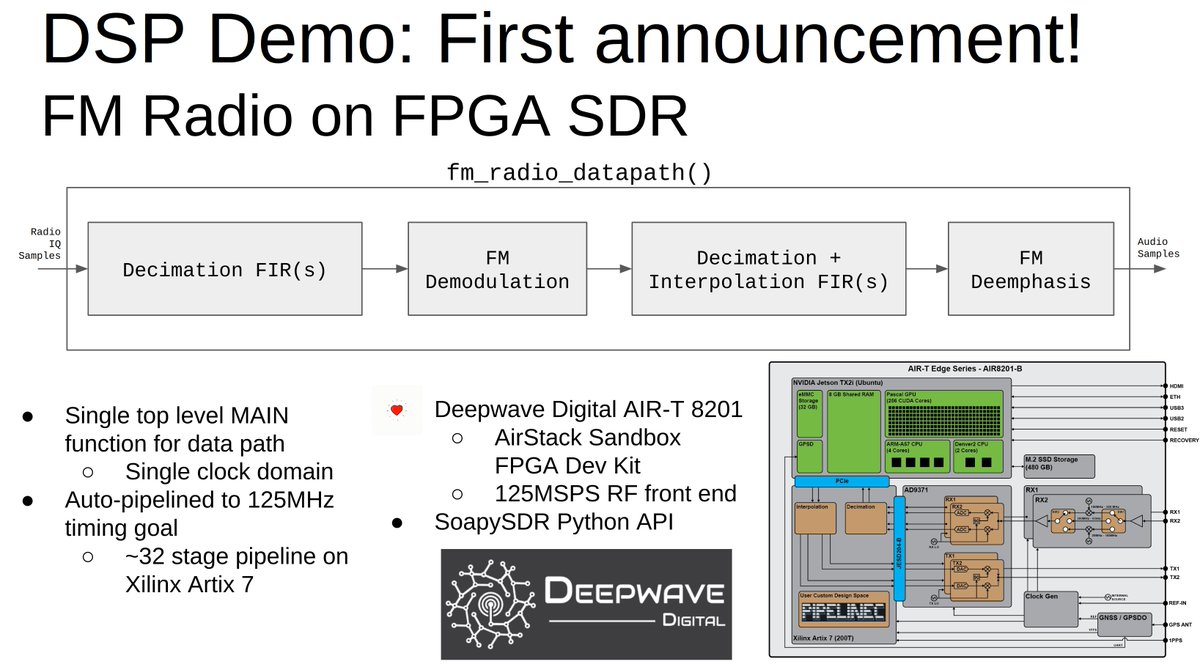

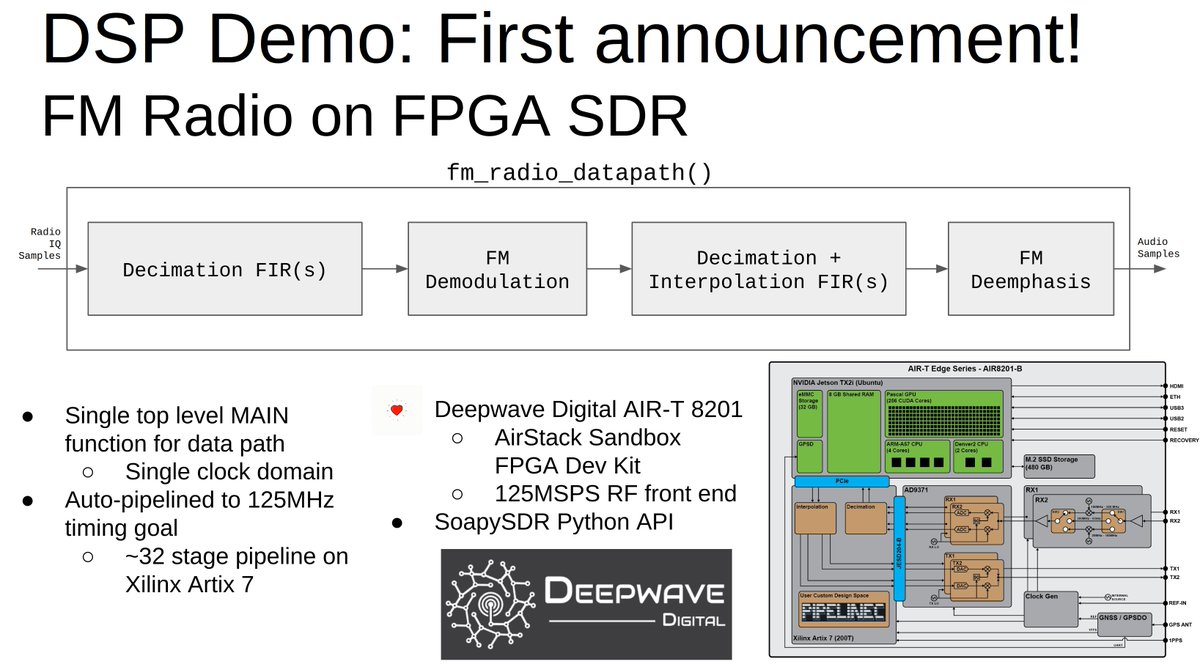

Use #PipelineC to listen to FM #radio with an #FPGA #SDR! Huge thanks to @DutraCGI and @Darkknight512 for making this first version a great learning process. And @deepwavedigital for the fantastic #hardware platform and workplace <3 fosstodon.org/@pipelinec/112… #hdl #hls #asic

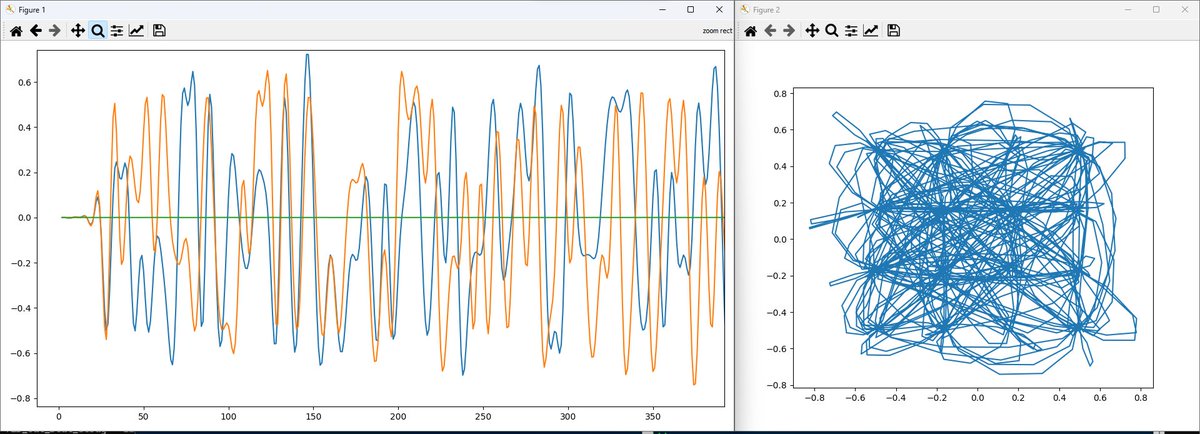

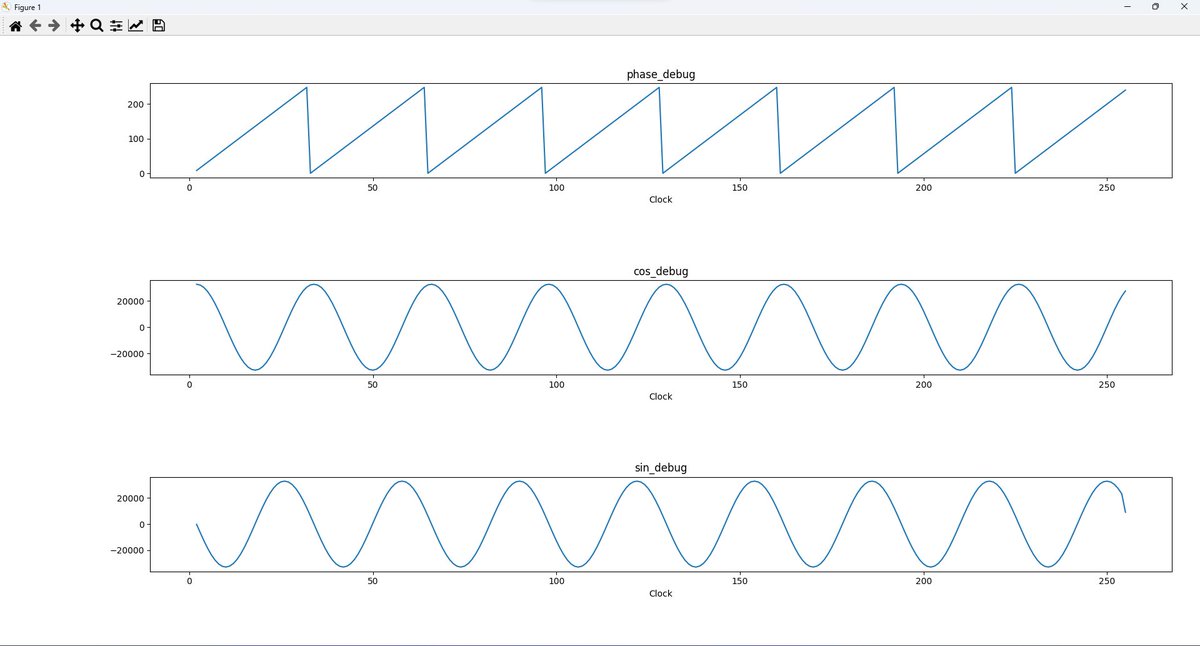

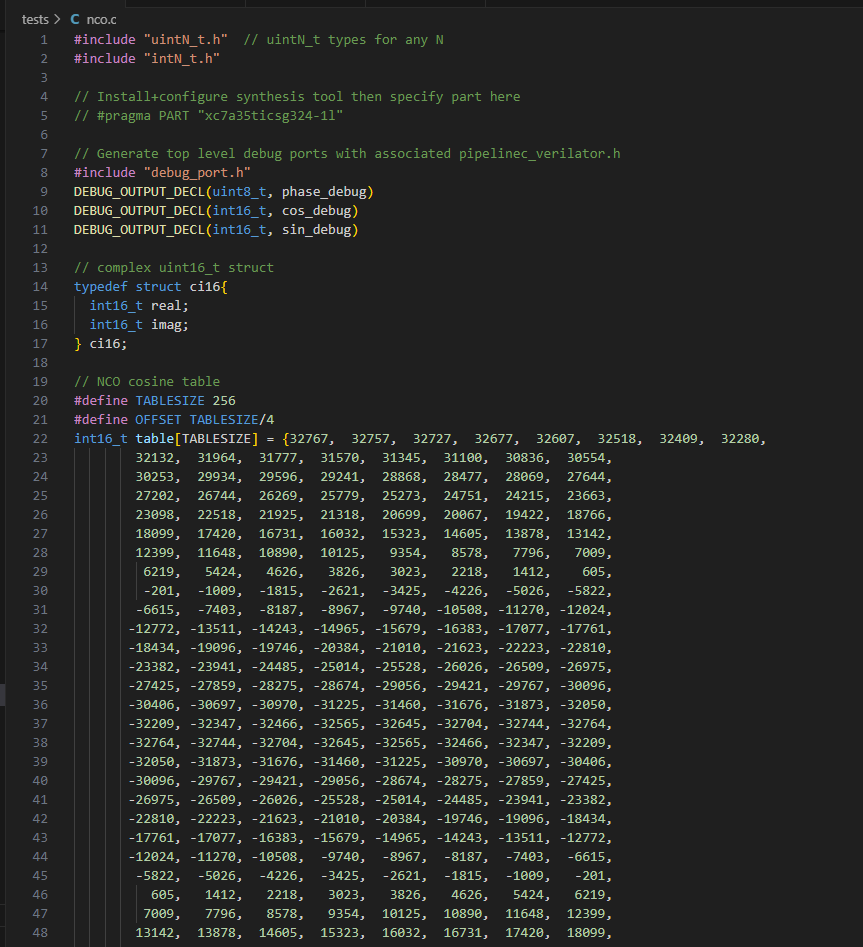

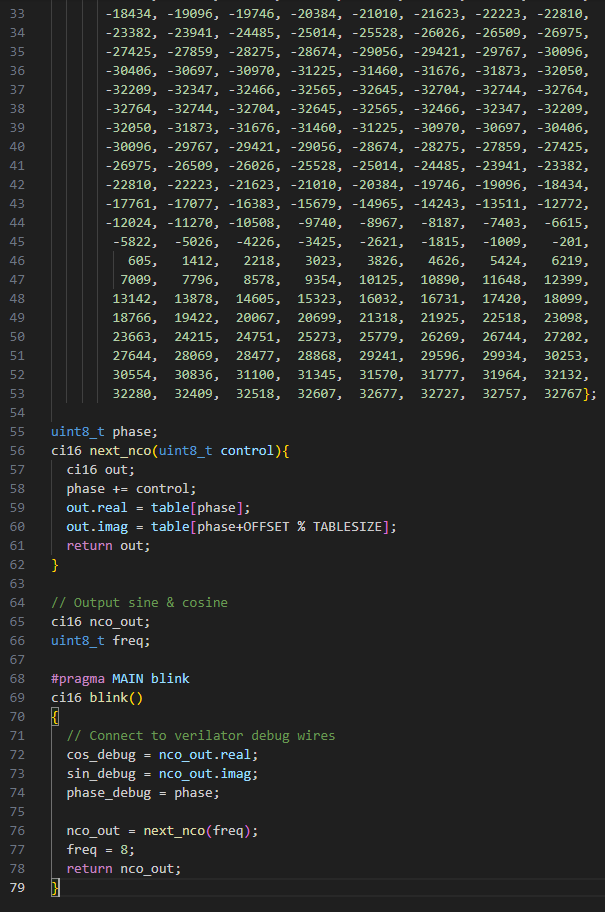

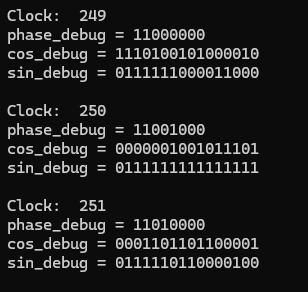

So... I made a blog... The first official post is about the #PipelineC #NCO I was developing last week! @ico_TC paulo-d2000.github.io/en-us/2023/10/… #FPGA #SDR #DSP

#AD Taking Care of Your Pipelines: Why It's Important dynagard.info/taking-care-of… #pipelinec

#QAM16 Modulator made with #PipelineC simulation with #GHDL and cocotb! Raised Cosine filter with 0.35 rollof and 4 samples/symbol ! #fpga #qam #sdr #dsp

So... I've made a little "LoRa" (CSSS) beacon demo with #ULX3S and #PipelineC ! Ramp Nco ("SF6") -> Sine / Cosine NCO's => 2nd Order Delta sigma DAC => digital iq mixer -> output #sdr #fpga #rf #csss #lora #dsp #dac #sigmadelta #alldigitaltx

Testing my PipelineC NCO again... Made one little python script that plots the GHDL outputs... #PipelineC #FPGA #NCO #DSP

#PipelineC Raised Cosine FIR Filter simulation with GDHL + cocotb! QAM modulator comming next... #fpga #ghdl #vhdl #rf #dsp #sdr

Trying to learn this magic tool that ''translates'' C code to FPGA HDL...😳 Simulating the blink example with Verilator #pipelinec #fpga

Following the previous post about the #FPGA #16APSK Modulator made with #PipelineC ... Here are some real world tests using the ULX3S Board! #dsp #sdr #apsk #hdl #ulx3s #dac #deltasigma #rf

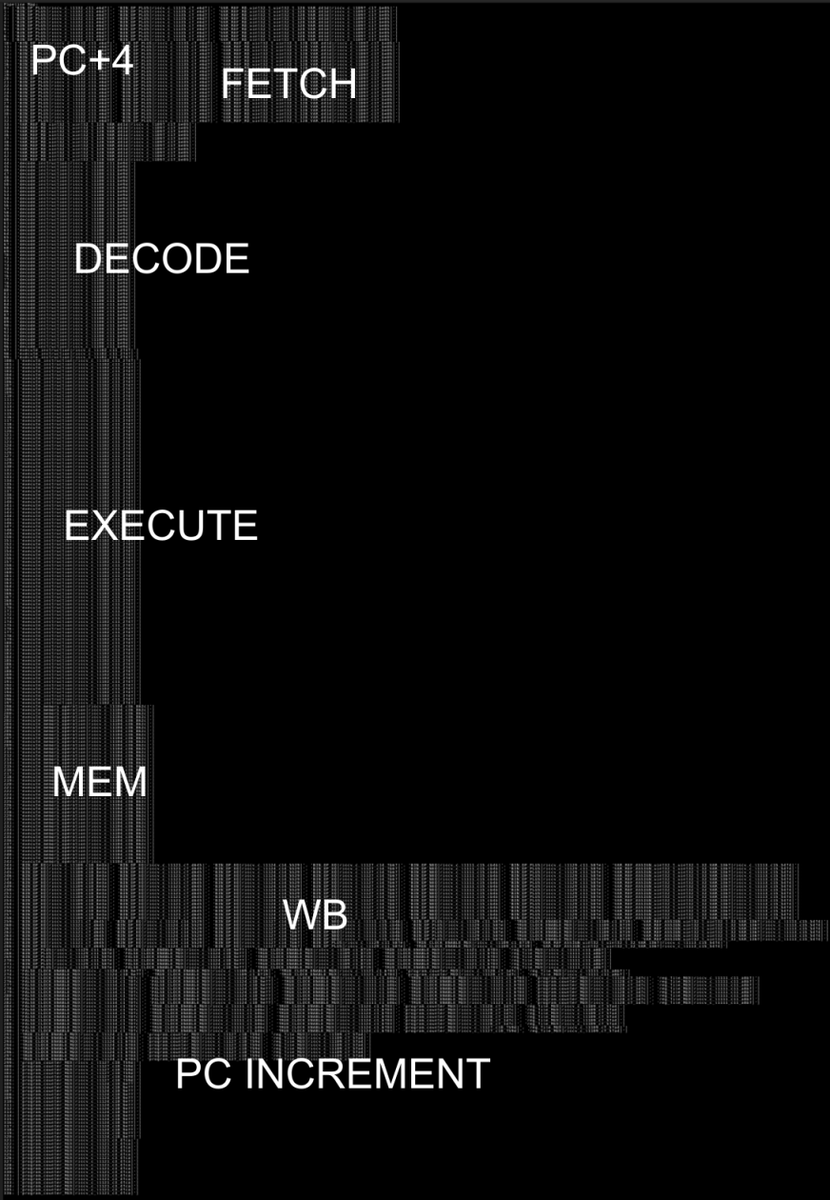

When working on a @risc_v design? Wouldn't it be nice to synthesize your emulator written in C? Heck, make a real RISCV design from that? #FPGA made easy if you can read basic C code. Single cycle cpu in ~1000LOC? (tool output pic) #pipelinec

1/4 as many RV32I @risc_v cores for same or better performance. Threads share #PipelineC auto pipelined ~15 stage kernel() hardware function to offload shader compute. CPU is now bottleneck for moving data around from RAM to pipeline and back. #FPGA #HDL #RTL #graphics #riscv

Use #PipelineC to listen to FM #radio with an #FPGA #SDR! Huge thanks to @DutraCGI and @Darkknight512 for making this first version a great learning process. And @deepwavedigital for the fantastic #hardware platform and workplace <3 fosstodon.org/@pipelinec/112… #hdl #hls #asic

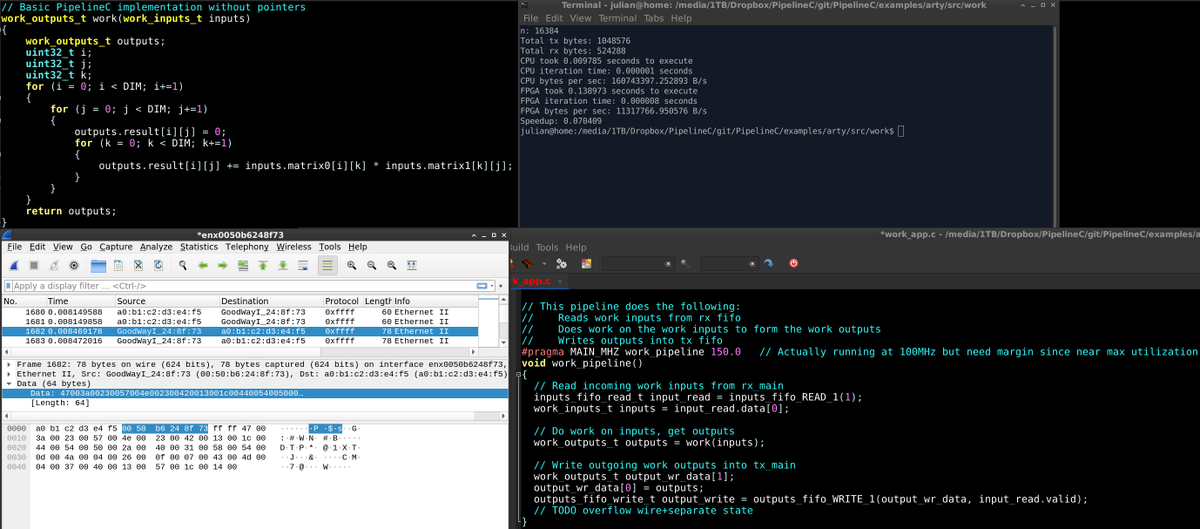

Quick threw together a fun - but ultimately slow - network attached 4x4 int16_t matrix multiplier #fpga perhaps onto a simple NN layer or two next #pipelinec

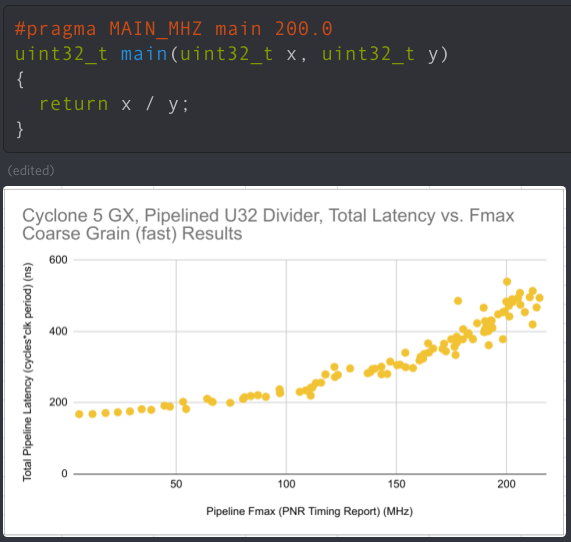

Are you trying to pipeline things on your #FPGA? @IntelFPGA 's devices are supported via Quartus - why pipeline by hand? #PipelineC #hdl #hls

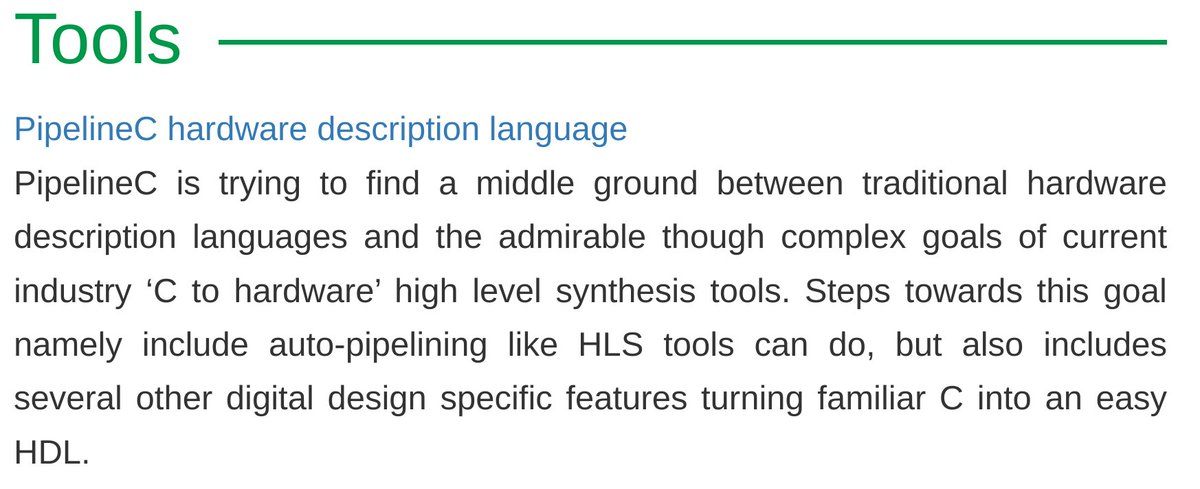

Alot of C and C++ indeed! Why not do your hardware description in a C look too? :) Thanks for the kind words @embedsys . Try out an easier HDL today! #PipelineC #FPGA #ASIC #HDL #FPGAFriday

This week in Embedsys Weekly #87: A complicated question for the Linux kernel maintainers, a lot of C and C++, how to do a 3D Lidar with $100, and more... Happy Reading! embedsysweekly.com/embedded-syste… #embedded #embedsys

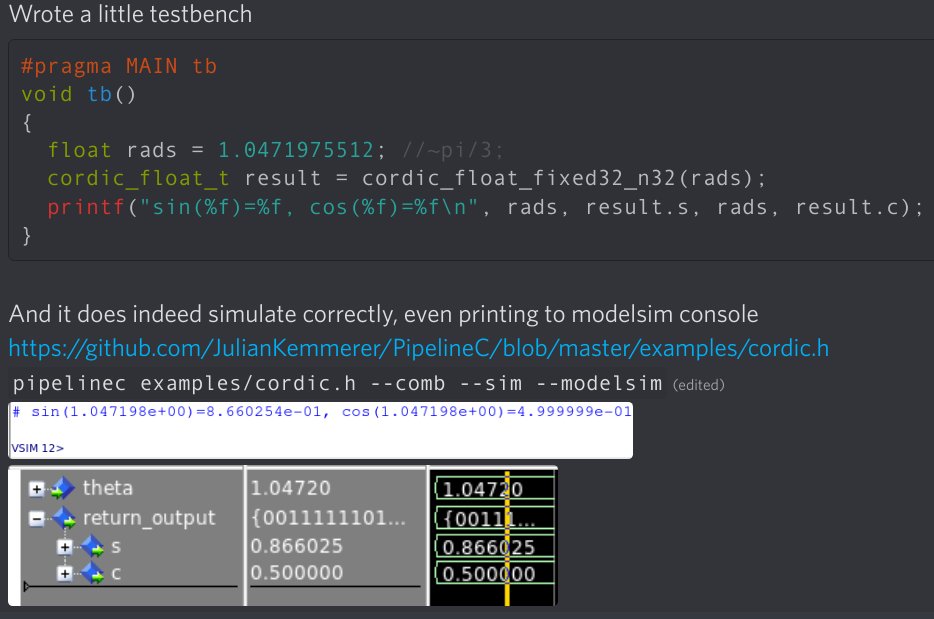

Wanted a quick CORDIC example I could synthesize. So roughly copied the first "simple C source for CORDIC" I could find 😏 github.com/JulianKemmerer… Ease your way from software into hardware description with #PipelineC 🤓

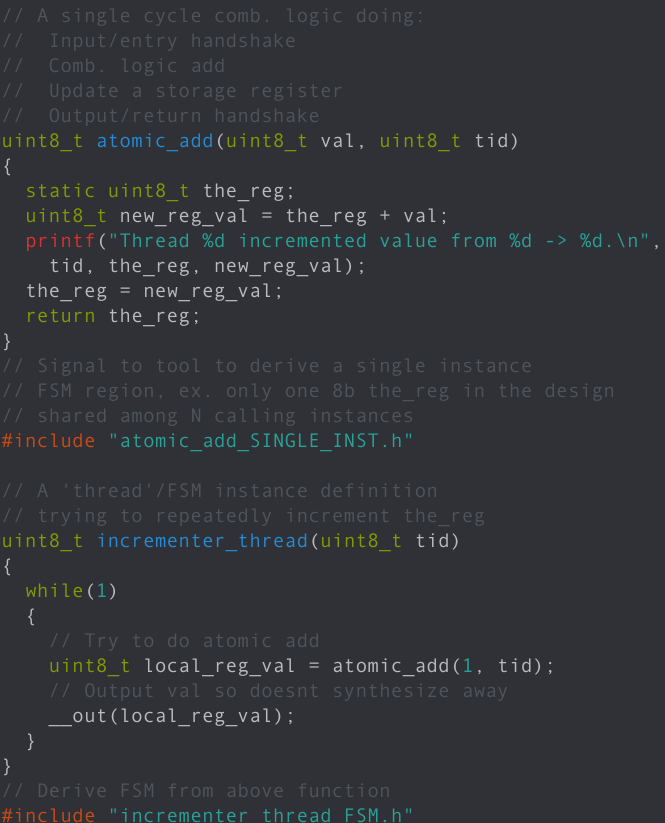

Can your HDL share a single state machines among other state machines? Check out this 'multiple thread FSMs atomically incrementing a register' demo. More announcements and documentation coming soon! (Can try it yourself today though!) #FPGA #hardware #PipelineC

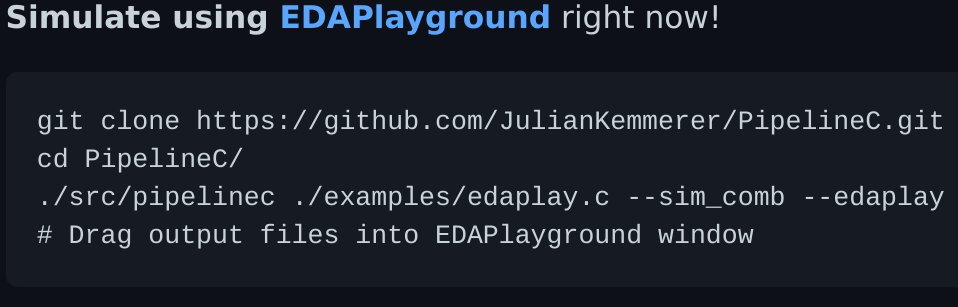

Making it easier to quick start up an @EDAPlayground based simulations. Give this #FPGA #PipelineC fun a try yourself in seconds! edaplayground.com/x/vWLi

Something went wrong.

Something went wrong.

United States Trends

- 1. Rays 13.1K posts

- 2. Shane Baz 2,969 posts

- 3. Tucker 174K posts

- 4. Merry Christmas 175K posts

- 5. Brandon Lowe 2,512 posts

- 6. Kennedy Center 183K posts

- 7. #FanCashDropPromotion 3,363 posts

- 8. Happy Holidays 51K posts

- 9. NextNRG 3,727 posts

- 10. #FursuitFriday 14.6K posts

- 11. Kennesaw State 1,929 posts

- 12. #jonita 41.1K posts

- 13. Mangum 1,489 posts

- 14. Western Michigan 2,099 posts

- 15. Burrows 2,440 posts

- 16. Jake Paul 30.5K posts

- 17. Bowen Yang 2,238 posts

- 18. Ben Shapiro 96.9K posts

- 19. Astros 3,513 posts

- 20. Bodine 2,054 posts