#verilator search results

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

Yeah fuck a little bit #riscv linux in my #verilator #kianRiscV....learning learning assembler linux souce code....💢💥❤️🤣👍👍👍👍👍😾

Verilator is fastzzz found this resource to get started itsembedded.com/dhd/verilator_… #opensourcehardware #verilator

Hello Bruno, my friend. Couldn't resist trying out KianV Stealth RV32I, 5-staged pipeline at 90MHz. :) @samsoniuk code adjustments takes some seconds, try it on #darkriscv #verilator #ulx3s #fpga #donut

Fancy graphics output of Dan's @zipcpu simulated fftdemo running with #verilator github.com/ZipCPU/fftdemo (Environment is Verilator 5 on virtual Ubuntu 22.04, WSL2, Windows 11)

We improved #Verilator's hierarchical mode in terms of verilation and compilation times, resource usage and scalability to enable faster-turnaround ASIC design flows for complex designs. See how we can extend Verilator for your use case: antmicro.com/blog/2025/05/i… @CHIPSAlliance

Join us for the 3rd Gdansk #OpenSource Meetup, Thu 11.05, 6PM. Learn about effective chip design simulation w/ #Verilator. 2nd talk will overview novel Deep Neural Network applications that are in the open source ecosystem for your use. meetup.com/gdansk-open-so… #DNN #SystemVerilog

Read about the latest speed and memory usage optimizations we added to #Verilator and the ongoing effort to enable multithreaded model generation. More about Verilator in our talk at #ORConf this weekend: antmicro.com/blog/2023/09/a… #opensource @FossiFoundation @CHIPSAlliance

Co-simulate CPUs from RTL in #Verilator with @renodeio to run unmodified software in a deterministic simulation. Combine precise CPU models w/ reusable #opensource I/O components to build complete systems simulating e.g. #OpenTitan SoC w/ Ibex @risc_v CPU: antmicro.com/blog/2023/01/c…

At @LatchUpConf today we presented our work towards full #opensource #UVM support. Learn how we added constrained randomization in #Verilator for cloud scaling of production-grade #ASIC verification workloads: antmicro.com/blog/2024/03/i… @FossiFoundation @CHIPSAlliance @google…

Has anyone heard of any distributed uses of #verilator i.e. manually splitting a single hardware design over multiple computers (VMs) and doing a distributed SystemVerilog simulation run that actually results in a speedup over a single node simulation? Thank you kindly.

With support for Direct Programming Interface in @renodeio, we introduced major improvements to pre-silicon development & co-simulation with industry-standard simulators like #Verilator or @siemenssoftware Questa for #ASIC and #FPGA design: antmicro.com/blog/2023/09/d… @MicrochipTech

Why with every new update of #VSCode, does the #Verilator linter stop working?

#verilator has a "--threads n" command-line flag to itself split the simulation into n threads to exploit running on a multiprocessor. Website claims some dramatic speedups. (I've no personal experience with using this.)

@Antmicro introduced global assertion control in runtime to #Verilator. Find out how it can simplify your verification test suites and read about future considerations for more granular control: chipsalliance.org/news/initial-a… #ASIC #FPGA

During our @LatchUpConf talk we discussed recent developments in #opensource RTL verification w/ #Verilator, including constrained randomization, #UVM support, coroutines and integration with Astsee: youtube.com/watch?v=5lQGxM… @FossiFoundation @CHIPSAlliance @google @westerndigital

Join @antmicro's talk on enabling #UVM testbenches in #Verilator during the CHIPS Technology Update. Learn about the updates & future plans of the project including compilation optimization & constrained randomization: sched.co/1TUoX @linuxfoundation

We improved #Verilator's hierarchical mode in terms of verilation and compilation times, resource usage and scalability to enable faster-turnaround ASIC design flows for complex designs. See how we can extend Verilator for your use case: antmicro.com/blog/2025/05/i… @CHIPSAlliance

Why with every new update of #VSCode, does the #Verilator linter stop working?

See how we extended @renodeio with new complex DPI-based HDL co-simulation scenarios and find out how we can help you accelerate FPGA & ASIC design, development and testing with a flexible, deterministic co-simulation environment antmicro.com/blog/2025/04/c… @MicrochipTech #Verilator

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

From 10 hrs to 37 mins: discover how our optimization of #LLVM made it possible to compile verilated C++ models 20x faster. antmicro.com/blog/2024/11/o… @CHIPSAlliance @llvmorg #Verilator

Find out how we brought #opensource AXI-based #UVM system verification to #Verilator as part of our work on the #Caliptra 2.0 specification. We also included new tests in our CI test suite for checking verification features: antmicro.com/blog/2024/09/o… @amd @google @microsoft @nvidia…

Introducing sv-bugpoint, an #opensource tool for identifying minimal bug-inducing #SystemVerilog code fragments that can be then shared externally to improve debugging in #Verilator, @OpenROAD_EDA & any other SV tool: antmicro.com/blog/2024/09/s… @CHIPSAlliance @risc_v @GoogleOSS #UVM

antmicro.com

sv-bugpoint: pinpoint minimal bug-inducing SystemVerilog code subsets to improve debugging in...

sv-bugpoint: pinpoint minimal bug-inducing SystemVerilog code subsets to improve debugging in...

Working towards #Caliptra 2.0, we added User mode support to the @risc_v VeeR EL2 core. Read about the implementation, PMP support & the testing infrastructure w/ #Verilator, RISCV-DV, @talkingtock & @renodeio antmicro.com/blog/2024/09/u… @CHIPSAlliance @Google @AMD @Microsoft @nvidia

Verilator is fastzzz found this resource to get started itsembedded.com/dhd/verilator_… #opensourcehardware #verilator

Learn how we used SMT solvers and #SystemVerilog to SMT-LIB2 conversion to implement constrained randomization in #Verilator on the road to fully #opensource #ASIC verification with #UVM: antmicro.com/blog/2024/08/c… @CHIPSAlliance @google @westerndigital @risc_v

antmicro.com

Constrained randomization in Verilator: SystemVerilog constraint to SMT-LIB2 conversion

Constrained randomization in Verilator: SystemVerilog constraint to SMT-LIB2 conversion

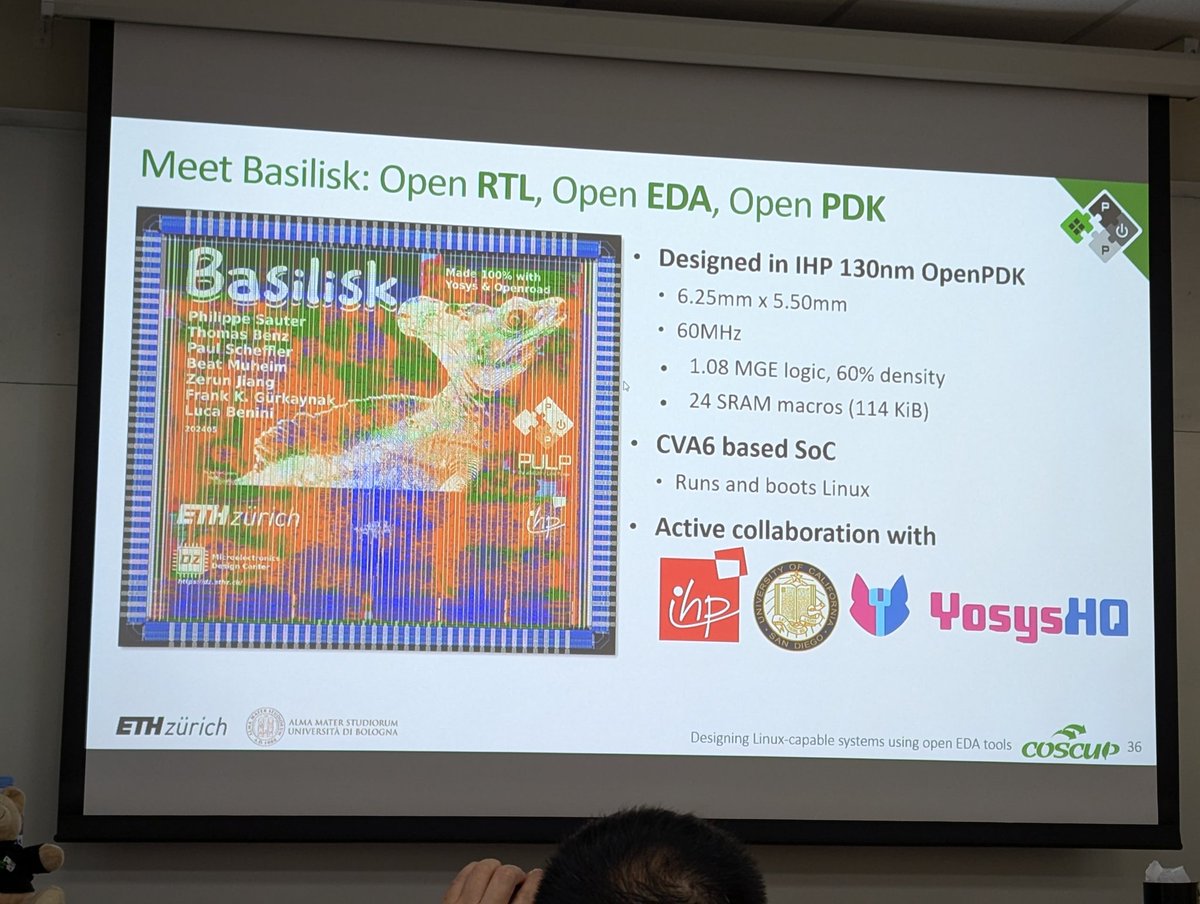

Now Philippe and Charlie from @pulp_platform talking about open tooling like #Yosys, #OpenLane , #Verilator and of course open #PDKs here at @coscup:) Happy to see @openhwgroup #CVA6 INSIDE #OpenHW #COSCUP #LINUX

Introducing global assertion control in runtime to #Verilator. Find out how it can simplify your verification test suites and read about future considerations for more granular control: antmicro.com/blog/2024/06/i… @CHIPSAlliance #ASIC #FPGA

antmicro.com

Initial assertion control support in Verilator

Initial assertion control support in Verilator

#verilator has a "--threads n" command-line flag to itself split the simulation into n threads to exploit running on a multiprocessor. Website claims some dramatic speedups. (I've no personal experience with using this.)

Has anyone heard of any distributed uses of #verilator i.e. manually splitting a single hardware design over multiple computers (VMs) and doing a distributed SystemVerilog simulation run that actually results in a speedup over a single node simulation? Thank you kindly.

During our @LatchUpConf talk we discussed recent developments in #opensource RTL verification w/ #Verilator, including constrained randomization, #UVM support, coroutines and integration with Astsee: youtube.com/watch?v=5lQGxM… @FossiFoundation @CHIPSAlliance @google @westerndigital

Exciting news for developers: Verilator, an open-source SystemVerilog simulator and lint system, has been released, offering a valuable resource for digital design and verification. #Verilator #SystemVerilog #OpenSource ift.tt/eiDx8rm

At @LatchUpConf today we presented our work towards full #opensource #UVM support. Learn how we added constrained randomization in #Verilator for cloud scaling of production-grade #ASIC verification workloads: antmicro.com/blog/2024/03/i… @FossiFoundation @CHIPSAlliance @google…

#Verilator noob at work. It took me an embarrassingly long time from realizing I had to implement simulation/test benches to actually getting a waveform visualization. Wasted a ton of time trying to create benches in modelsim (garbage tool), then just dumping verilator debugs.

Open-source project are arriving to the #FPGA world. We already have great examples like #Yosys or #Verilator. In this week article we are going to see another interesting project, Open Logic. Check it out! controlpaths.com/2025/02/02/the…

Introducing github.com/antonblanchard… - a generator of fast and efficient standard cell adders, multipliers and multiply-adders. Written in Amaranth HDL, formally verified with #Yosys. #Verilator verification too With @OpenROAD_EDA + ASAP7 7nm a 32bit 3 cycle multiplier hits 2.7GHz

Feels good when the CPU you built from scratch is running instructions! #verilog #verilator #gtkwave #v30mz

Wilson Snyder Officially Launches Verilator 4.0 at ORConf 2018. abopen.com/news/wilson-sn… #Verilator #FOSSi #FOSS #Verilog #HDL

The @renodeio 1.9 release introduces extended co-simulation support with #Verilator. See the @ZephyrIoT on #LiteX/VexRiscv @RISC_V demo with a verilated UART connected to Renode via our brand new Wishbone support, with interrupt-driven input: github.com/renode/renode/…

Multithreaded simulation orders of magnitude slower than single-threaded stackoverflow.com/questions/6733… #multithreading #verilator #cpp #performance

.@antmicro The @renodeio 1.9 release introduces extended co-simulation support with #Verilator. See the @ZephyrIoT on #LiteX/VexRiscv @RISC_V demo with a verilated UART connected to Renode via brand new Wishbone support, with interrupt-driven input: bddy.me/2QMQCAW

In collaboration with @westerndigital we’ve reached another important milestone towards #opensource UVM design verification with dynamic scheduling in #Verilator that enables converting non-synthesizable code. antmicro.com/blog/2021/05/d… @CHIPSAlliance

Fresh blog note in @antmicro's Technology Showcase on new @renodeio co-simulation capabilities with #verilator - combining Renode's openness, flexibility and debugging powers with the precision of HDL simulation: antmicro.com/blog/2019/09/r…

Join @antmicro discussing “Open Source Tools: #cocotb and #Verilator support” during the inaugural @CHIPSAlliance Workshop next week at Google’s Sunnyvale campus with @EsperantoTech, @Google, @SiFive & @WesternDigital @linuxfoundation: events.linuxfoundation.org/events/chips-a…

With the latest improvements to the dynamic scheduler in #Verilator we've developed a fully usable, fast implementation based on #coroutines, bringing us one step closer to #opensource UVM support in chip design: antmicro.com/blog/2021/12/c… @CHIPSAlliance @westerndigital

Co-simulate your #Verilog IP with @renodeio and #verilator - plug in a peripheral under development to an entire @RISC_V system running @ZephyrIoT and test a real-world use case. Read the @antmicro blog here: bddy.me/2VQS0DX #RTOS #ZephyrIoT

#SweRV is a family of production-grade @RISC_V cores from @westerndigital under the governance of @CHIPSAlliance, with a range of MCU options. Read about our work with #opensource tools for SweRV: antmicro.com/blog/2020/07/s… #Verilator @renodeio #FuseSoC #LiteX @symbiflow

This time we’re enabling advanced HW/SW #cosimulation with Antmicro’s @renodeio and #Verilator for the popular #FPGA #Zynq platform by @XilinxInc. Read more in our latest blog: antmicro.com/blog/2021/09/c… @CHIPSAlliance @mithro

Something went wrong.

Something went wrong.

United States Trends

- 1. Texas A&M 15.7K posts

- 2. South Carolina 15.2K posts

- 3. Marcel Reed 2,866 posts

- 4. Aggies 4,430 posts

- 5. College Station 2,283 posts

- 6. Nyck Harbor 1,767 posts

- 7. Elko 2,686 posts

- 8. Semaj Morgan N/A

- 9. Jeremiyah Love 3,583 posts

- 10. Malachi Fields 1,715 posts

- 11. Mike Shula N/A

- 12. Sellers 9,991 posts

- 13. Shane Beamer N/A

- 14. TAMU 5,953 posts

- 15. Michigan 40.8K posts

- 16. Dylan Stewart N/A

- 17. Northwestern 4,526 posts

- 18. #iufb 1,477 posts

- 19. #GoIrish 3,247 posts

- 20. #GoBlue 2,301 posts