#gpuprogramming نتائج البحث

PROGRAM YOUR GPU youtube.com/playlist?list=… #gpu #gpuprogramming #nvidia #intel #amd #graphics #computergraphics #dataviz #simulation #cudaeducation

PROGRAM YOUR GPU youtube.com/playlist?list=… #gpu #gpuprogramming #nvidia #intel #amd #graphics #computergraphics #dataviz #simulation #cudaeducation

NSIGHT GRAPHICS TUTORIAL: youtu.be/LtretfoL2tc | Vulkan, OpenGL, Direct 3D profiling and debugging | #graphicsprogramming #gpuprogramming #gpgpu #howtoprogram #howtocode #computerprogramming #howtowriteaprogram #siliconvalley #cudaeducation

youtube.com

YouTube

Nsight Graphics Tutorial | Cuda Education

@nvidia GPU bootcamp in the Claustro of @URosario. @HPCCol growing stronger. #HPC #GPUProgramming #OpenACC

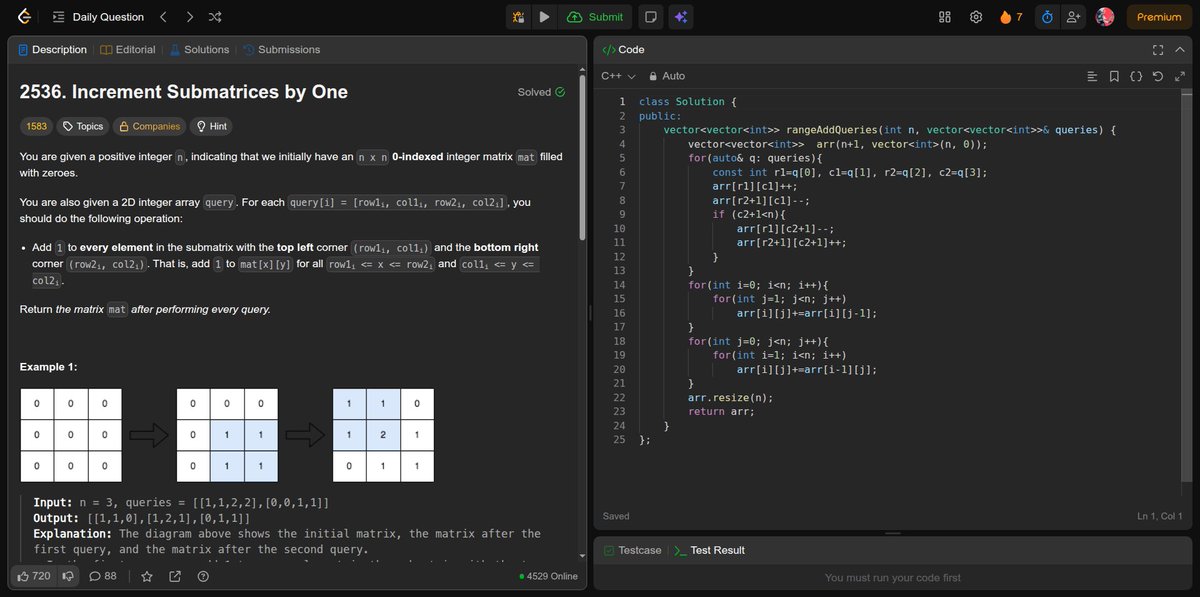

Day 5 of GPU Programming -matrix transpose. -matrix prefix sum leetcode. #100DaysOfGPU #CUDA #GPUProgramming #ParallelComputing #AI #DeepLearning #100DaysOfCode #MachineLearning #NVIDIA #CodingJourney

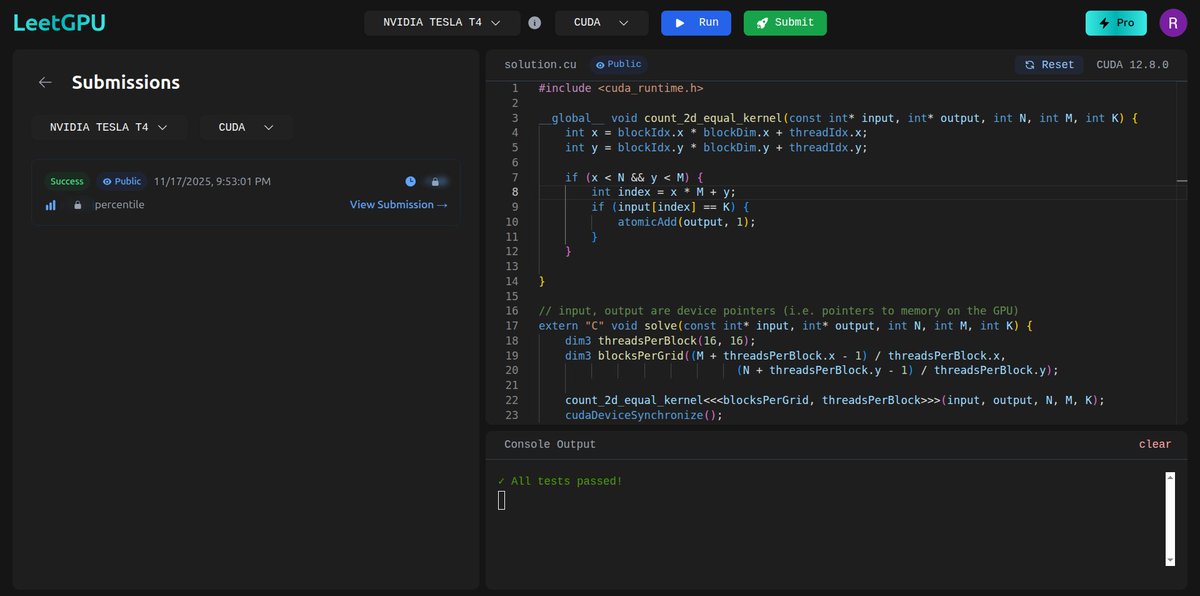

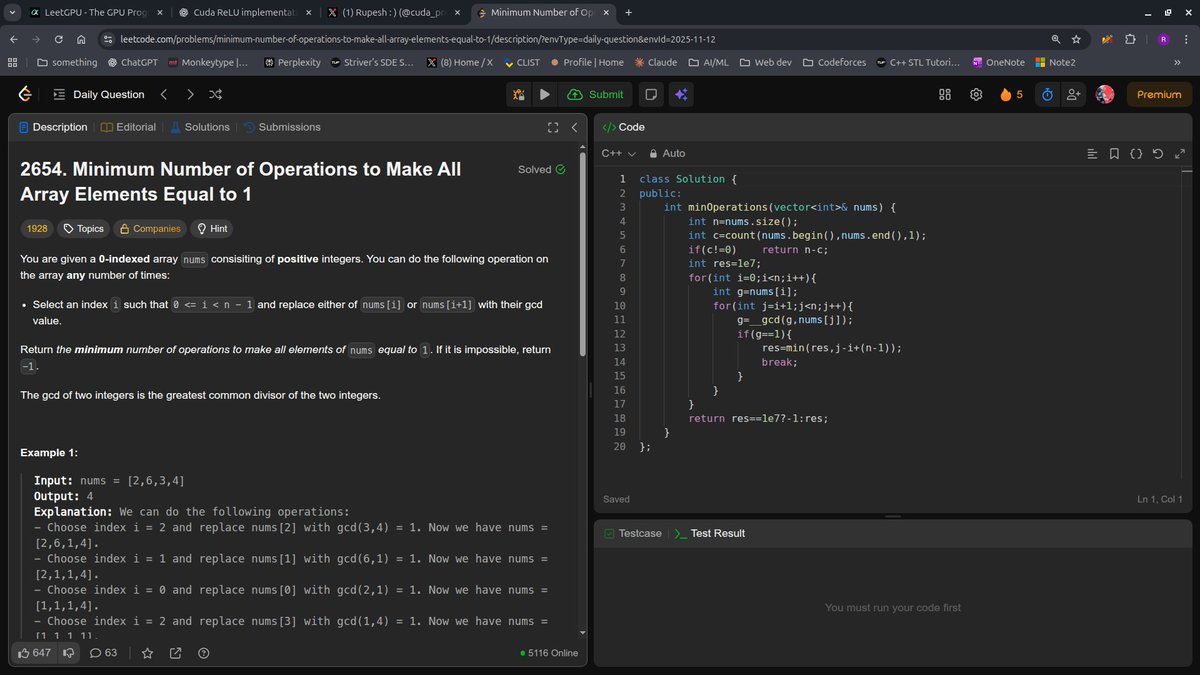

Day 8 of GPU Programming -Count 2D Array Element -todays potd easy peasy again. #100DaysOfGPU #CUDA #GPUProgramming #ParallelComputing #AI #DeepLearning #100DaysOfCode #MachineLearning #NVIDIA #CodingJourney

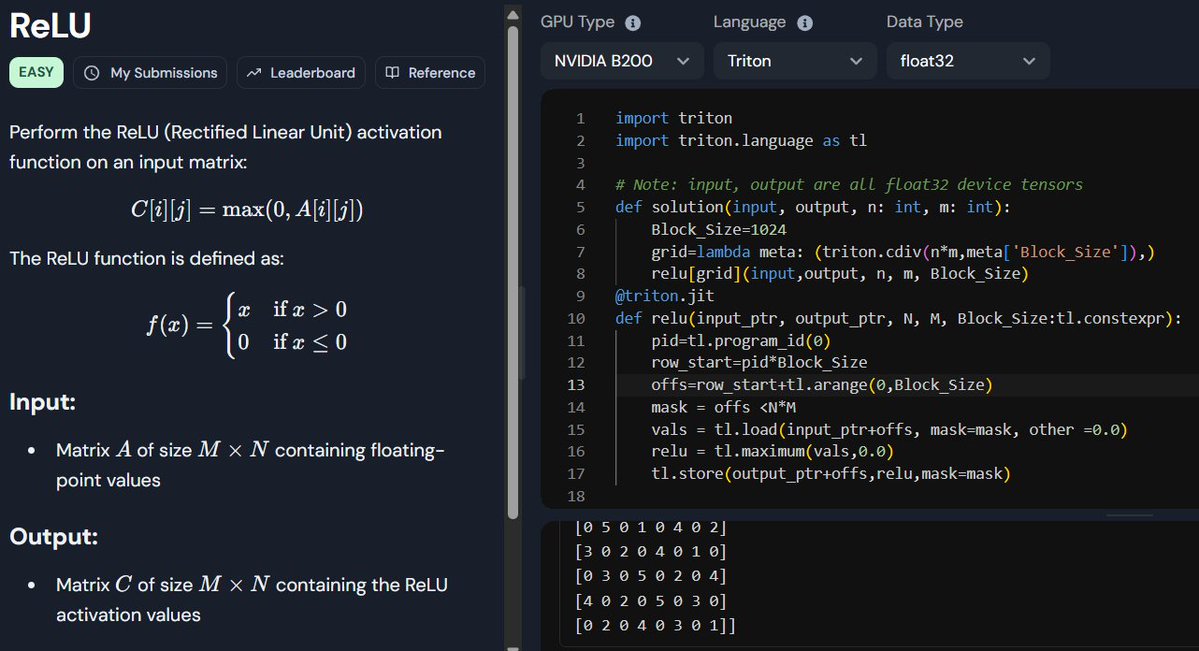

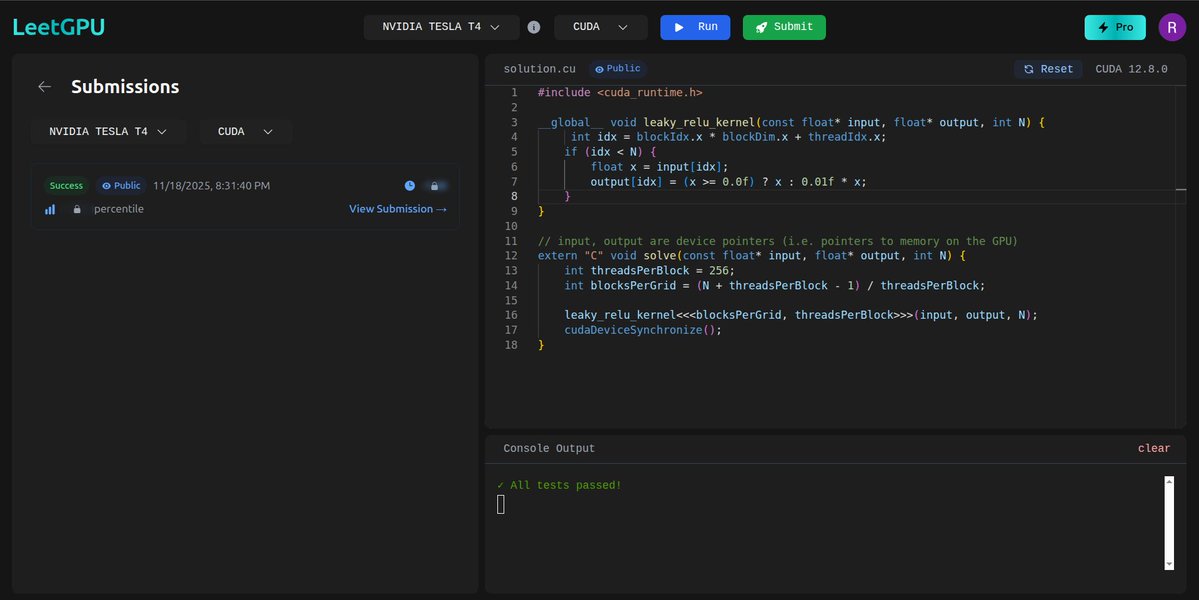

Day 3 of GPU Programming -implemented ReLU activation for 1D array -Did potd leetcod -explored how GPUs handle element-wise operations in parallel #100DaysOfGPU #CUDA #GPUProgramming #ParallelComputing #AI #DeepLearning #100DaysOfCode #MachineLearning #NVIDIA #CodingJourney

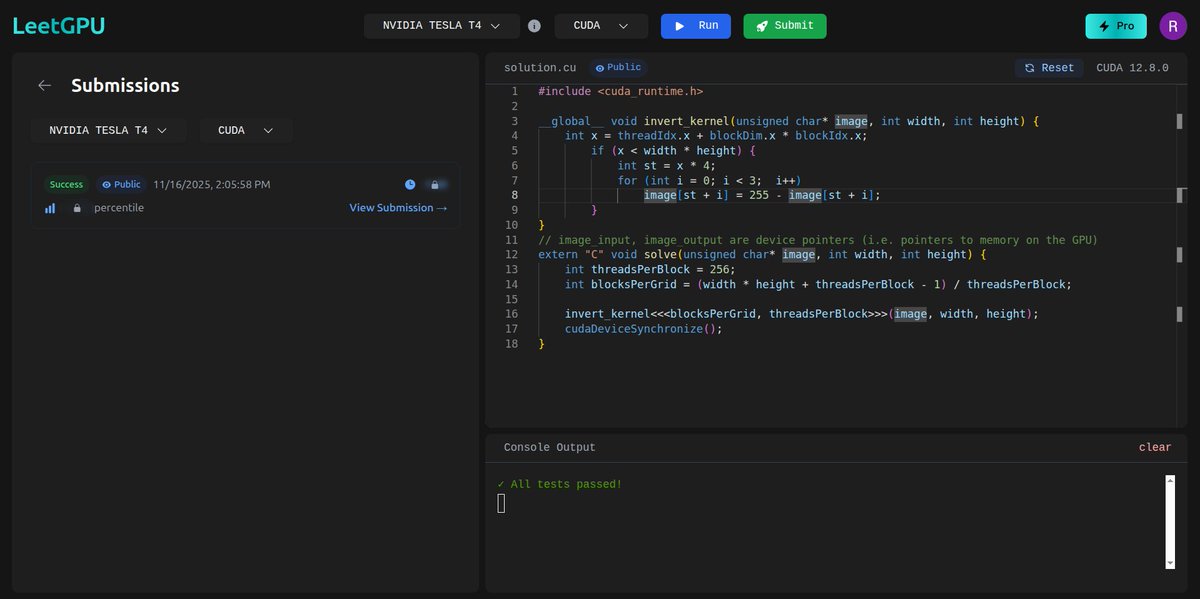

Day 7 of GPU Programming -color inversion. -todays potd easy peasy. #100DaysOfGPU #CUDA #GPUProgramming #ParallelComputing #AI #DeepLearning #100DaysOfCode #MachineLearning #NVIDIA #CodingJourney

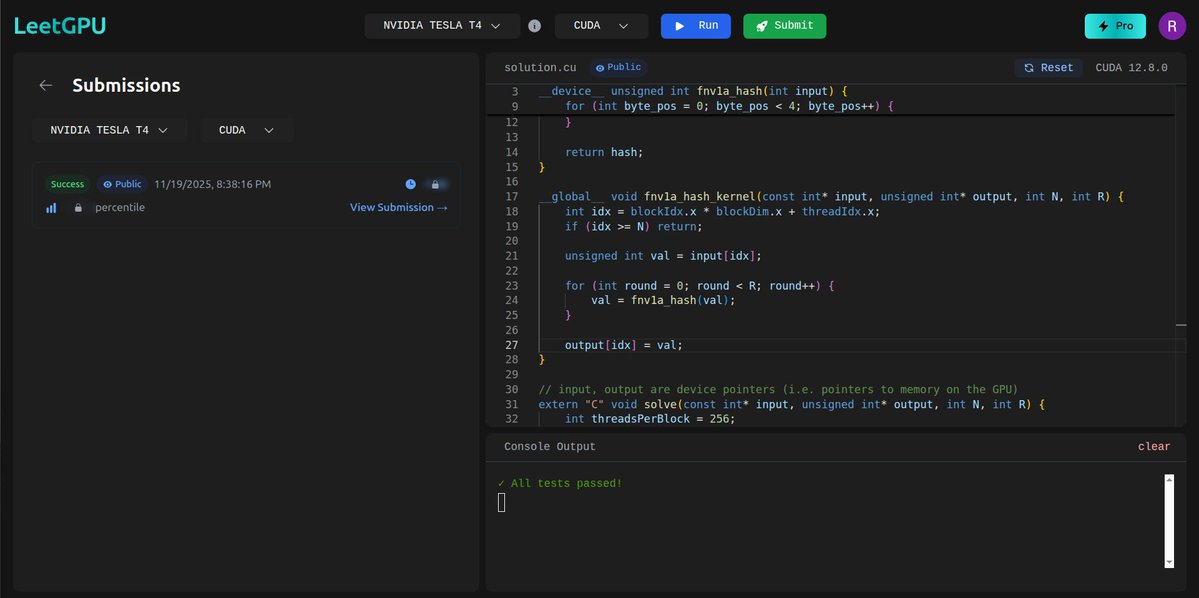

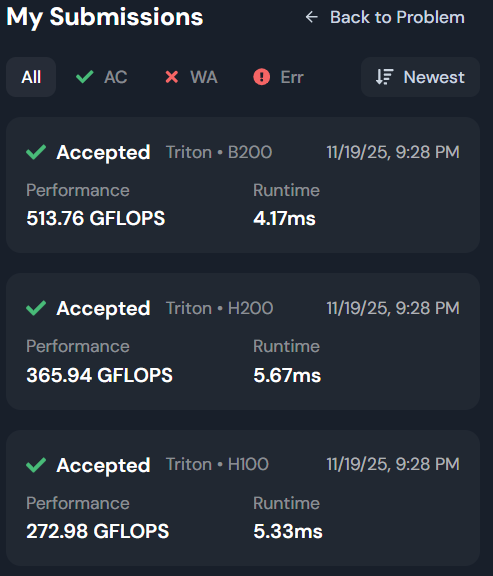

Day 10 of GPU Programming - Rainbow Table - 4th consecutive easy problem on LeetCode #100DaysOfGPU #CUDA #GPUProgramming #ParallelComputing #AI #DeepLearning #100DaysOfCode #MachineLearning #NVIDIA #CodingJourney pic.x.com/FYOUlLsQy3

Compilation errors when using OpenACC with g++ 10 stackoverflow.com/questions/6542… #openacc #gpuprogramming #g++ #compilererrors #cpp

Day 3 of GPU programming At this rate I'll be writing custom inference kernels for AI by next month. The gap between PyTorch abstractions and bare metal isn't as wide as it seemed. #CUDA #GPUProgramming #MachineLearning

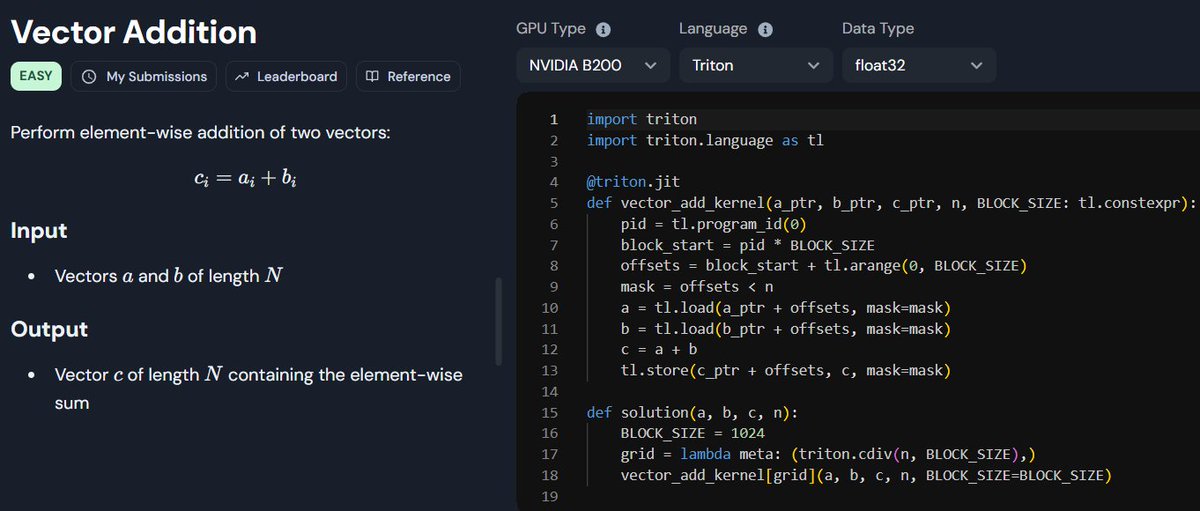

Day 2 of GPU programming Never knew addition needs so much code 😂 Starting to get the hang of program_id. Used Gemini 3.0 to generate pseudocode since I'm new to GPU programming and didn't want full code. Lets hope this momentum continues

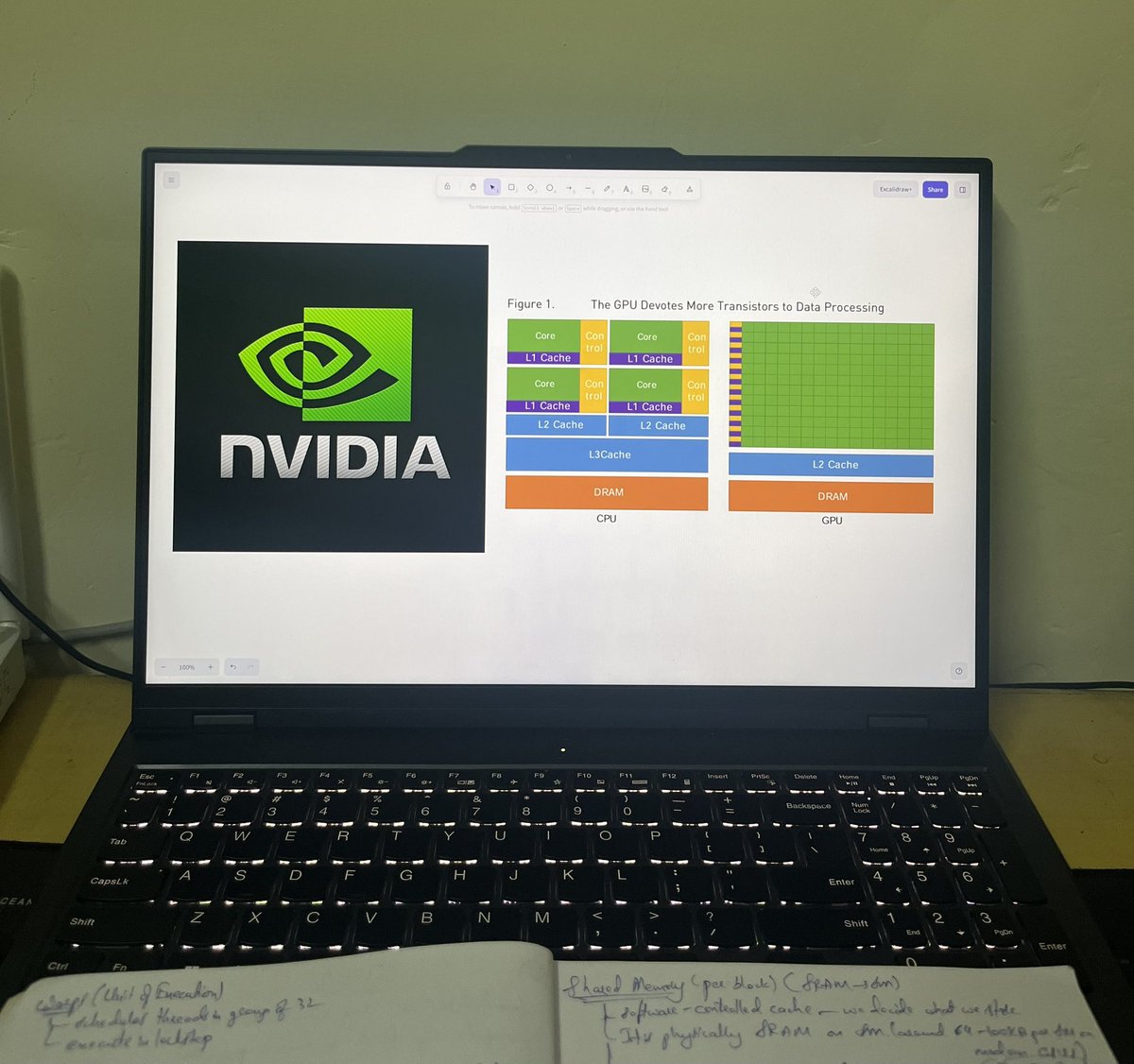

Day 2 of #GPUProgramming: >read an article about shared memory >learnt about registers……..Global memory >almost blacked out from elaboration of L1 & L2 iykyk >”repetition”to digest what I just learnt for about 900k milliseconds

"Need better CUDA textbooks. 'Programming Massively Parallel Processors' is a good intro. I've created C/CUDA C implementations for first 3 chapters. Check book & my GitHub repo for details. #CUDA #GPUprogramming"

Day 6 of GPU Programming -matrix addition. -todays potd was on harder side. #100DaysOfGPU #CUDA #GPUProgramming #ParallelComputing #AI #DeepLearning #100DaysOfCode #MachineLearning #NVIDIA #CodingJourney pic.x.com/9qrJliv3Fdhttp…

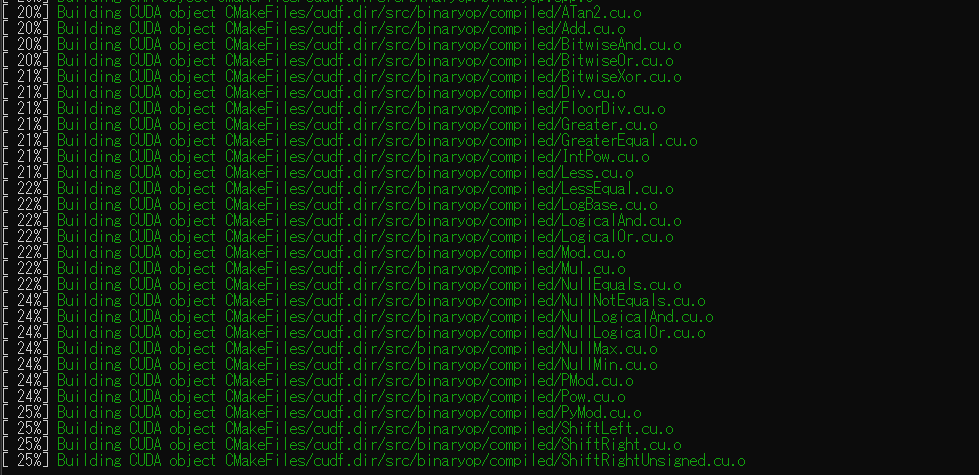

Each common operation is implemented as its own .cu file—modular. intriguing. #CUDA #NVIDIA #GPUProgramming #libcudf

NSIGHT GRAPHICS TUTORIAL: amzn.to/2Qffvpl | Vulkan, OpenGL, Direct 3D profiling and debugging | #graphicsprogramming #gpuprogramming #gpgpu #howtoprogram #howtocode #computerprogramming #howtowriteaprogram #siliconvalley #nsightgraphicstutorial #videowalkthrough

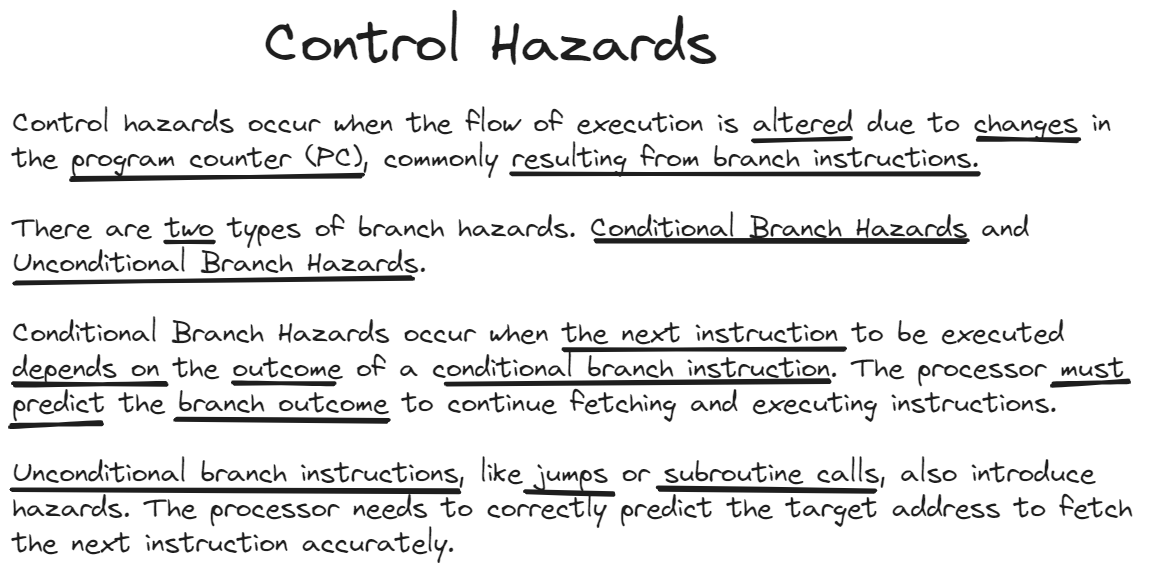

#GPUProgramming - Day 07: 🔧 #CPU Hazards 101 🚧: Ever heard of #Register Renaming & Out-of-Order Execution? They tackle structural hazards, ensuring smooth sailing for instructions. Watch out for Data Hazards (#RAW, #WAR, #WAW) in #MIPS, but fear not! #COA #LearnInPublic

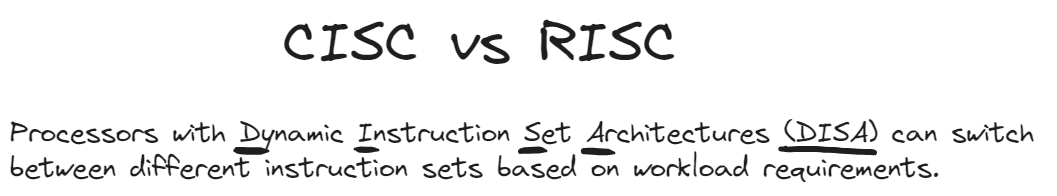

#GPUProgramming - Day 02: 🔄 Exploring CPU architectures! #RISC, like #ARM & #Power, opts for efficiency with many registers. #CISC, exemplified by #Intel 8086, prioritizes simplicity, offering diverse, complex instructions. RISC excels in energy efficiency. #COA #LearnInPublic

#GPUProgramming - Day 03: 🧠 CPUs: Processors adapt with DISA. #CPU's core duo - Control Unit & Datapath. Datapath: Registers, ALU, Buses, Multiplexers – a data symphony! 🔄 Follow the Instruction Execution Cycle: Fetch ➡️Decode➡️Execute➡️Store➡️ Update PC. 🕹️ #LearnInPublic

Day 9 of GPU Programming -Leaky ReLU -leetcode potd easy but hard to implement #100DaysOfGPU #CUDA #GPUProgramming #ParallelComputing #AI #DeepLearning #100DaysOfCode #MachineLearning #NVIDIA #CodingJourney

#GPUProgramming - Day 01: 🚀 Exploring RISC architecture: Simplified, optimized instructions in one clock cycle. 🔄 Bye, CISC complexity! 🏎️ Registers rule, boosting speed. 🤖💡 Compiler-friendly design, slick pipelining for simultaneous processing! 🕵️♂️ #COA #RISC #LearnInPublic

#GPUProgramming - Day 08: 🚀 Explored #computerarchitecture today! 🖥️ Control Hazards tackle branch prediction, #Pentium FDIV bug a classic example. 💡 Memory #Hierarchy is key—#RAM, #cache levels (L1, L2, L3), and storage devices play crucial roles. 🔄🌐 #Memory #LearnInPublic

Something went wrong.

Something went wrong.

United States Trends

- 1. FINALLY DID IT 564K posts

- 2. The BONK 104K posts

- 3. Good Tuesday 31.8K posts

- 4. US Leading Investment Team 6,825 posts

- 5. #Nifty 11.7K posts

- 6. $FULC 10.3K posts

- 7. Jalen 78.7K posts

- 8. Eagles 120K posts

- 9. #tuesdayvibe 1,715 posts

- 10. #BAZAARWomenofTheYearXFreen 387K posts

- 11. #TuesdayFeeling 1,045 posts

- 12. Israel and Judah 1,742 posts

- 13. Chargers 88.3K posts

- 14. Chainers 1,787 posts

- 15. LINGLING BA HAUS64 491K posts

- 16. #Haus64xLingMOME 494K posts

- 17. Piers 89.6K posts

- 18. Herbert 34.3K posts

- 19. Fuentes 122K posts

- 20. Oslo 74.3K posts