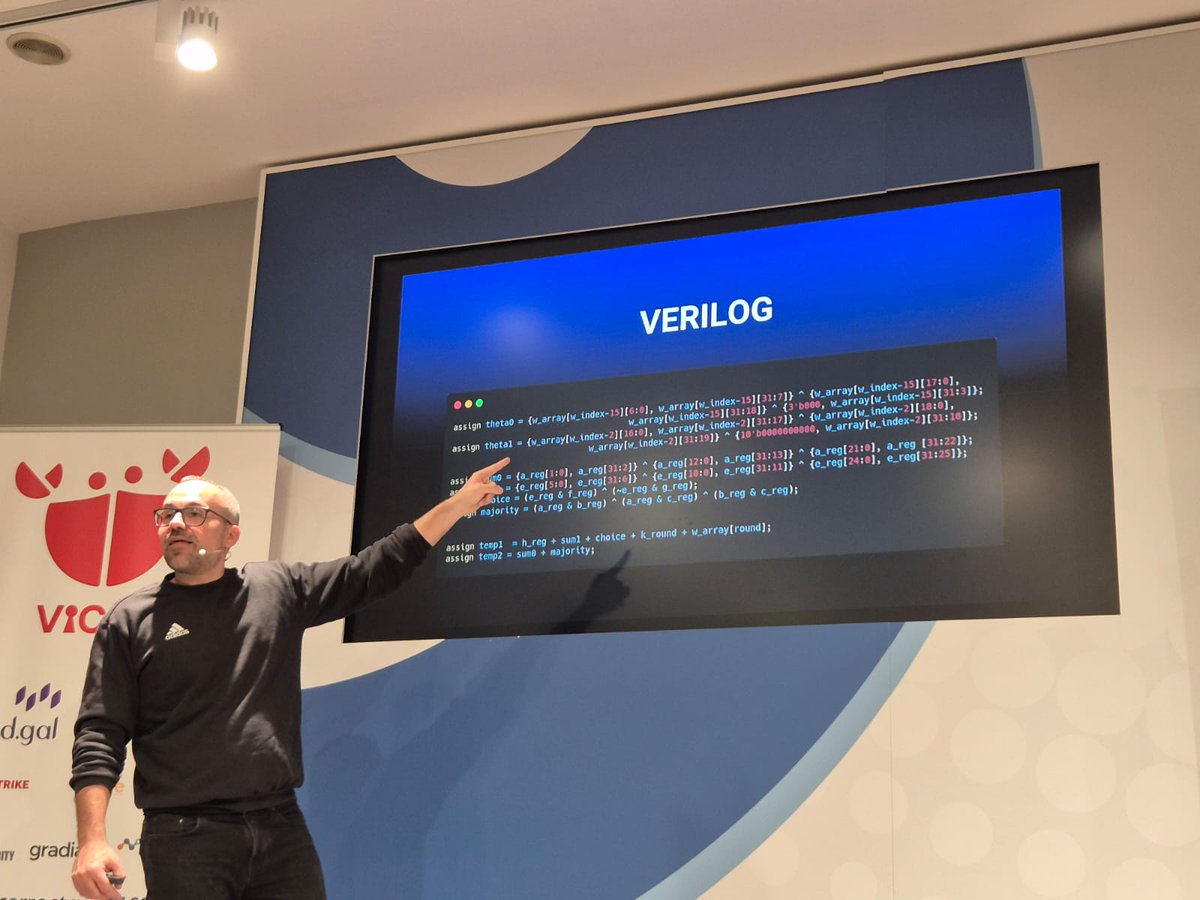

#verilog kết quả tìm kiếm

Built a dual-clock async FIFO in pure Verilog: Gray-coded pointers, registered full/empty, clean CDC. Lint-clean and passes a self-checking testbench. Tiny, fast, rock-solid. #FPGA #Verilog #logicDestroyer

#Shirshendu Roy Advanced Digital System Design A Practical Guide to #Verilog Based #FPGA and #ASIC Implementation

QuasiSoC rv32 nommu Linux: Verilator simulation with interactive UART! So fast and so elegant! Easier than I imagined! RV tests, coremark, and Linux(1:13 for typing) are shown, right side is iverilog simulation of Linux(slowerrr) #FPGA #RISCV #Verilog github.com/regymm/quasiSo…

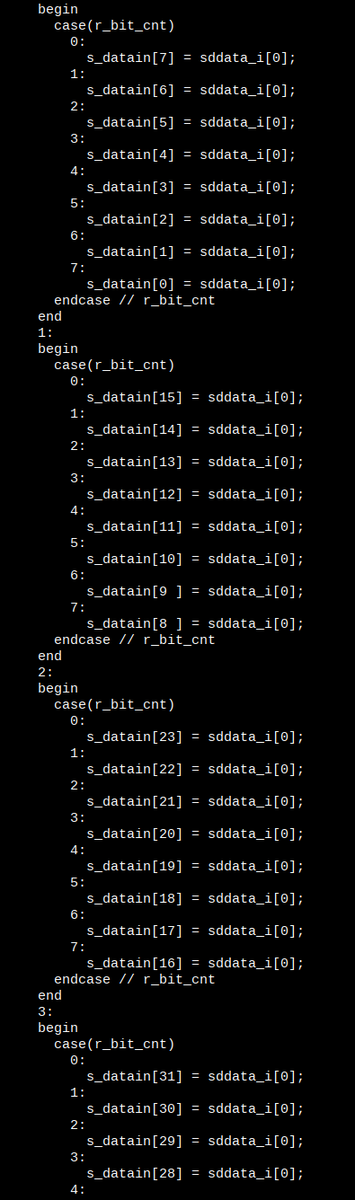

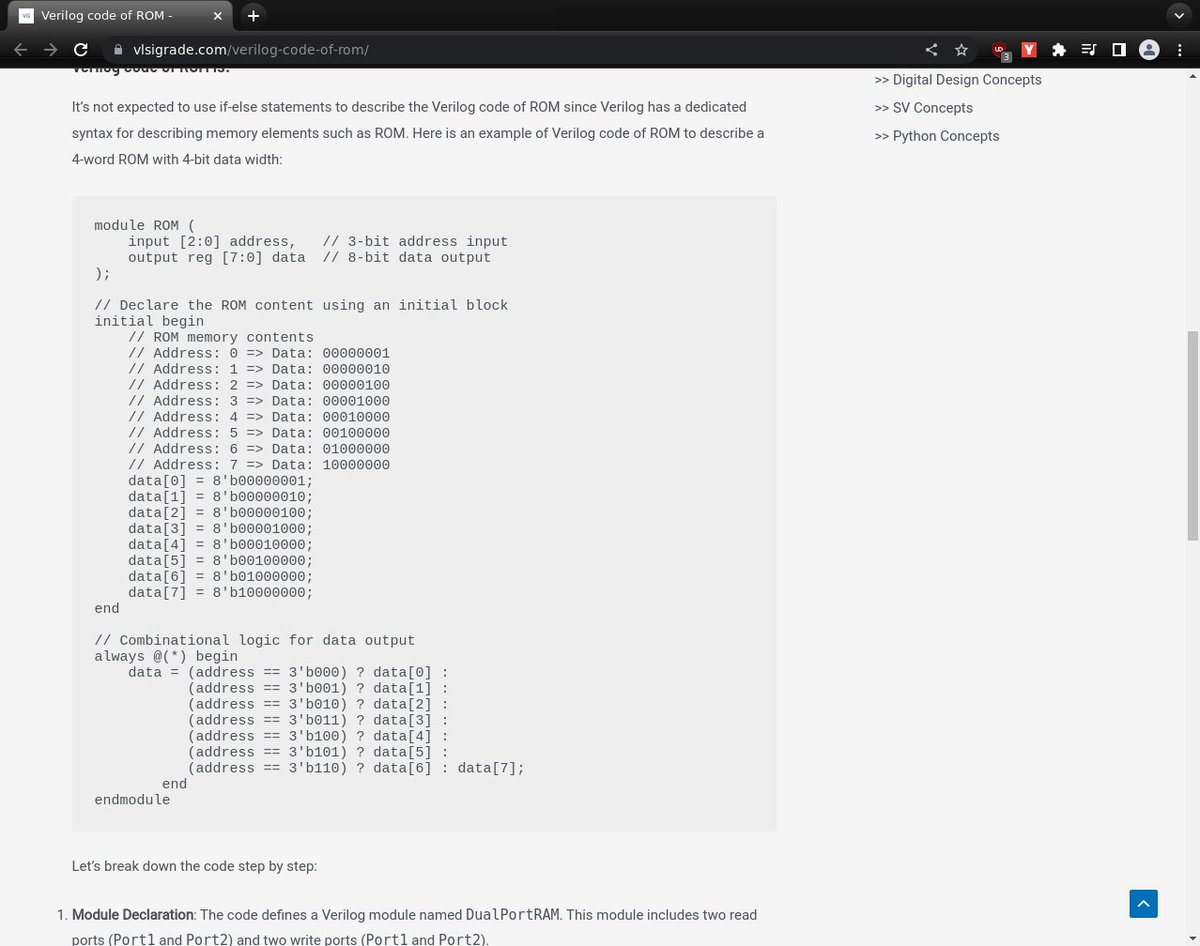

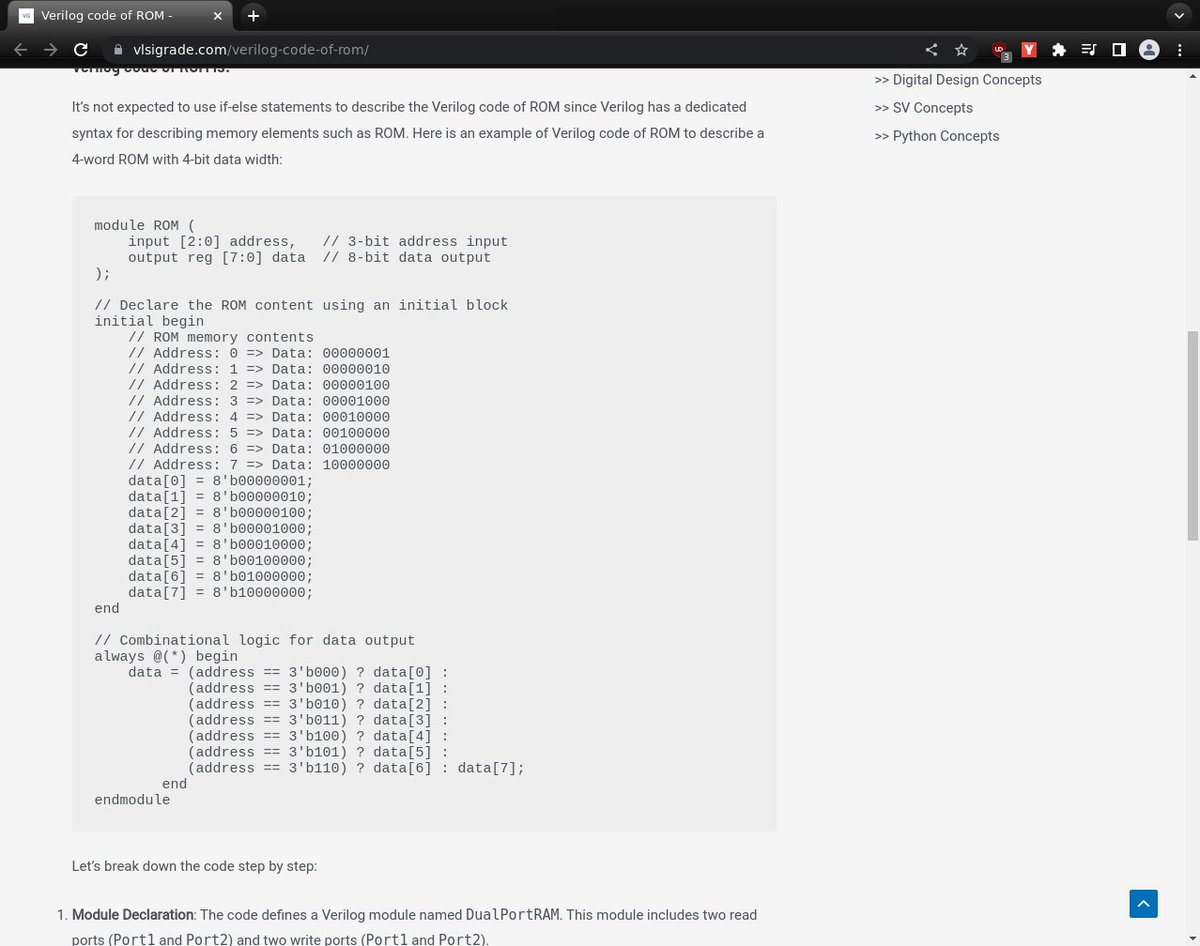

I don’t know #verilog very well, but something tells me that there’s no way this ROM will work. I'll look for another textbook. #fpga

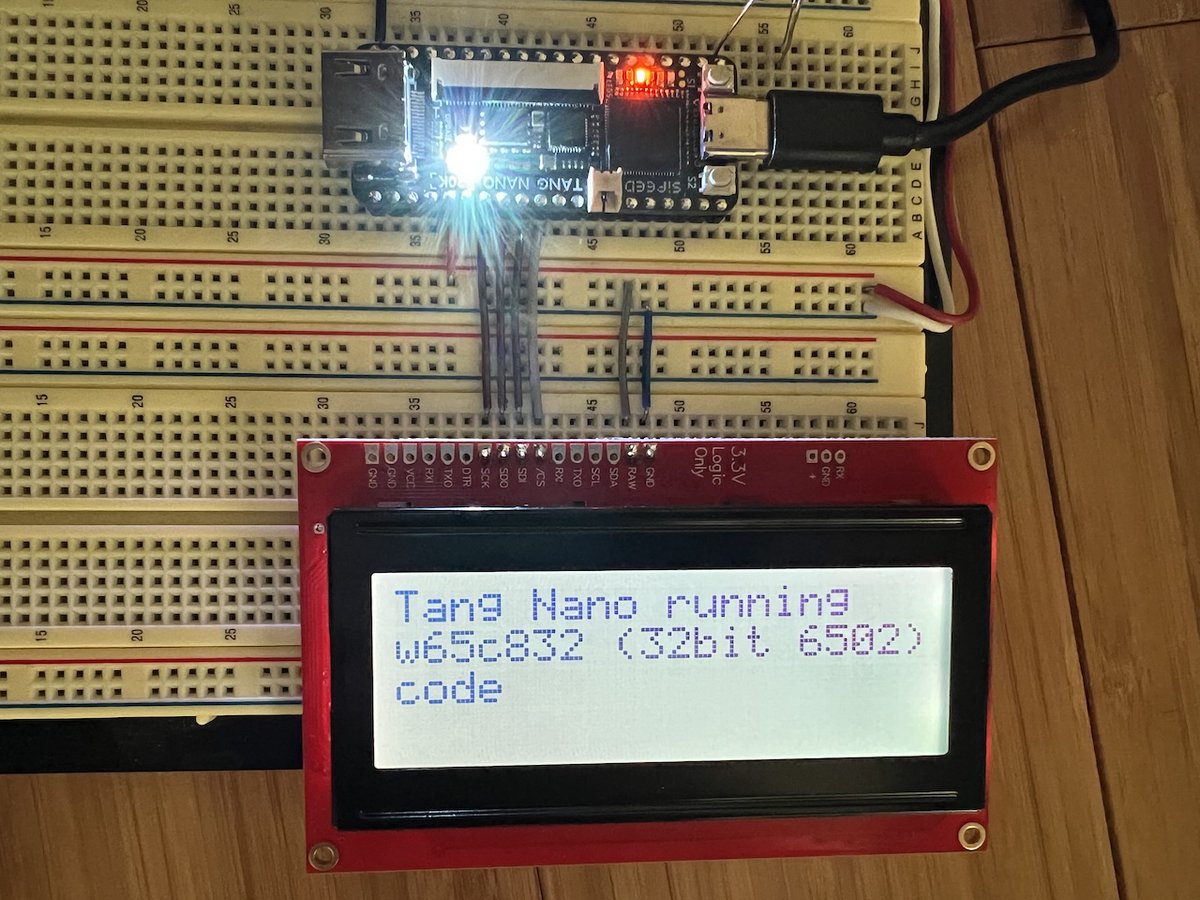

Got this @SipeedIO Tang Nano 20k #FPGA board and got the #Verilog implementation of the W65C832 (32 bit 6502) I did earlier working with it. The dev kit used is still the open source tools: yosys, nextpnr-himbaechel, and openFPGAloader. The currently running program is written…

The last article of controlpaths has maths, power electronics, #Verilog and a #Zynq MPSOC. Learn how to control a #BLDC motor using the KD240 kit and just RTL code. Check it out! controlpaths.com/2024/04/28/mot…

Can #AI write #Verilog code? Absolutely, however, Can AI make a design work? That is the real question. In this article I used #Copilot to generate an AXI4 Lite Slave and something else... Check it out! controlpaths.com/2025/05/04/wri…

Another blinker, who cares... But this one is a Quokka AXI SoC - a prerequisite for web soc builder (github.com/EvgenyMuryshki…) Running a simple assembler program on #riscv, #rtl, #verilog

#RISCV Single Cycle Core in #Verilog (10 video lectures) youtube.com/playlist?list=…

So CLKDIV/DIV/2 for all supported chips by #apicula pointless program on #verilog, but since all primitive pins are connected to IO, this prevents the compiler from optimising them and allows me to track which wires go where.😜 #fpga

I was getting the weirdest #verilog test results until I spotted my test data didn't mean what I thought it meant... (DATAW=10) 🤭 #fpga

Learn FPGA Architecture & Verilog HDL Programming from resource persons from NIELIT Calicut 👨🏫💻 Speakers: Mr. Sreejeesh S. G. & Ms. Nanditha N. Varma #FPGA #Verilog #VLSI #NIELIT #FISAT #TechTraining #ECE

⚡️an ADC for your project? Why not do it inside your FPGA? ADC = (FPGA LVDS + resistors + capacitors). Your FPGA is like a candy store 🤯 Join us to discuss! groups.google.com/g/fpga-wars-ex… ❄️#icestudio #verilog #fpgawars @Obijuan_cube @EladioDM @RueNahcMohr @BinaryDemocrito

💾 ¿#VHDL o #Verilog? Dos lenguajes, mil debates. ¿Cuál es tu favorito para diseñar sistemas lógicos? ¡Déjalo en los comentarios y veamos qué prefiere la comunidad! #Programación #HardwareDesign

🧠 Prefer reading instead? “AI-Accelerated Agile Design Using the ROHD Framework” explores how AI + ROHD enable test-driven, agile hardware development. 📝 buff.ly/kKimODN #AI #HardwareDesign #Verilog #FPGA #ROHD #AgileHardware #OpenSource

Me and My Really Smart Friend (top-tier smart) wrote the FSM code on verilog without GPT. Really feel proud and productive. #VLSI #verilog

Multiples pixeles ws2812b en Verilog, os lo muestro aquí 😏 youtu.be/H4FUshyXjBs #verilog #fpga #vlsi #ws2812b #quartus #altera

youtube.com

YouTube

HDL. #verilog Múltiples píxeles ws2812b

Completed a course on Building a CNN hardware accelerator for MNIST digit recognition on FPGA using verilog. #HardwareAccelerator #Verilog #CNN #FPGA

Turn your breadboard into an FPGA lab Cmod A7-35T (Artix-7) in a 48-pin DIP: 44 I/O + 2 analog, 512KB SRAM, 4MB QSPI, USB-JTAG. $99. Build soft-cores, DSP and weird logic now 👇 sovereignstore.io/product/digile… #FPGA #Verilog #VHDL

sovereignstore.io

Digilent Cmod A7: Breadboardable Artix-7 FPGA Module (Cmod A7-35T) - Sovereignstore.io

Price: (as of - Details)

while learning #verilog it's important to understand the Basics along with case studies. Which Basic to use where, as some might require simple Dataflow and some might require Structural

#soft_FPGA_TD4 4bit CPU #TD4 の #verilog ソースを #verilator でC++ソースへ変換し、Raspberry Pi #Pico2 上で動作するようにしました。 github.com/open-tommie/So… #自作CPUを語る会 #make_cpu #soft_FPGA #電子工作

📌 Full-throttle, wire-speed hardware implementation of Wireguard VPN, using low-cost Artix7 FPGA with opensource toolchain. If you seek security and privacy, nothing is private in our codebase. Our door is wide... 🔗 github.com/chili-chips-ba… #Verilog

10. wireguard-fpga Full-throttle, wire-speed hardware implementation of Wireguard VPN, using low-cost Artix7 FPGA with ... #Verilog github.com/chili-chips-ba…

I’ve started a new learning series — 100 Days of FPGA! Join me as I explore FPGA design, Verilog, and digital systems from scratch. 🎥 Watch it here → youtube.com/@TheHardwareDe… YT/TheHardwareDeveloper #FPGA #Verilog #VLSI #HardwareDesign

Start your Verilog journey today — build smarter circuits! 💡 Read Full Blog here : futurewiz.co.in/blog-detail/ve… #Verilog #HDL #Semiconductor #ChipDesign #Futurewiz

Private lecturer for Engineers. #digial logic design #VHDL #verilog #computerArchitecture #algorithms #programming_club #دوري_أبطال_آسيا_للنخبة #الاتحاد_شباب_الأهلي #ناساف_الهلال #قنوات_الكاس #منصة_شوف #نرفض_خطة_ترامب #غزة_الفاضحة #عاجل_الان #قطر #الدحيل_الاهلي #الدوحة

Big thanks to @YuriPanchul for highlighting the Verilog Meetup booth at #MakerFaire Vallejo! 🙏 linkedin.com/posts/yuripanc… Only 2 days left — come by, say hi, and dive into hands-on #FPGA and #Verilog fun. Don’t miss it! 🚀 #MakerFaire #HardwareDesign #STEM #Innovation

Add-On Course: Introduction to Verilog – Powering the Next-Gen Innovation This initiative reflects I²IT’s mission to bridge the gap between classroom learning and real-world engineering challenges. #I2ITPune #Verilog #AddOnCourse #EandTC #FPGA #VLSIDesign #EmbeddedSystems

#Shirshendu Roy Advanced Digital System Design A Practical Guide to #Verilog Based #FPGA and #ASIC Implementation

Built a dual-clock async FIFO in pure Verilog: Gray-coded pointers, registered full/empty, clean CDC. Lint-clean and passes a self-checking testbench. Tiny, fast, rock-solid. #FPGA #Verilog #logicDestroyer

Designing a #DSP algorithm is just the first part of the complete development, the rest is debugging and (many) simulations. In this article I show you jow you can simulate DSP algorithms using just #Verilog . Check it out! controlpaths.com/2023/05/20/sim…

🚦 Built a Smart Pedestrian Crosswalk Controller using Verilog + Vivado 2024.2 ✅ FSM-based RTL Design ✅ Pedestrian logic + Emergency override ✅ Walk timer countdown Learning hardware, one project at a time :) #Verilog #FPGA #RTLDesign

The last article of controlpaths has maths, power electronics, #Verilog and a #Zynq MPSOC. Learn how to control a #BLDC motor using the KD240 kit and just RTL code. Check it out! controlpaths.com/2024/04/28/mot…

Another blinker, who cares... But this one is a Quokka AXI SoC - a prerequisite for web soc builder (github.com/EvgenyMuryshki…) Running a simple assembler program on #riscv, #rtl, #verilog

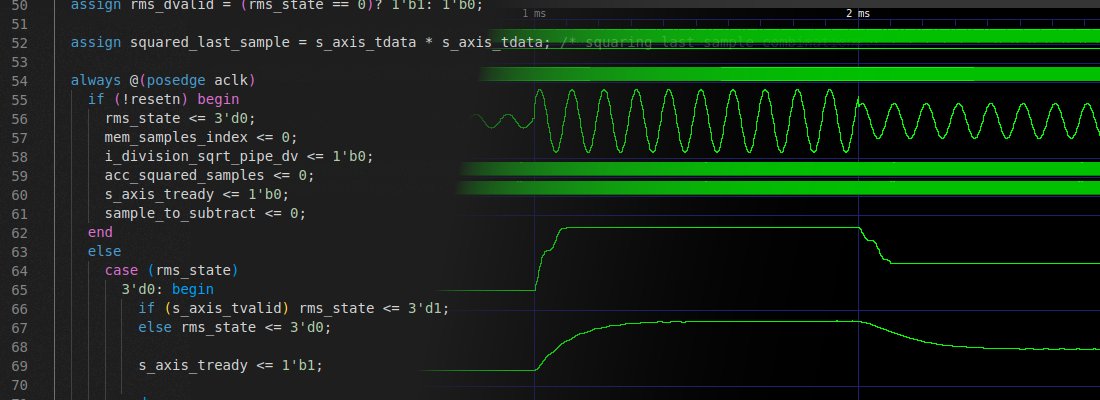

In my job I use to calculate the RMS value of some signals. In this post you can find how to implement an #RMS calculator using #Verilog. Check it out! controlpaths.com/2022/07/18/tru…

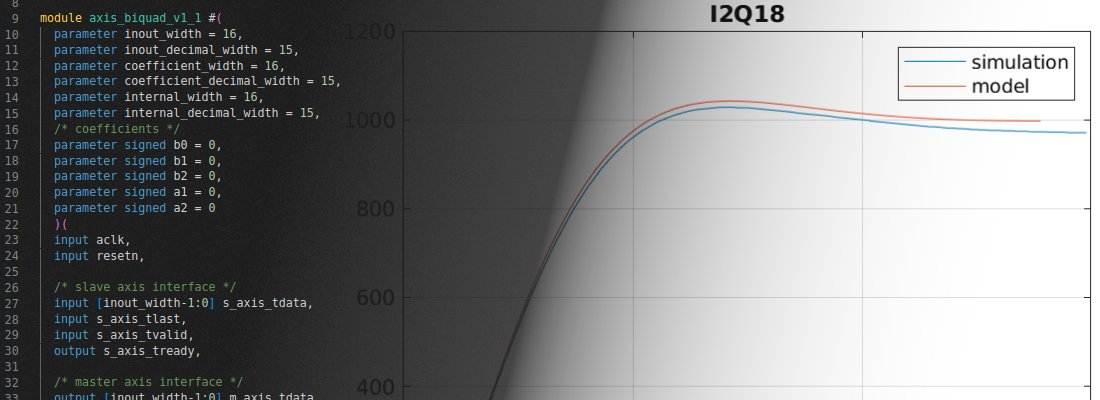

have you seen the AN001 of #controlpaths ? In this Application Note, I tell you how to design and implement an IIR filter in #Verilog from zero. controlpaths.com/articles/an001…

I don’t know #verilog very well, but something tells me that there’s no way this ROM will work. I'll look for another textbook. #fpga

Divide and conquer! And if there is an #FPGA, all the better! Check out how to implement a divider algorithm in #Verilog. controlpaths.com/2022/06/20/div…

#AKGEC's Electronics Club held a workshop on "Digital Hardware Design using #Verilog #HDL" for 2nd-year students, led by Vikram Singh from #STMicroelectronics, featuring hands-on training and enhancing VLSI design #skills. #simulationtool #collaborative #GuestLecture

Something went wrong.

Something went wrong.

United States Trends

- 1. yeonjun 263K posts

- 2. #CARTMANCOIN 1,954 posts

- 3. $APDN $0.20 Applied DNA N/A

- 4. $SENS $0.70 Senseonics CGM N/A

- 5. Broncos 67.8K posts

- 6. $LMT $450.50 Lockheed F-35 N/A

- 7. Raiders 67.1K posts

- 8. Bo Nix 18.6K posts

- 9. #iQIYIiJOYTH2026 1.21M posts

- 10. Geno 19.3K posts

- 11. daniela 55.4K posts

- 12. Kehlani 11.4K posts

- 13. Sean Payton 4,878 posts

- 14. #Pluribus 3,118 posts

- 15. #PowerForce 1,065 posts

- 16. Danny Brown 3,284 posts

- 17. #NOLABELS_PART01 113K posts

- 18. Kenny Pickett 1,523 posts

- 19. John Wayne 1,080 posts

- 20. MIND-BLOWING 22.3K posts