#verilog نتائج البحث

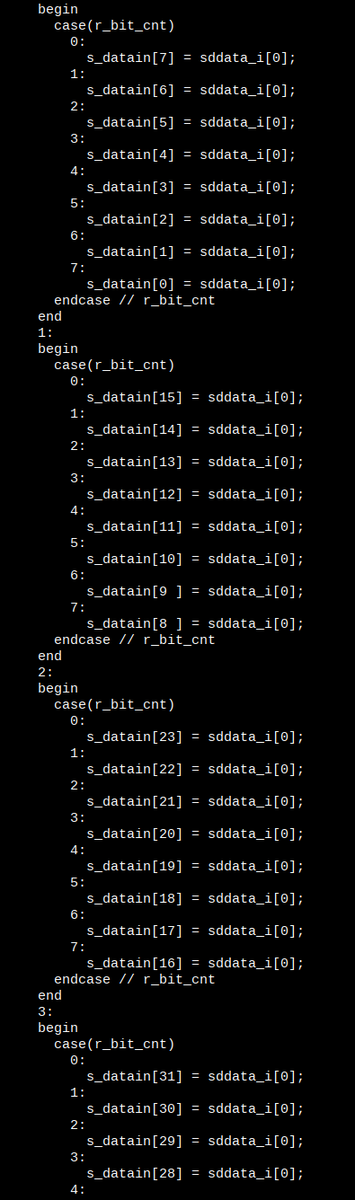

QuasiSoC rv32 nommu Linux: Verilator simulation with interactive UART! So fast and so elegant! Easier than I imagined! RV tests, coremark, and Linux(1:13 for typing) are shown, right side is iverilog simulation of Linux(slowerrr) #FPGA #RISCV #Verilog github.com/regymm/quasiSo…

Built a dual-clock async FIFO in pure Verilog: Gray-coded pointers, registered full/empty, clean CDC. Lint-clean and passes a self-checking testbench. Tiny, fast, rock-solid. #FPGA #Verilog #logicDestroyer

Another blinker, who cares... But this one is a Quokka AXI SoC - a prerequisite for web soc builder (github.com/EvgenyMuryshki…) Running a simple assembler program on #riscv, #rtl, #verilog

#Shirshendu Roy Advanced Digital System Design A Practical Guide to #Verilog Based #FPGA and #ASIC Implementation

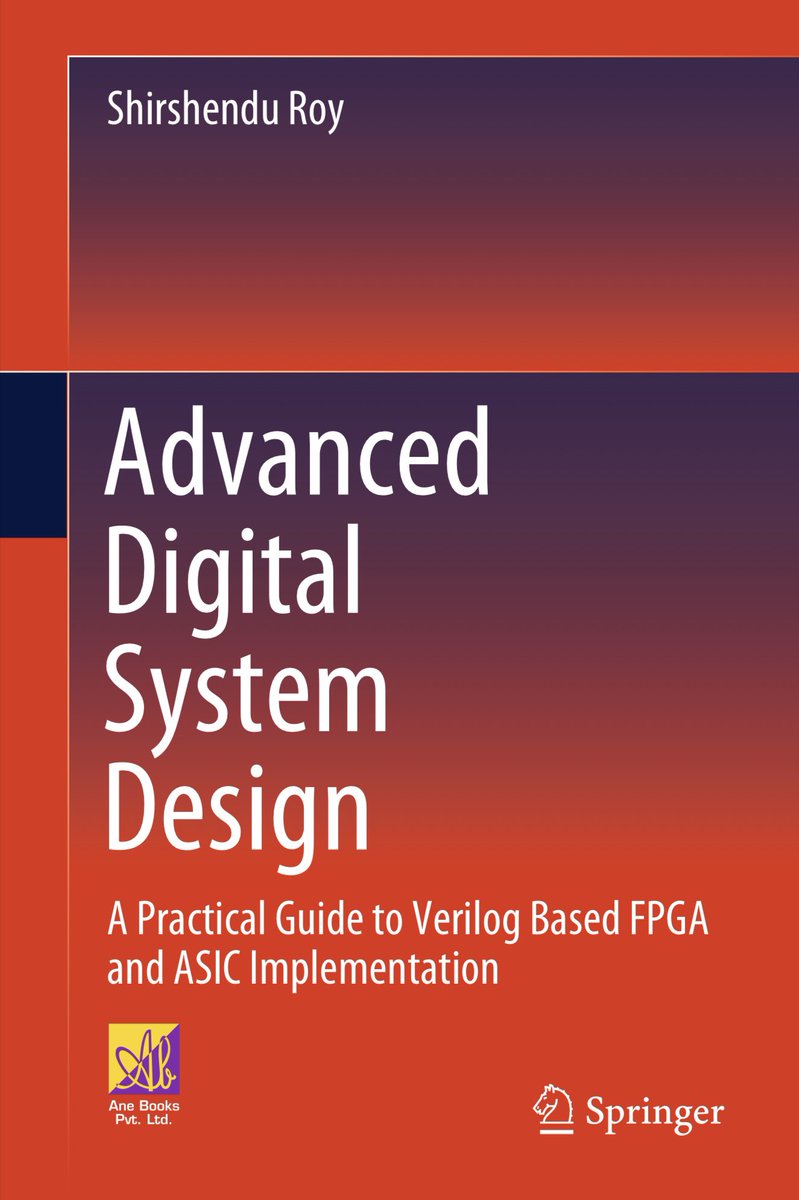

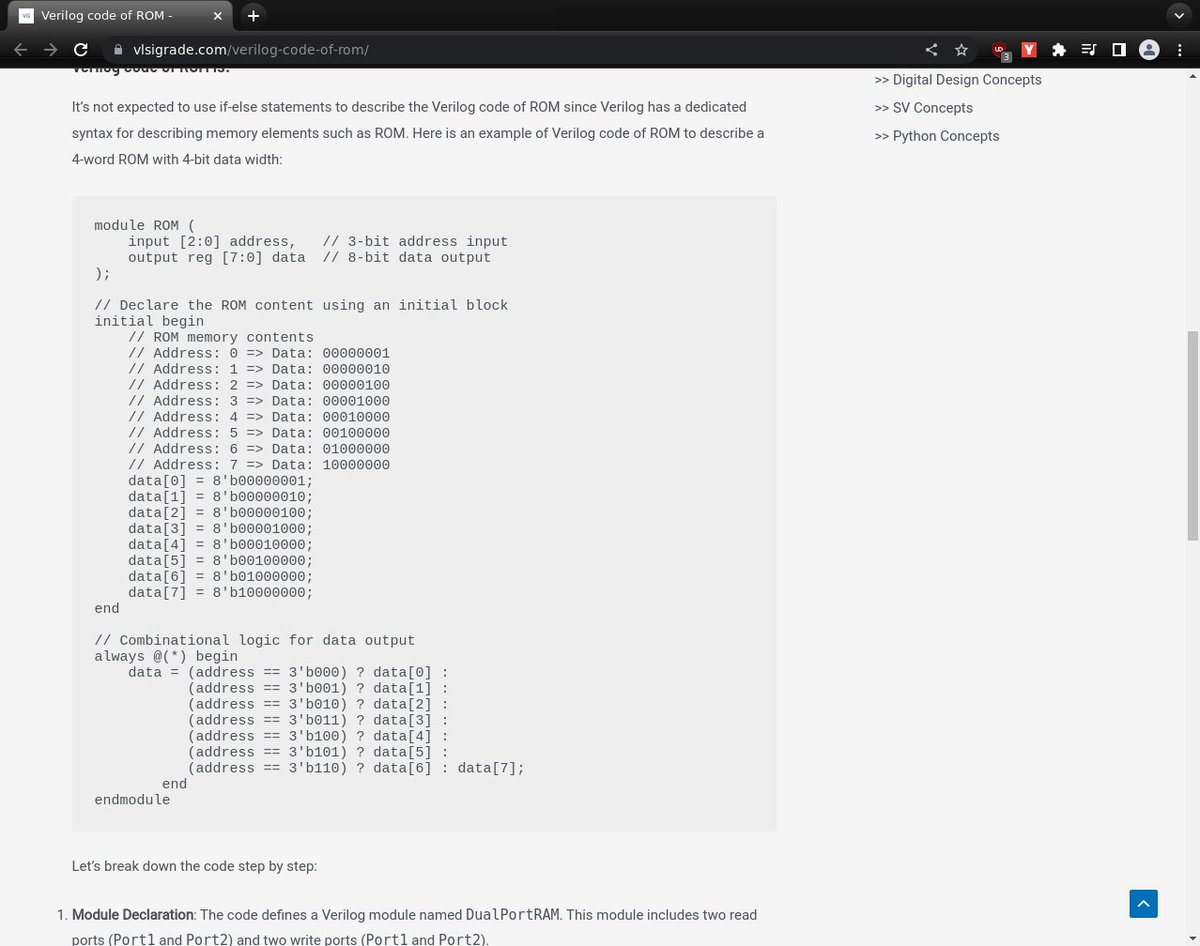

I don’t know #verilog very well, but something tells me that there’s no way this ROM will work. I'll look for another textbook. #fpga

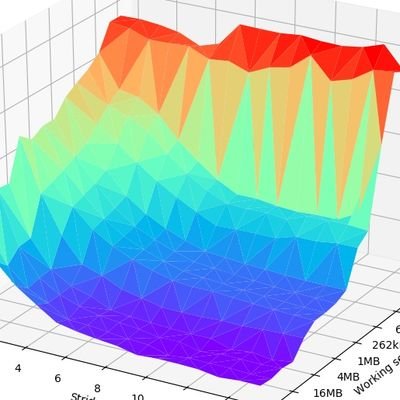

I was getting the weirdest #verilog test results until I spotted my test data didn't mean what I thought it meant... (DATAW=10) 🤭 #fpga

#RISCV Single Cycle Core in #Verilog (10 video lectures) youtube.com/playlist?list=…

Here's a video of an #FPGA in an IceBLIP board (iCE40-LP1K) with #Verilog code making it a #TMS1000 microcontroller. It's running the original ROM from the 1970's Simon Says electronics game. It's still a little glitchy so it has no speaker. Code was posted on GitHub.…

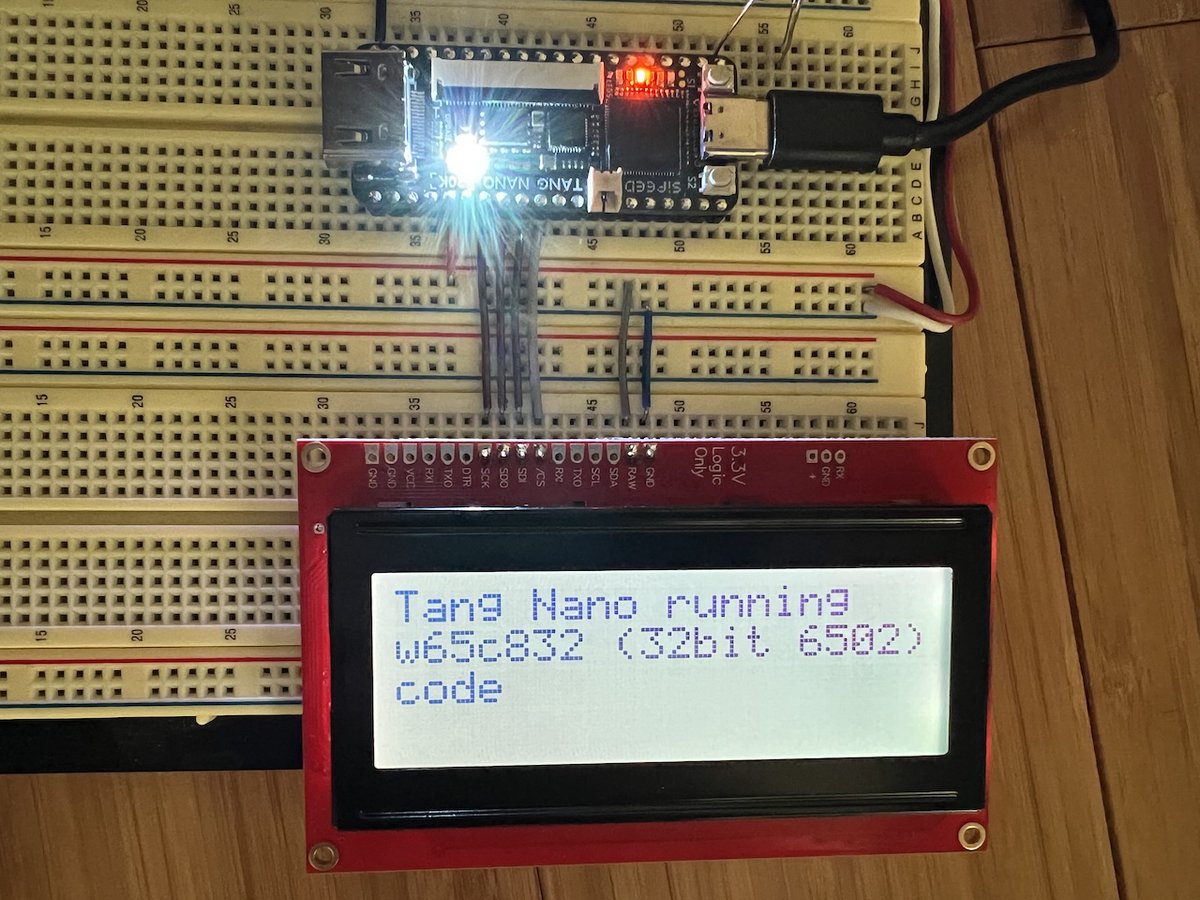

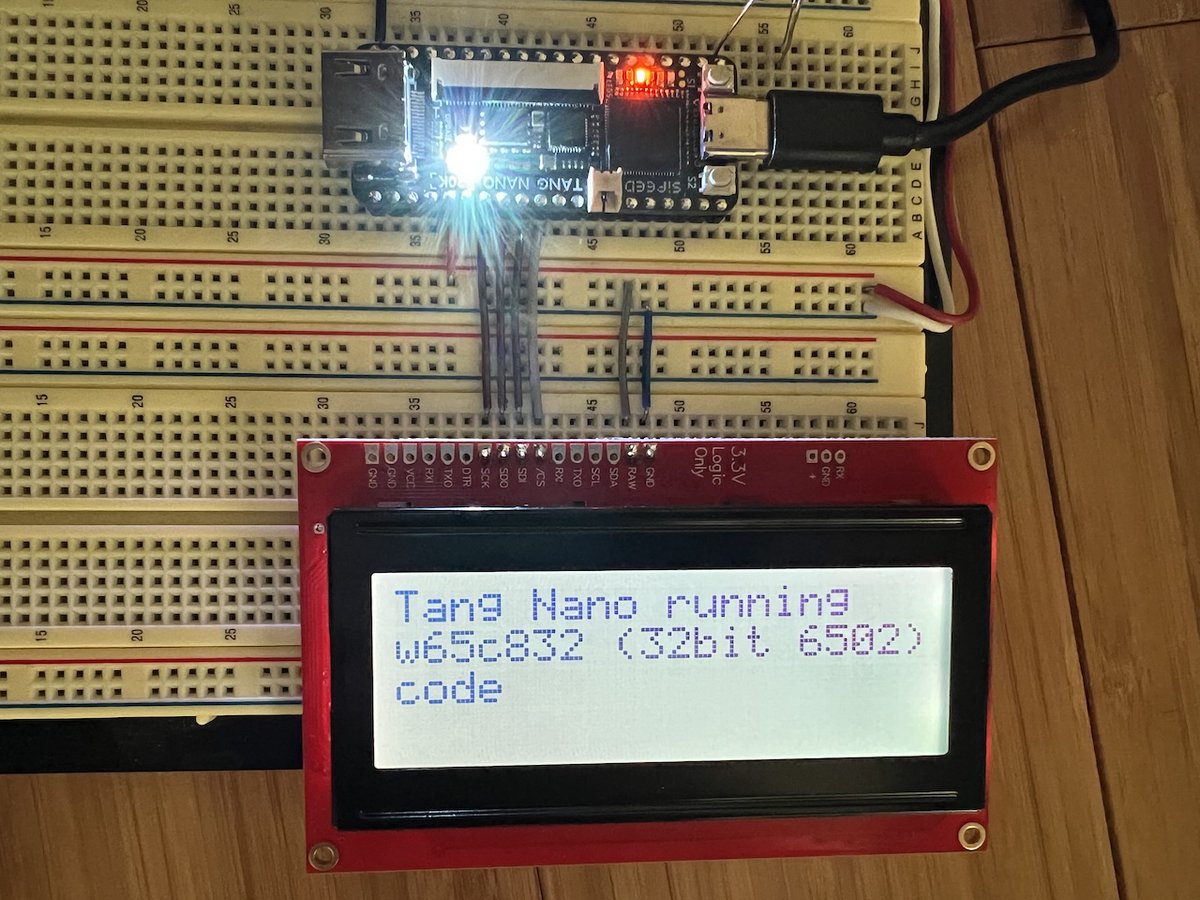

Got this @SipeedIO Tang Nano 20k #FPGA board and got the #Verilog implementation of the W65C832 (32 bit 6502) I did earlier working with it. The dev kit used is still the open source tools: yosys, nextpnr-himbaechel, and openFPGAloader. The currently running program is written…

⚡️an ADC for your project? Why not do it inside your FPGA? ADC = (FPGA LVDS + resistors + capacitors). Your FPGA is like a candy store 🤯 Join us to discuss! groups.google.com/g/fpga-wars-ex… ❄️#icestudio #verilog #fpgawars @Obijuan_cube @EladioDM @RueNahcMohr @BinaryDemocrito

The last article of controlpaths has maths, power electronics, #Verilog and a #Zynq MPSOC. Learn how to control a #BLDC motor using the KD240 kit and just RTL code. Check it out! controlpaths.com/2024/04/28/mot…

So CLKDIV/DIV/2 for all supported chips by #apicula pointless program on #verilog, but since all primitive pins are connected to IO, this prevents the compiler from optimising them and allows me to track which wires go where.😜 #fpga

As of tomorrow, we'll be at @DVConEurope . If you're there, stop by and say hi! 👋 #VHDL #Verilog #SystemVerilog #EDAsoftware #EDA #DesignAutomation #IDE #HDL #Productivity

T017 「HDLによるLSI開発技術(Verilog-HDL編)」<FPGA開発シリーズ1A> FPGAの評価ボードを用いた実習を通じて、Verilog-HDLによるFPGA開発技術を習得します。実習では7セグメントLEDデコーダ回路、カウンタ回路などを組み合わせて24時間時計を作成します。 #HDL #Verilog #FPGA #ディジタル回路

Can #AI write #Verilog code? Absolutely, however, Can AI make a design work? That is the real question. In this article I used #Copilot to generate an AXI4 Lite Slave and something else... Check it out! controlpaths.com/2025/05/04/wri…

I’ve started a new learning series — 100 Days of FPGA! Join me as I explore FPGA design, Verilog, and digital systems from scratch. 🎥 Watch it here → youtube.com/@TheHardwareDe… YT/TheHardwareDeveloper #FPGA #Verilog #VLSI #HardwareDesign

Start your Verilog journey today — build smarter circuits! 💡 Read Full Blog here : futurewiz.co.in/blog-detail/ve… #Verilog #HDL #Semiconductor #ChipDesign #Futurewiz

Private lecturer for Engineers. #digial logic design #VHDL #verilog #computerArchitecture #algorithms #programming_club #دوري_أبطال_آسيا_للنخبة #الاتحاد_شباب_الأهلي #ناساف_الهلال #قنوات_الكاس #منصة_شوف #نرفض_خطة_ترامب #غزة_الفاضحة #عاجل_الان #قطر #الدحيل_الاهلي #الدوحة

Big thanks to @YuriPanchul for highlighting the Verilog Meetup booth at #MakerFaire Vallejo! 🙏 linkedin.com/posts/yuripanc… Only 2 days left — come by, say hi, and dive into hands-on #FPGA and #Verilog fun. Don’t miss it! 🚀 #MakerFaire #HardwareDesign #STEM #Innovation

linkedin.com

Verilog Meetup booth at Maker Faire in Vallejo, California. We use Gowin boards to introduce RTL to...

Verilog Meetup booth at Maker Faire in Vallejo, California. We use Gowin boards to introduce RTL to kids and curious by creating games on LCD screen using SystemVerilog.

Add-On Course: Introduction to Verilog – Powering the Next-Gen Innovation This initiative reflects I²IT’s mission to bridge the gap between classroom learning and real-world engineering challenges. #I2ITPune #Verilog #AddOnCourse #EandTC #FPGA #VLSIDesign #EmbeddedSystems

Os muestro como modelar el dispositivo WS2812B en Verilog, aquí 🙃 youtu.be/uoo8HL0Txk8 #verilog #ws2812b #quartus #modelsim #altera

youtube.com

YouTube

HDL. #verilog WS2812B

Private lecturer for Engineers. #digial logic design #VHDL #verilog #computerArchitecture #algorithms #programming #CaneloCrawford #دوري_أبطال_آسيا_للنخبة

Private lecturer for Engineers. #digial logic design #VHDL #verilog #computerArchitecture #algorithms #programming #حي_الشتاء #حياك_في_بيتك #القمه_العربيه #قمه_الدوحه

Private lecturer for Engineers. #digial logic design #VHDL #verilog #computerArchitecture #algorithms #programming #قمة_قطر #قمة_الدوحة #القمة_العربية_الإسلامية #دوري_أبطال_آسيا_للنخبة #الدوحة #قطر #النصر_الخلود #الدوحه_الآن

Private lecturer for Engineers. #digial logic design #VHDL #verilog #computerArchitecture #algorithms #programming #تلفزيون_قطر | #جامعتنا #الدوحة #قطر #الريان #الرياض #جامعة_الملك_عبدالعزيز #جامعة_السلطان_قابوس #جامعه_البلقاء_التطبيقيه #الهلال_القادسيه #الهلال #الكويت

>so a 32‑bit word can be read or written every CPU cycle (“double‑pumping” the memory). .. 486 PC is complex..more so than the game consoles I’ve worked on. The ao486 CPU alone is >25K lines of #Verilog, versus a few K for older cores like M68K. Debugging on hardware was painful>

Just completed this amazing course 🎓 AI-Augmented Digital Logic Design on Udemy! Verilog, VHDL, Simulation, Waveform Analysis – सब कुछ सीखा AI tools जैसे ChatGPT, Gemini & Colab से 🔥 👉 udemy.com/course/ai-augm… #DigitalDesign #Verilog #VHDL #AItools #Udemy

udemy.com

AI-Augmented Digital Logic Design: From Elementary to Master

Not just another HDL course—use AI to learn, design, simulate, and master digital logic design

Built a dual-clock async FIFO in pure Verilog: Gray-coded pointers, registered full/empty, clean CDC. Lint-clean and passes a self-checking testbench. Tiny, fast, rock-solid. #FPGA #Verilog #logicDestroyer

Learn Verilog & VHDL the modern way — using AI tools to generate, simulate, debug & document HDL designs in Google Colab. No coding background needed. Built for beginners & future professionals. Now live on Udemy: tinyurl.com/26hq97sa #Verilog #VHDL #FPGA #VLSI

🚀 Just dropped: ROOM (Read-Once-Only Memory) Verilog Reference Quantum-inspired, post-algebraic primitive enforcing true one-time keys — modeled after measurement & the no-cloning theorem. 👉 Explore the repo + details: qsymbolic.com/2025/09/06/roo… #PQC #FPGA #Verilog #ROOM

#Shirshendu Roy Advanced Digital System Design A Practical Guide to #Verilog Based #FPGA and #ASIC Implementation

Built a dual-clock async FIFO in pure Verilog: Gray-coded pointers, registered full/empty, clean CDC. Lint-clean and passes a self-checking testbench. Tiny, fast, rock-solid. #FPGA #Verilog #logicDestroyer

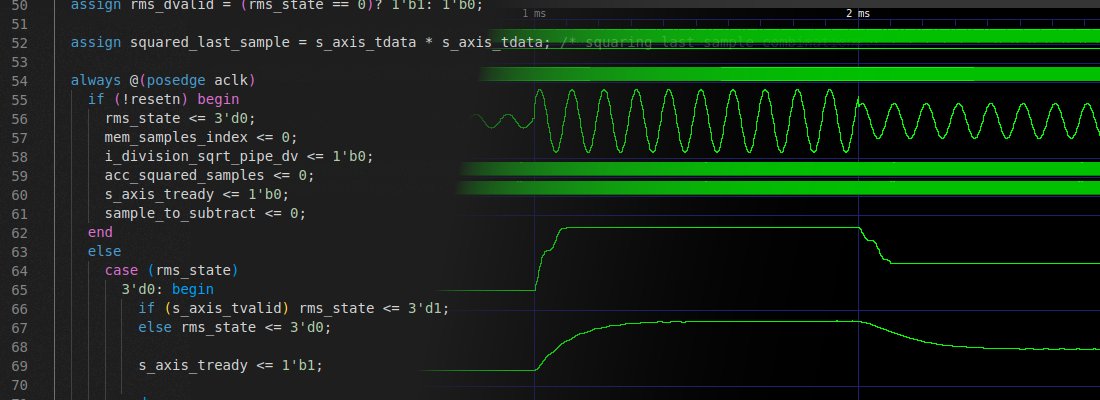

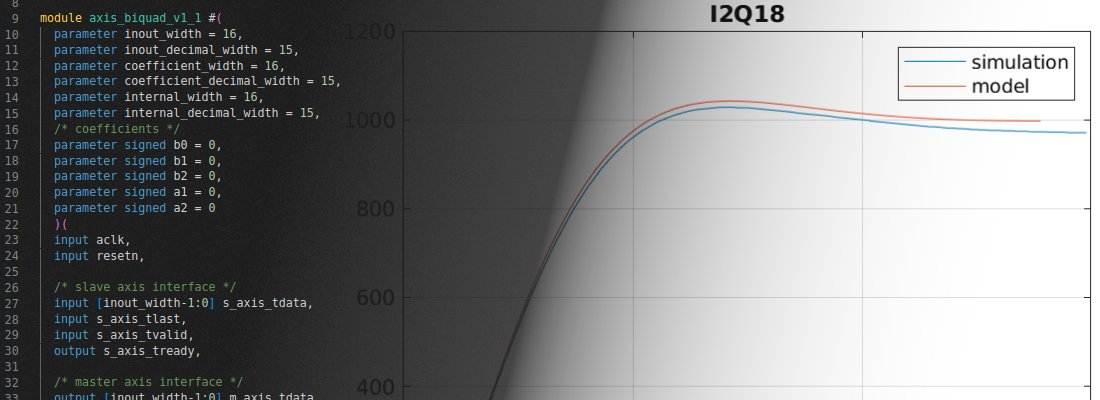

Designing a #DSP algorithm is just the first part of the complete development, the rest is debugging and (many) simulations. In this article I show you jow you can simulate DSP algorithms using just #Verilog . Check it out! controlpaths.com/2023/05/20/sim…

Another blinker, who cares... But this one is a Quokka AXI SoC - a prerequisite for web soc builder (github.com/EvgenyMuryshki…) Running a simple assembler program on #riscv, #rtl, #verilog

Join us this Thursday (August 21) for our Automated Regression Testing for #VHDL #Verilog webinar, during which you will learn how to convert your testbenches into fully automated, repeatable regression flows. aldec.com/en/company/eve… #EDA #FPGA #FPGADesign

I don’t know #verilog very well, but something tells me that there’s no way this ROM will work. I'll look for another textbook. #fpga

In my job I use to calculate the RMS value of some signals. In this post you can find how to implement an #RMS calculator using #Verilog. Check it out! controlpaths.com/2022/07/18/tru…

have you seen the AN001 of #controlpaths ? In this Application Note, I tell you how to design and implement an IIR filter in #Verilog from zero. controlpaths.com/articles/an001…

The last article of controlpaths has maths, power electronics, #Verilog and a #Zynq MPSOC. Learn how to control a #BLDC motor using the KD240 kit and just RTL code. Check it out! controlpaths.com/2024/04/28/mot…

Divide and conquer! And if there is an #FPGA, all the better! Check out how to implement a divider algorithm in #Verilog. controlpaths.com/2022/06/20/div…

I was getting the weirdest #verilog test results until I spotted my test data didn't mean what I thought it meant... (DATAW=10) 🤭 #fpga

Got this @SipeedIO Tang Nano 20k #FPGA board and got the #Verilog implementation of the W65C832 (32 bit 6502) I did earlier working with it. The dev kit used is still the open source tools: yosys, nextpnr-himbaechel, and openFPGAloader. The currently running program is written…

#AKGEC's Electronics Club held a workshop on "Digital Hardware Design using #Verilog #HDL" for 2nd-year students, led by Vikram Singh from #STMicroelectronics, featuring hands-on training and enhancing VLSI design #skills. #simulationtool #collaborative #GuestLecture

Something went wrong.

Something went wrong.

United States Trends

- 1. Columbus 105K posts

- 2. #WWERaw 44.9K posts

- 3. #IndigenousPeoplesDay 6,334 posts

- 4. Middle East 192K posts

- 5. Seth 39.8K posts

- 6. $BURU N/A

- 7. Darius Smith 1,620 posts

- 8. #IDontWantToOverreactBUT 1,146 posts

- 9. Marc 41K posts

- 10. Thanksgiving 1,877 posts

- 11. #SwiftDay 9,708 posts

- 12. The Vision 92.1K posts

- 13. Flip 50.4K posts

- 14. Egypt 195K posts

- 15. Mike Shildt N/A

- 16. Knesset 154K posts

- 17. THANK YOU PRESIDENT TRUMP 57.2K posts

- 18. Victory Monday 3,028 posts

- 19. #MondayMotivation 14.8K posts

- 20. Bronson 8,446 posts