PipelineC (fosstodon.org/@pipelinec)

@pipelinec_hdl

http://fosstodon.org/@pipelinec PipelineC hardware description language

Potrebbero piacerti

First ever raytraced game thats not software? 1080p realtime, interactive, fixed+float point, 3D vector math, no CPU, no instructions, autopipelined in #FPGA! @suarezvictor's fantastic work w/ CflexHDL + PipelineC! #raytracing #graphics #hardware #gamedev youtu.be/hn3sr3VMJQU

youtube.com

YouTube

Sphery vs. Shapes

Over at Digital Design HQ #ddhq, I'm documenting and discussing a #hardware #FPGA #I2S #audio #pmod to-from #AXI project. Stop on by 👋 and see how nice it is to work in #PipelineC 🤓 #RTL #HDL #HLS discord.gg/ceheSfKzRM

discord.com

Join the Digital Design HQ Discord Server!

Check out the Digital Design HQ community on Discord - hang out with 4563 other members and enjoy free voice and text chat.

Wow, great article on working with #FPGAs. Couldn't agree more that manual by hand pipelining is annoying and tools should do it for you 🤓 #hardware #hdl #hls #eda stitt-hub.com/its-time-to-re…

#graphics #demoscene folks: What's possible with just a few hundred bits of memory? Make custom #ASIC #hardware. #PipelineC friends @suarezvictor and @DutraCGI have done LARGE #FPGA demos in the past. Now the challenge is to be very SMALL! 🤓 tinytapeout.com/competitions/d…

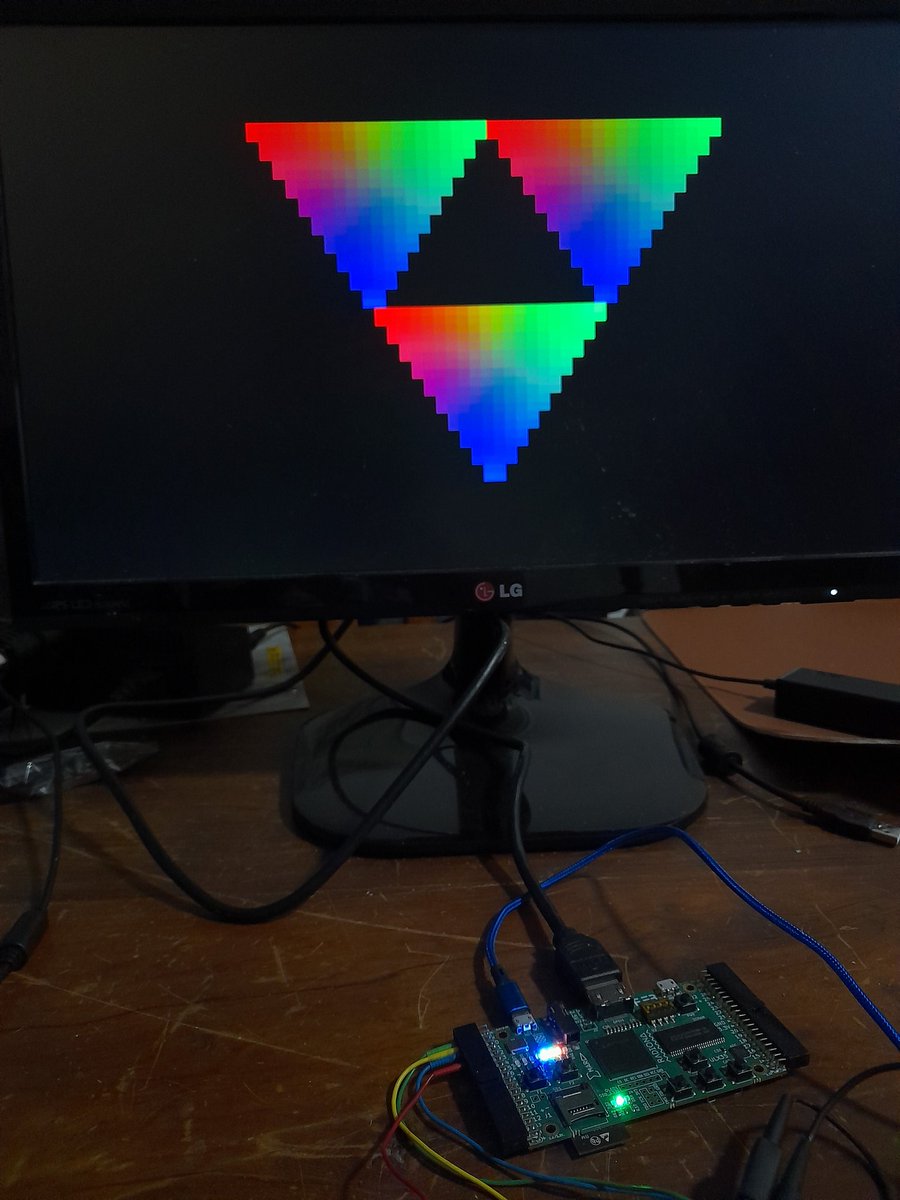

Icosphere 😄 80T/240V model #FPGA Rasterizer made on #ULX3S using @pipelinec_hdl 320x240px DVI output ~4000 triangles/second? 😳 #gpu #triangles #graphics #cgi #3d #rasterizer #vga #diy

Making a #FPGA #GPU with @pipelinec_hdl... Small lutram framebuffer works! Now with screen space vertex streaming...

Several talks in one. #eda #asic #fpga #hdl Can't share enough. Thanks for the great talk Rice! youtu.be/R2ak8KVo0F0

youtube.com

YouTube

"Riding The Wave: Building Wave Pipelines in FPGAs" - Rice Shelley...

How many triangles until it counts as a GPU? A runtime variable amount > 1? 😅 Cool indeed 😎

So... I made a "GPU" with the #ulx3s #fpga and @pipelinec_hdl... Its actually just a rasterizer with HDMI output but "GPU" sounds more cool 😎 #gpu #rasterization #triangle #graphics #opengl #pipelinec

Dream is more generic pipelined streaming compute accelerator #hardware. #photogrammetry next ? Want custom dataflow to-from memories managed by #CPU threads. looking for help, plenty of work to do. Come chat on Discord 🤓 discord.gg/7DECDMvbmc #HDL #FPGA #HLS #PipelineC

What kind of fixed point (or small floating point) shaders without textures do yall #graphics folks know of? I know @BrunoLevy01 had that great link I need to dig into still 🙌 🤓 #FPGA #RISCV #hardware #hdl #vhdl #verilog #PipelineC #HLS x.com/BrunoLevy01/st…

So... I made a "GPU" with the #ulx3s #fpga and @pipelinec_hdl... Its actually just a rasterizer with HDMI output but "GPU" sounds more cool 😎 #gpu #rasterization #triangle #graphics #opengl #pipelinec

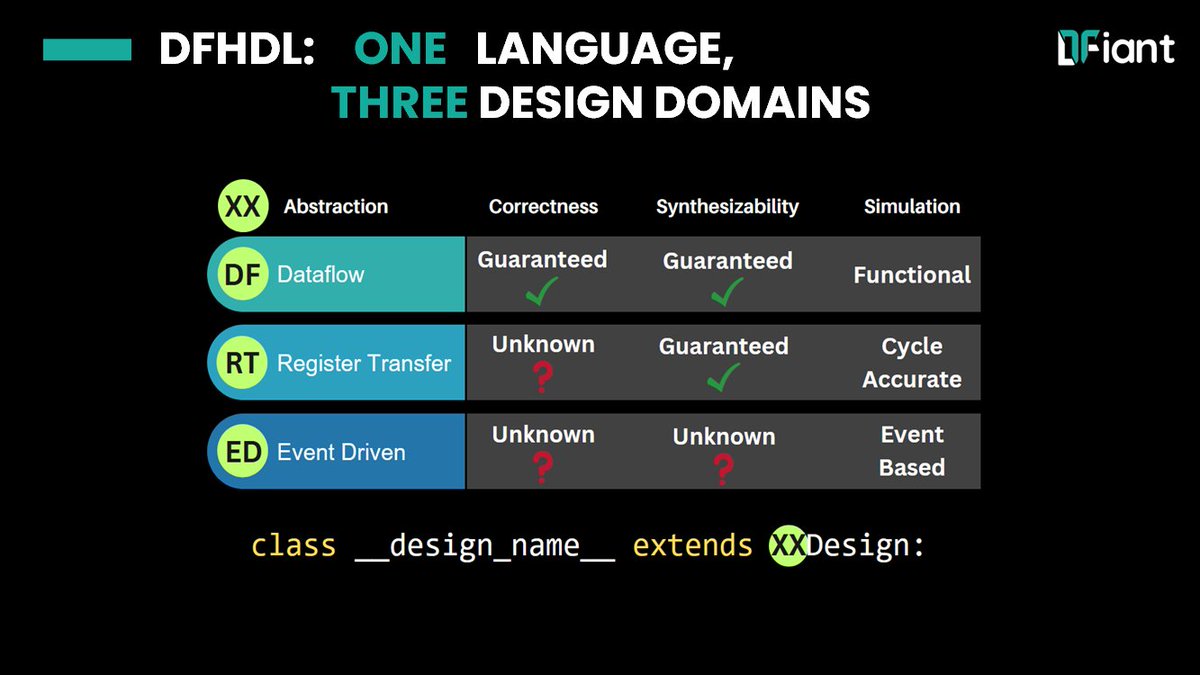

Today is the day! First release of DFiant HDL (DFHDL) 🚀 It takes us some time, so we'll be extending to May 2nd, Anywhere On Earth 😉 Here is a little teaser of our updated documentation.

Finally, first official launch🚀of DFiant HDL (DFHDL) #opensource. The only hardware description language you'll ever need 😉 Save the date! May 2nd, 2024. 🗓️ Follow me stay updated. Feature list ->

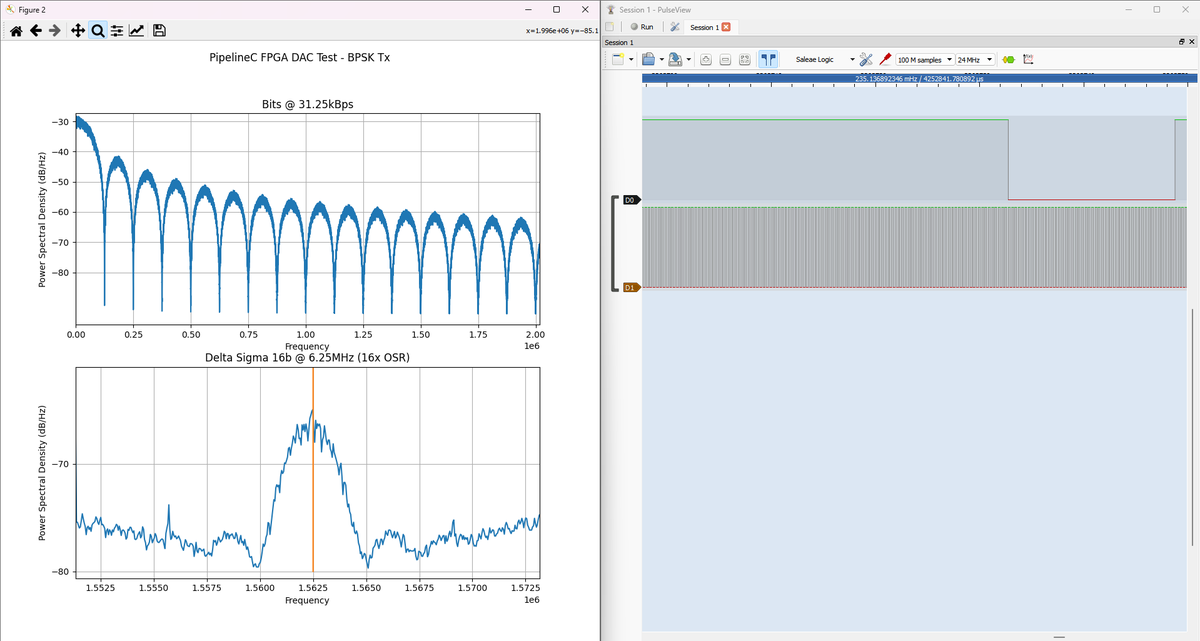

IT WORKS!!!! #BPSK Transmitter using #DeltaSigmaModulator made with the #ULX3S #FPGA and @pipelinec_hdl ! #RF #SDR #DSP #DAC

Blinking the #ULX3S led with #PipelineC ! @pipelinec_hdl is a Magic tool that turns C into HDL 🔥 #fpga #ledblink #lattice

We have #MSK! Doing some simulations (tests next week) for a #SDR #FPGA #RF beacon made with #PipelineC... Next is GMSK, maybe LoRa ? 😁

Thanks again to @robstewartUK and the #HAFDAL24 organizers for having me 🤓 Couldn't make it there yourself? Video is available: fosstodon.org/@pipelinec/112… 🙌 #FPGA #hdl #hls #hardware #rtl

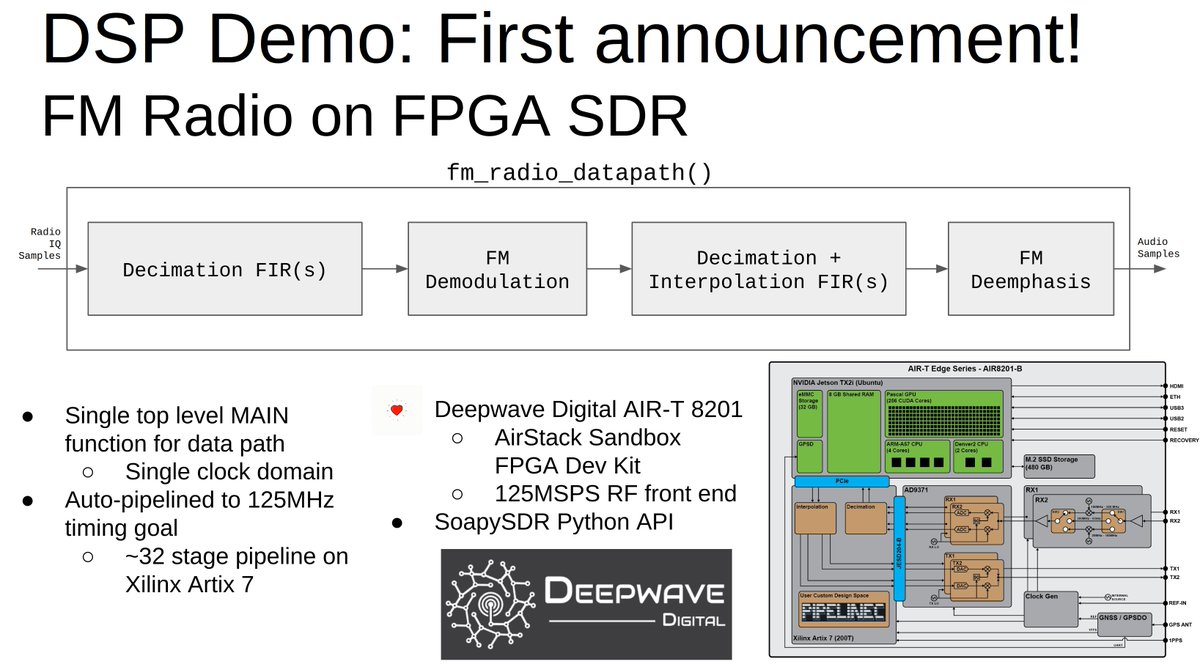

Use #PipelineC to listen to FM #radio with an #FPGA #SDR! Huge thanks to @DutraCGI and @Darkknight512 for making this first version a great learning process. And @deepwavedigital for the fantastic #hardware platform and workplace <3 fosstodon.org/@pipelinec/112… #hdl #hls #asic

United States Tendenze

- 1. #SantaChat 9,174 posts

- 2. Venezuela 762K posts

- 3. Jack Smith 99.1K posts

- 4. Dan Bongino 17.7K posts

- 5. Big Christmas 15.4K posts

- 6. Talavera 30.4K posts

- 7. Endrick 15.4K posts

- 8. Ewers 13.4K posts

- 9. Jared Isaacman 4,180 posts

- 10. Weaver 7,907 posts

- 11. Cherki 32.6K posts

- 12. The Oscars 25.6K posts

- 13. NextNRG Inc 1,528 posts

- 14. Old Dominion N/A

- 15. Kawhi 5,022 posts

- 16. Fani 35.8K posts

- 17. Gunna 24.1K posts

- 18. Coinbase 33.7K posts

- 19. Jimmy Stewart 3,078 posts

- 20. Unblock 3,397 posts

Potrebbero piacerti

-

YosysHQ

YosysHQ

@YosysHQ -

Pablo Trujillo

Pablo Trujillo

@controlpaths -

Antmicro

Antmicro

@antmicro -

Flux

Flux

@WillFlux -

Charles Eric LaForest, PhD

Charles Eric LaForest, PhD

@elaforest -

Enjoy Digital

Enjoy Digital

@enjoy_digital -

Matthew Venn

Matthew Venn

@matthewvenn -

asic destroyer

asic destroyer

@splinedrive -

Machdyne UG

Machdyne UG

@machdyne -

Victor Suarez Rovere

Victor Suarez Rovere

@suarezvictor -

Tim 'mithro' Ansell

Tim 'mithro' Ansell

@mithro -

Marcelo Samsoniuk

Marcelo Samsoniuk

@samsoniuk -

Tom Verbeure

Tom Verbeure

@tom_verbeure -

Hans Baier @[email protected]

Hans Baier @[email protected]

@hansfbaier -

EfinixInc

EfinixInc

@efinixinc

Something went wrong.

Something went wrong.