#gpuprogramming نتائج البحث

⚡ Built my own graphics engine: Asthrarisine Sounds fun? Reality = invisible meshes, memory bugs & shader headaches. But here’s what made it work: #OpenGL #GraphicsEngine #GPUProgramming #GLTF #GameDev #ShaderProgramming

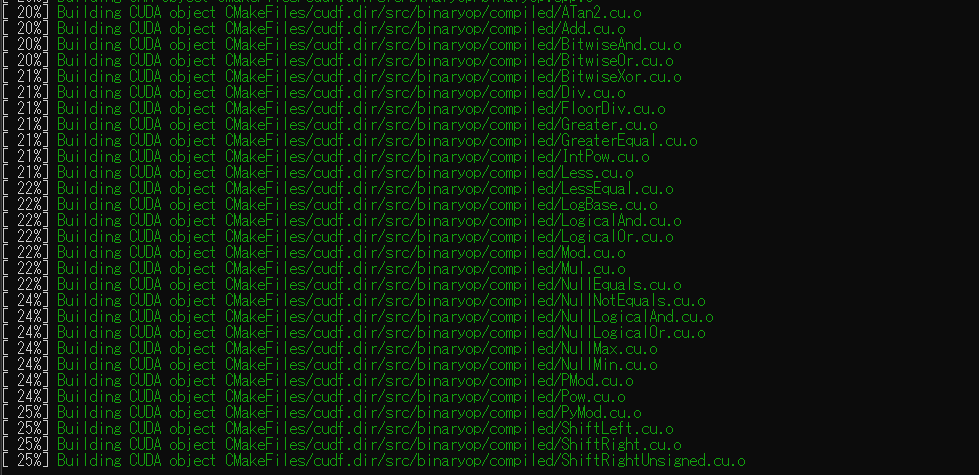

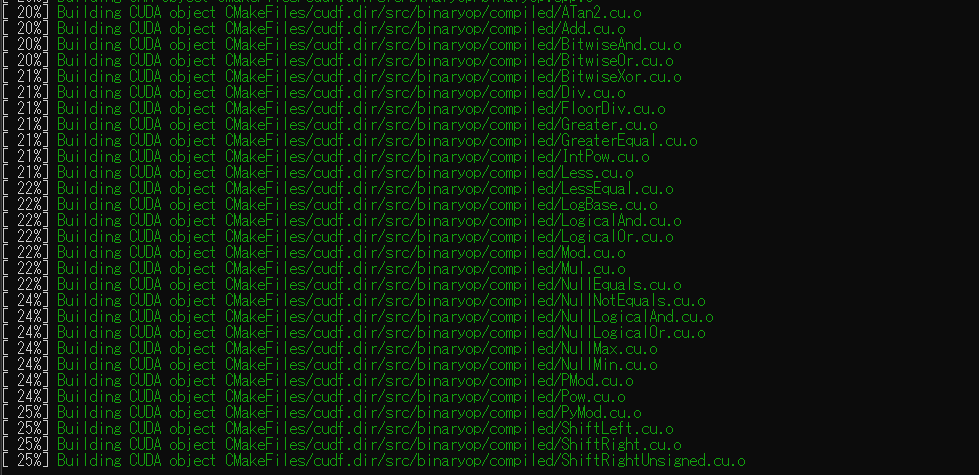

Each common operation is implemented as its own .cu file—modular. intriguing. #CUDA #NVIDIA #GPUProgramming #libcudf

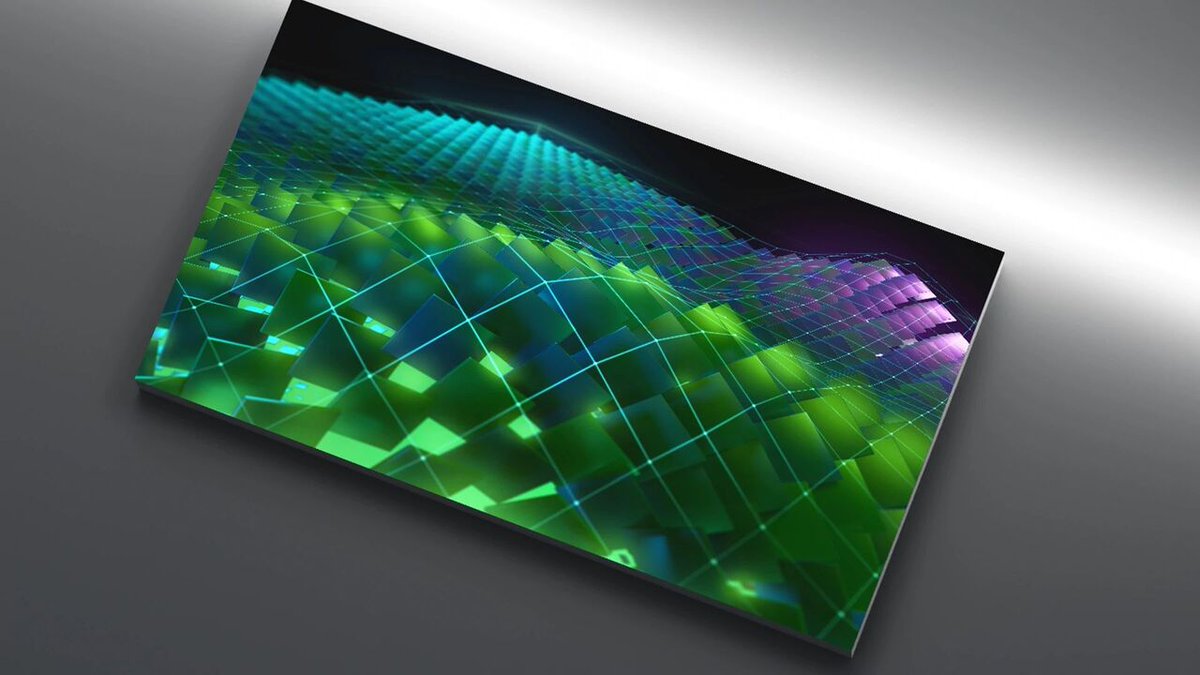

CPU rendering vs. GPU rendering youtu.be/FFQQNvSaIFI?si… #gpu #gpuprogramming #nvidia #intel #amd #parallelprocessing #cuda #computergraphics #graphics #dataviz #compute #hpc #rendering #cpu #render #cudaeducation

youtube.com

YouTube

Terrain & Ocean Rendering Using CUDA

"Need better CUDA textbooks. 'Programming Massively Parallel Processors' is a good intro. I've created C/CUDA C implementations for first 3 chapters. Check book & my GitHub repo for details. #CUDA #GPUprogramming"

"10 days into CUDA, and I’ve earned my first badge of honor! 🚀 From simple kernels to profiling, every day is a step closer to mastering GPU computing. Onward to 100! #CUDA #GPUProgramming #100DaysOfCUDA"

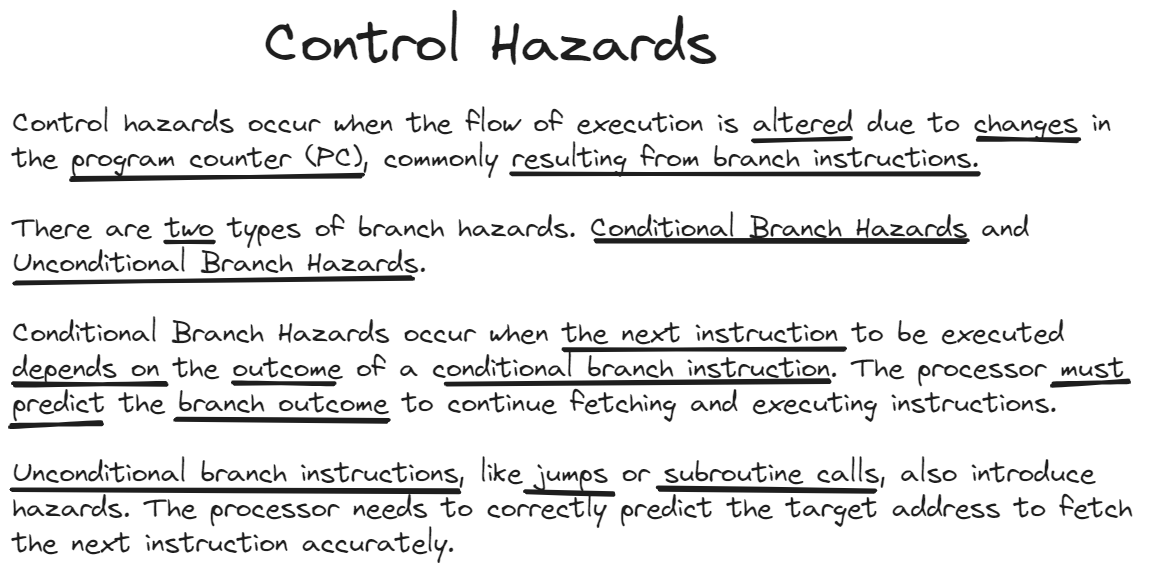

#GPUProgramming - Day 07: 🔧 #CPU Hazards 101 🚧: Ever heard of #Register Renaming & Out-of-Order Execution? They tackle structural hazards, ensuring smooth sailing for instructions. Watch out for Data Hazards (#RAW, #WAR, #WAW) in #MIPS, but fear not! #COA #LearnInPublic

#GPUProgramming - Day 02: 🔄 Exploring CPU architectures! #RISC, like #ARM & #Power, opts for efficiency with many registers. #CISC, exemplified by #Intel 8086, prioritizes simplicity, offering diverse, complex instructions. RISC excels in energy efficiency. #COA #LearnInPublic

#GPUProgramming - Day 03: 🧠 CPUs: Processors adapt with DISA. #CPU's core duo - Control Unit & Datapath. Datapath: Registers, ALU, Buses, Multiplexers – a data symphony! 🔄 Follow the Instruction Execution Cycle: Fetch ➡️Decode➡️Execute➡️Store➡️ Update PC. 🕹️ #LearnInPublic

#GPUProgramming - Day 01: 🚀 Exploring RISC architecture: Simplified, optimized instructions in one clock cycle. 🔄 Bye, CISC complexity! 🏎️ Registers rule, boosting speed. 🤖💡 Compiler-friendly design, slick pipelining for simultaneous processing! 🕵️♂️ #COA #RISC #LearnInPublic

For maximum performance, firms often develop custom CUDA kernels. This involves writing low-level code to directly program the GPU's parallel cores, squeezing out every drop of efficiency for critical tasks. #CUDA #GPUProgramming

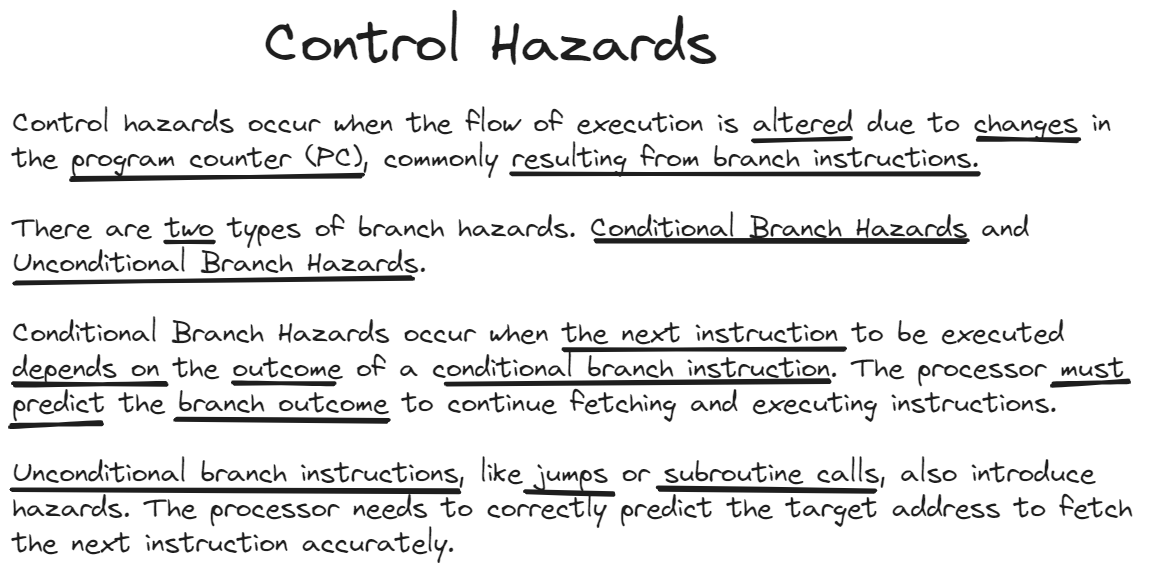

#GPUProgramming - Day 08: 🚀 Explored #computerarchitecture today! 🖥️ Control Hazards tackle branch prediction, #Pentium FDIV bug a classic example. 💡 Memory #Hierarchy is key—#RAM, #cache levels (L1, L2, L3), and storage devices play crucial roles. 🔄🌐 #Memory #LearnInPublic

#GPUProgramming - Day 06: 🔍 Diving into computer architecture! 🖥️ Structural hazards arise when hardware resources are in high demand, causing contention among instructions. Data hazards? RAW, WAR, WAW – the battle for data paths and registers! 💡 #COA #LearnInPublic

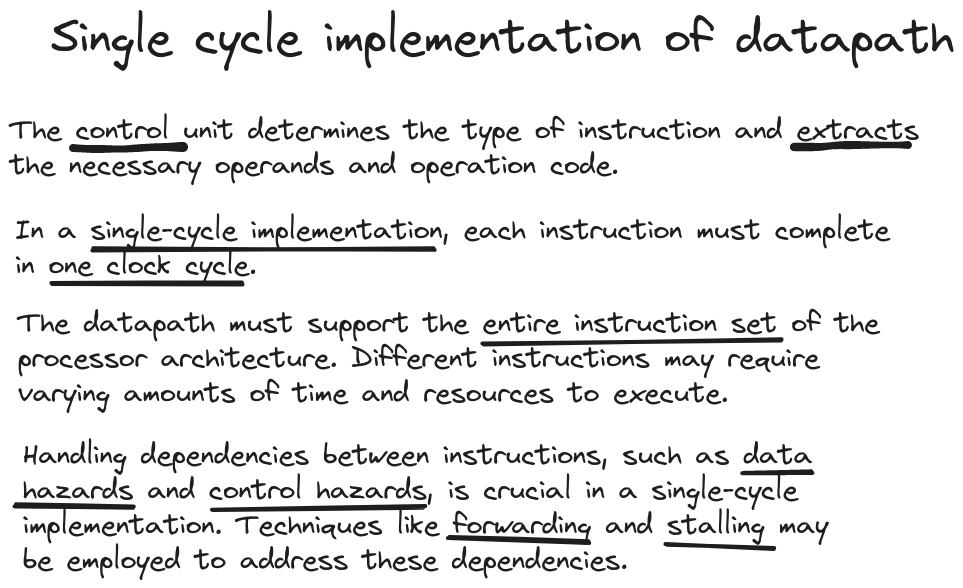

#GPUProgramming - Day 04: 🕰️ Dive into processor architectures! 🧠 Single-cycle execution, one clock cycle per instruction, demands a versatile datapath. 🔄 Multi-cycle instructions break it down for a more intricate dance with time. ⏳ #ComputerArchitecture #LearnInPublic 🚀

$AMD will train 100,000 STEM graduates in open-source GPU programming and grant 100,000 hours of free cloud access to Indian researchers and startups: ibn.fm/o5GJF #OpenSource #GPUProgramming #AIIndia

opensourceforu.com

AMD Expands Open Source GPU Programming In India With 100,000 Graduate Training And Free Cloud...

AMD will train 100,000 graduates in open source GPU programming and offer 100,000 hours of free cloud access in India, aiming to democratise AI development

#GPUProgramming - Day 05: 🚀 Pipelining in computer architecture boosts performance by dividing instruction execution into stages. Techniques like forwarding, branch prediction, and superscalar processors enhance parallelism.💻🌐 #ComputerArchitecture #Pipelining #LearnInPublic

🚀 Exciting Learning Opportunity! 🚀 For more details and registration: events.eurocc.lu/meluxina-intro… #GPUProgramming #CUDA #Supercomputing #ScientificComputing #MeluXina #Luxembourg

📣 Save the date. Join Dr. Wen-mei Hwu & Dr. Izzat El Hajj on May 28, 2025, at 10:00 AM PDT for a 1-hour webinar on teaching and accelerating #CUDA. Get insider tips, book updates, and expert advice. Register now ➡️ #CUDA #GPUProgramming #TechWebinar bit.ly/3YRAhOI

#NewBooks Gerassimos Barlas #Multicore and #GPUprogramming: An Integrated Approach 2nd Edition Morgan Kaufmann (August 2022) Blurb: "offers broad coverage of key parallel computing tools, essential for multi-core CPU programming and many-core "massively parallel" computing. >

#DataParallel #GPUProgramming and revolutionize the way you code! 💪 Want to learn more? Check out this book! 👉 [Amazon link] Hey @elonmusk, have you explored the potential of GPU programming in your space endeavors? 🚀🪐 Curious to hear your thoughts! #tech #innovation Hey…

RAY TRACING PROGRAMMING | Shader Binding Table | youtu.be/LtJBt84tn6Y #computergraphics #gpuprogramming #vulkan #vulkanapi #hpc #raytracing #graphics #visualarts #photoshop #shaderbindingtable #rtx #nvidia #amd #intel #cudaeducation

youtube.com

YouTube

VULKAN API DISCUSSION | Ray Tracing 4.2 | Shader Binding Table...

CPU rendering vs. GPU rendering youtu.be/FFQQNvSaIFI?si… #gpu #gpuprogramming #nvidia #intel #amd #parallelprocessing #cuda #computergraphics #graphics #dataviz #compute #hpc #rendering #cpu #render #cudaeducation

youtube.com

YouTube

Terrain & Ocean Rendering Using CUDA

RAY TRACING PROGRAMMING | Shader Binding Table | youtu.be/LtJBt84tn6Y #computergraphics #gpuprogramming #vulkan #vulkanapi #hpc #raytracing #graphics #visualarts #photoshop #shaderbindingtable #rtx #nvidia #amd #intel #cudaeducation

youtube.com

YouTube

VULKAN API DISCUSSION | Ray Tracing 4.2 | Shader Binding Table...

@nvidia GPU bootcamp in the Claustro of @URosario. @HPCCol growing stronger. #HPC #GPUProgramming #OpenACC

Each common operation is implemented as its own .cu file—modular. intriguing. #CUDA #NVIDIA #GPUProgramming #libcudf

Compilation errors when using OpenACC with g++ 10 stackoverflow.com/questions/6542… #openacc #gpuprogramming #g++ #compilererrors #cpp

"Need better CUDA textbooks. 'Programming Massively Parallel Processors' is a good intro. I've created C/CUDA C implementations for first 3 chapters. Check book & my GitHub repo for details. #CUDA #GPUprogramming"

#GPUProgramming - Day 07: 🔧 #CPU Hazards 101 🚧: Ever heard of #Register Renaming & Out-of-Order Execution? They tackle structural hazards, ensuring smooth sailing for instructions. Watch out for Data Hazards (#RAW, #WAR, #WAW) in #MIPS, but fear not! #COA #LearnInPublic

And this was day 3 of the DL & #GPUprogramming course @LRZ_DE @HLRS_HPC @Uni_Stuttgart @NVIDIAAI DLI, with the grande finale: we learnt how to employ distributed stoch. gradient descent w/ multi-GPU, @TensorFlow & #Horovod @UberAILabs @LFAIDataFdn🎉😍highly recommended course!

#GPUProgramming - Day 02: 🔄 Exploring CPU architectures! #RISC, like #ARM & #Power, opts for efficiency with many registers. #CISC, exemplified by #Intel 8086, prioritizes simplicity, offering diverse, complex instructions. RISC excels in energy efficiency. #COA #LearnInPublic

#GPUProgramming - Day 03: 🧠 CPUs: Processors adapt with DISA. #CPU's core duo - Control Unit & Datapath. Datapath: Registers, ALU, Buses, Multiplexers – a data symphony! 🔄 Follow the Instruction Execution Cycle: Fetch ➡️Decode➡️Execute➡️Store➡️ Update PC. 🕹️ #LearnInPublic

#GPUProgramming - Day 01: 🚀 Exploring RISC architecture: Simplified, optimized instructions in one clock cycle. 🔄 Bye, CISC complexity! 🏎️ Registers rule, boosting speed. 🤖💡 Compiler-friendly design, slick pipelining for simultaneous processing! 🕵️♂️ #COA #RISC #LearnInPublic

NSIGHT GRAPHICS TUTORIAL: amzn.to/2Qffvpl | Vulkan, OpenGL, Direct 3D profiling and debugging | #graphicsprogramming #gpuprogramming #gpgpu #howtoprogram #howtocode #computerprogramming #howtowriteaprogram #siliconvalley #nsightgraphicstutorial #videowalkthrough

#GPUProgramming - Day 08: 🚀 Explored #computerarchitecture today! 🖥️ Control Hazards tackle branch prediction, #Pentium FDIV bug a classic example. 💡 Memory #Hierarchy is key—#RAM, #cache levels (L1, L2, L3), and storage devices play crucial roles. 🔄🌐 #Memory #LearnInPublic

#GPUProgramming - Day 04: 🕰️ Dive into processor architectures! 🧠 Single-cycle execution, one clock cycle per instruction, demands a versatile datapath. 🔄 Multi-cycle instructions break it down for a more intricate dance with time. ⏳ #ComputerArchitecture #LearnInPublic 🚀

#GPUProgramming - Day 05: 🚀 Pipelining in computer architecture boosts performance by dividing instruction execution into stages. Techniques like forwarding, branch prediction, and superscalar processors enhance parallelism.💻🌐 #ComputerArchitecture #Pipelining #LearnInPublic

#GPUProgramming - Day 06: 🔍 Diving into computer architecture! 🖥️ Structural hazards arise when hardware resources are in high demand, causing contention among instructions. Data hazards? RAW, WAR, WAW – the battle for data paths and registers! 💡 #COA #LearnInPublic

"10 days into CUDA, and I’ve earned my first badge of honor! 🚀 From simple kernels to profiling, every day is a step closer to mastering GPU computing. Onward to 100! #CUDA #GPUProgramming #100DaysOfCUDA"

VULKAN VALIDATION LAYERS TUTORIAL: amzn.to/38I5uY6 | the most efficient way to learn about vulkan validation layers on the internet. | video walkthrough (133 min) | #computergraphicsapi #opengl #gpuprogramming #framerate #graphicsrendering #dataviz #computersimulation

New to GPU programming? Want to boost your NVIDIA CUDA efficiency? Check out this must-read blog post for essential techniques and expert tips! Get ready to unleash the full power of NVIDIA GPUs. #GPUprogramming #NVIDIA #CUDAefficiency ift.tt/6eYjOno

🚀 Exciting Learning Opportunity! 🚀 For more details and registration: events.eurocc.lu/meluxina-intro… #GPUProgramming #CUDA #Supercomputing #ScientificComputing #MeluXina #Luxembourg

Working on one of my last projects before graduating: a position based dynamics cloth simulator plugin for Unity parallelized on the GPU using compute shaders. Hoping to put it on the Asset store for free! @AssetStore @pjcozzi @shehzanm #Unity #AssetStore #GPUProgramming

Something went wrong.

Something went wrong.

United States Trends

- 1. #LoveYourW2025 83.6K posts

- 2. Good Wednesday 19.7K posts

- 3. #Worlds2025 54.8K posts

- 4. Raila 207K posts

- 5. #LeeKnowXGucci 4,897 posts

- 6. And the Word 77.1K posts

- 7. LEE KNOW FOR HARPERS BAZAAR 4,320 posts

- 8. Hump Day 7,086 posts

- 9. #Wordle1579 N/A

- 10. #100T N/A

- 11. Baba 123K posts

- 12. Young Republicans 86.2K posts

- 13. Tami 4,989 posts

- 14. Yamamoto 51.1K posts

- 15. Lucia 60.9K posts

- 16. Vishnu 9,237 posts

- 17. halsey 9,991 posts

- 18. George Floyd 36.6K posts

- 19. Politico 328K posts

- 20. Burl Ives 1,804 posts